Method for testing field programmable gate array (FPGA) single-long line slant switches

A test method and a single long-line technology, applied in the direction of circuit breaker testing, measuring electricity, measuring devices, etc., can solve problems such as unfavorable fault location, long interconnection levels of wiring resources, and no detection means proposed, so as to achieve user-friendly operation , Accurate fault location, and the effect of simplifying the test process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

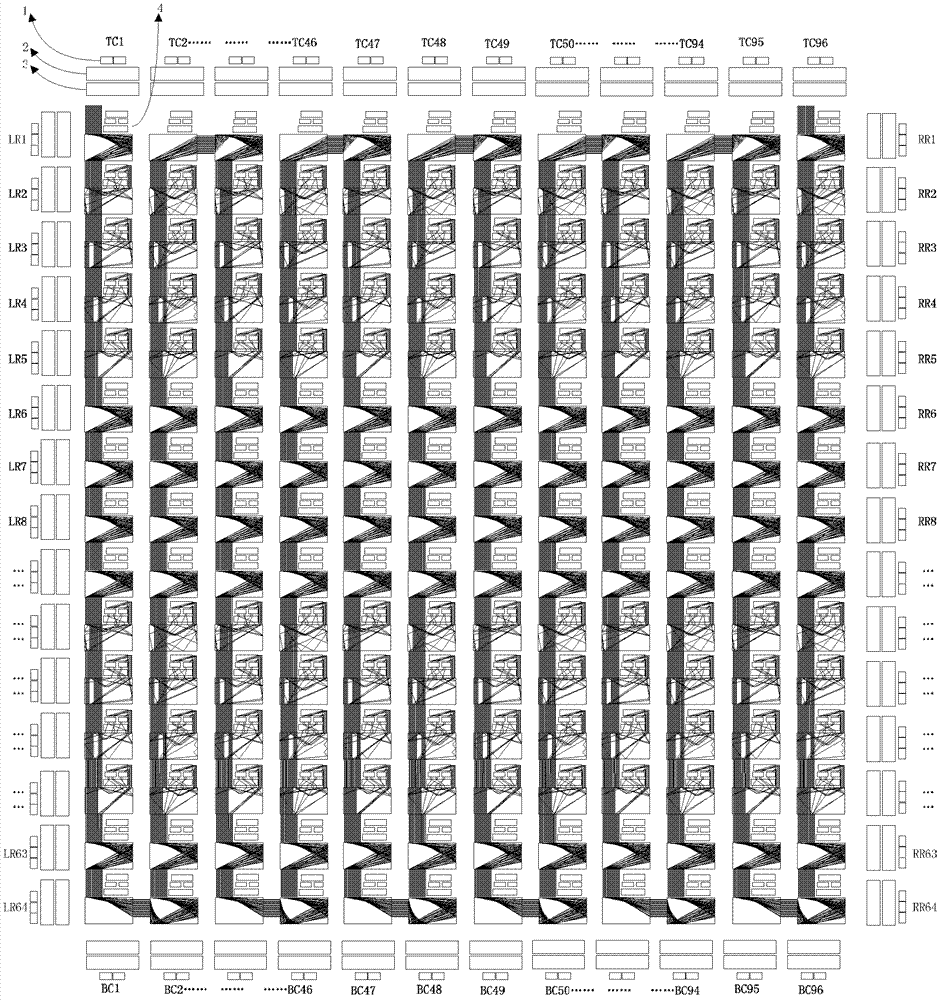

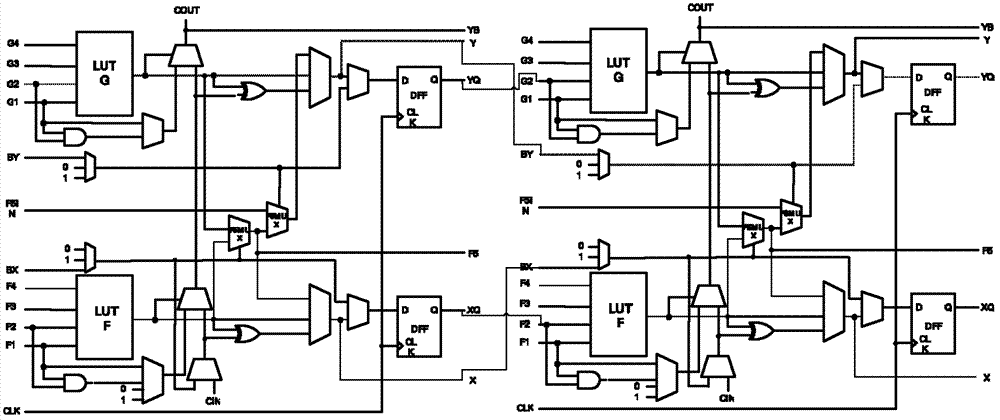

[0036] The present invention will be further described below in conjunction with drawings and embodiments. The implementation object of this test method is based on Xilinx company Virtex TM Any FPGA for system architecture. FPGAs based on this architecture usually include: embedded block memory (Blockram), programmable input / output unit (Input / Output Block, IOB), a large number of programmable logic units (Configurable Logic Block, CLB) and programmable interconnect resources, classic Symmetrical FPGA interconnection resources include interconnection switch box (Switch Box, SB), input switch box (Input Mux, IMUX), output switch box (Output Mux, OMUX), IOB module switch box, and interconnection segment (specifically including Single long line, six long lines, long line, tri-state bus and other resources).

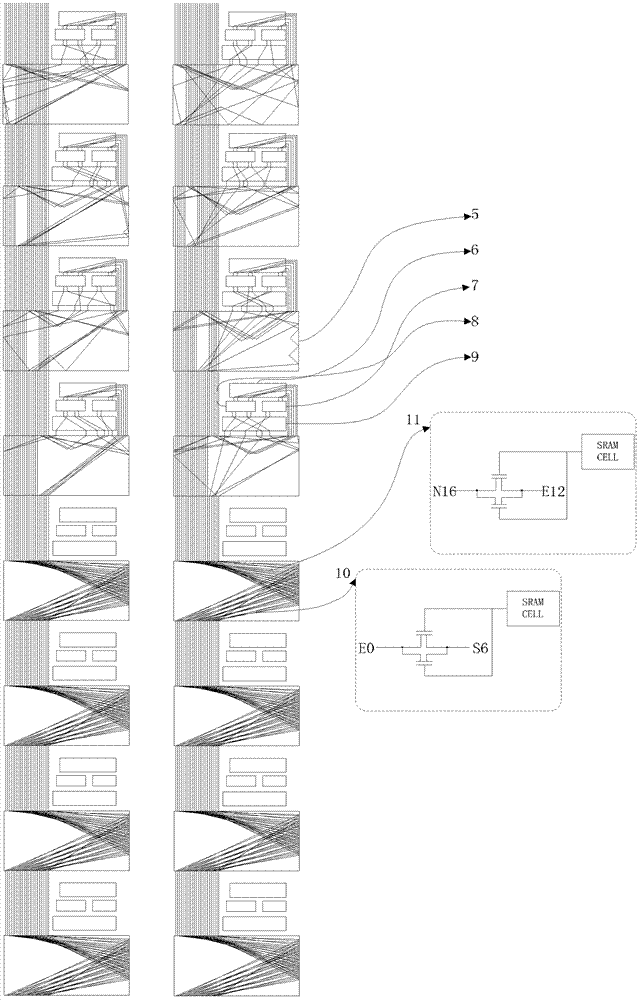

[0037] figure 1 , 2 shown for Xilinx Virtex-based TMSchematic diagram of the FPGA logic structure of the system architecture, including: IOB1, IOB input switch box 2, IO...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More