Decomposed circuit interconnection testing method based on boundary scanning technology

A boundary scan and circuit interconnection technology, which is applied in the direction of electronic circuit testing, electrical measurement, measuring devices, etc., can solve the problem of low accuracy of fault diagnosis, achieve improved reliability and feasibility, reduce difficulty, and achieve high accuracy Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

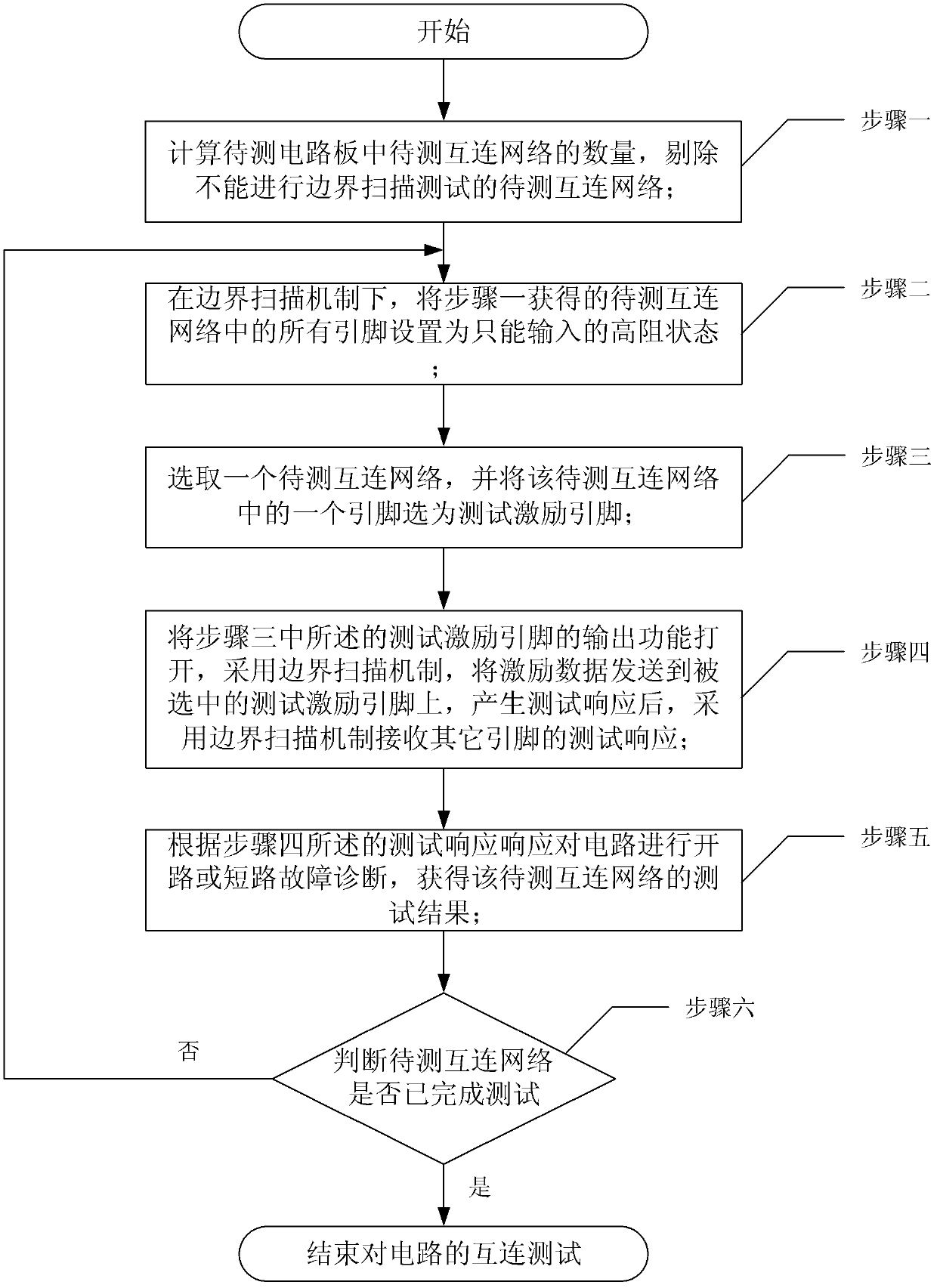

[0015] Specific implementation mode 1. Combination figure 1 Illustrate this specific embodiment, a kind of decomposed circuit interconnection test method based on boundary scan technology, it is realized by the following steps:

[0016] Step 1, calculating the number of interconnection networks to be tested in the circuit board to be tested, and eliminating the interconnection networks to be tested that cannot be tested by boundary scan;

[0017] Step 2. Under the boundary scan mechanism, set all pins in the interconnection network to be tested obtained in step 1 to a high-impedance state that can only be input;

[0018] Step 3, select an interconnection network to be tested, and select a pin in the interconnection network to be tested as a test excitation pin, and generate data '1' or '0';

[0019] Step 4. Turn on the output function of the test stimulus pin described in step 3, and use the boundary scan mechanism to send the stimulus data to the selected test stimulus pin. ...

specific Embodiment approach 2

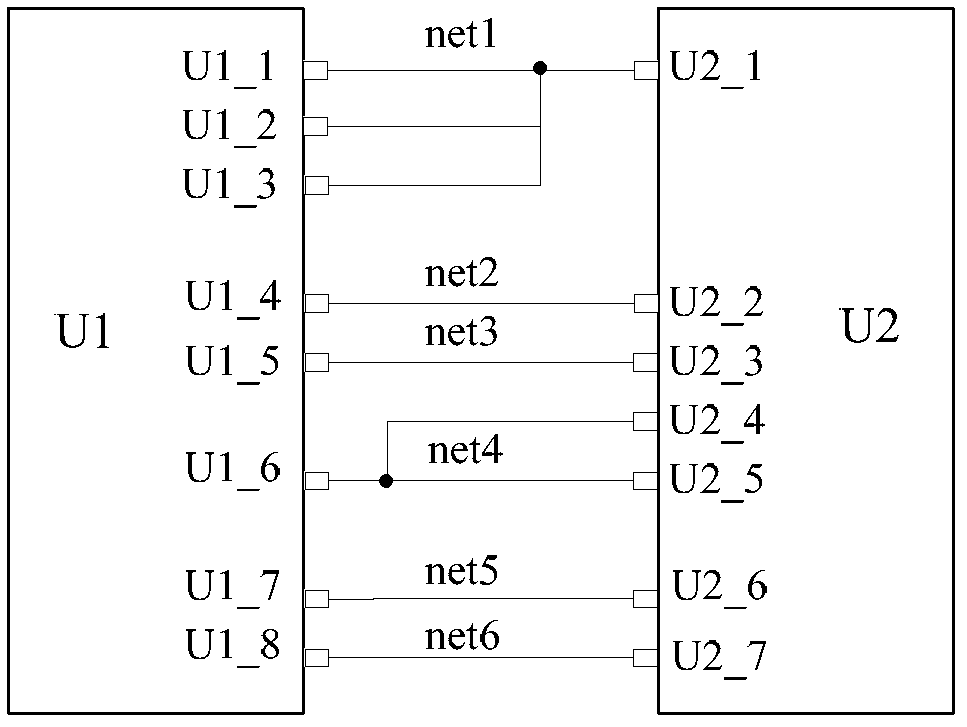

[0024] Specific Embodiment 2. In this specific embodiment, a circuit interconnection is taken as an example to describe the method of the present invention; figure 2 As shown, the interconnected chips are U1 and U2, and there are 6 measurable interconnection networks: net1 to net6. The specific test process is as follows:

[0025] Step 1, calculating the number of interconnection networks to be tested in the circuit board to be tested, and eliminating the interconnection networks to be tested that cannot be tested by boundary scan;

[0026] Specifically: According to the circuit schematic file (.net file), find the interconnection network in the circuit, and remove the network that cannot be controlled by the boundary scan mechanism, and the remaining network number is the total number of measurable networks.

[0027] Step 2. Under the boundary scan mechanism, set all the pins in the interconnection network to be tested that are eliminated in step 1 to a high-impedance state ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More