Microcontrollers with Special Grouped Instructions

A microcontroller and instruction technology, applied in instruction analysis, program control design, instruments, etc., can solve the problem of disconnected data memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

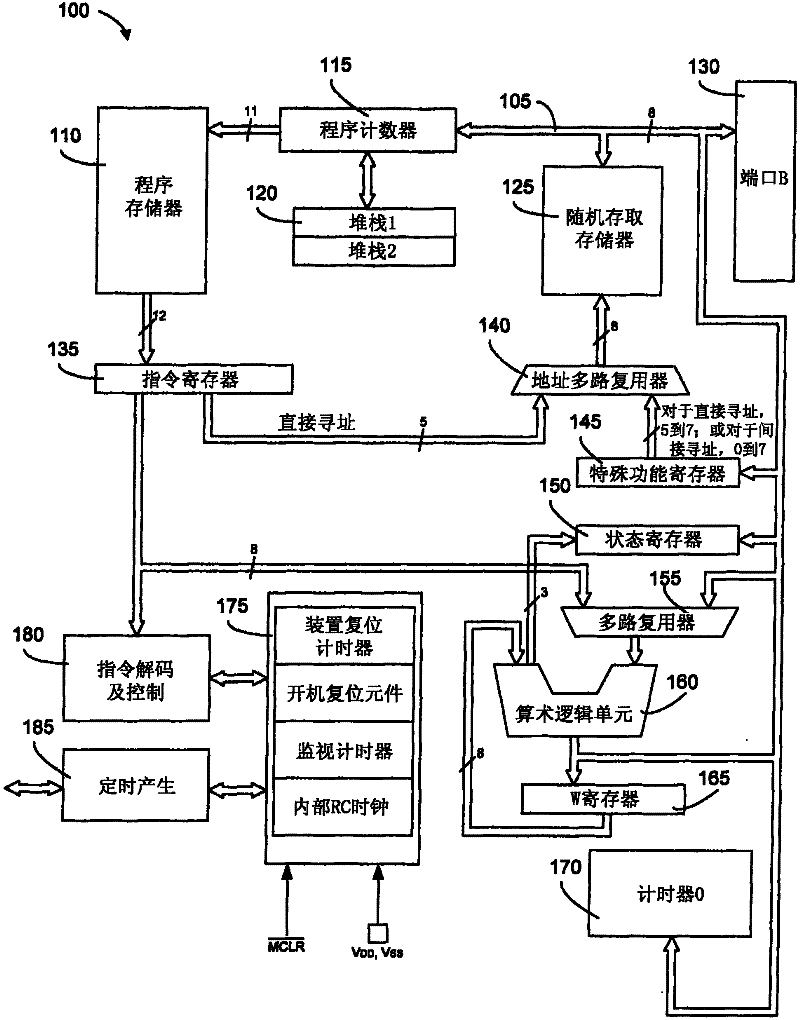

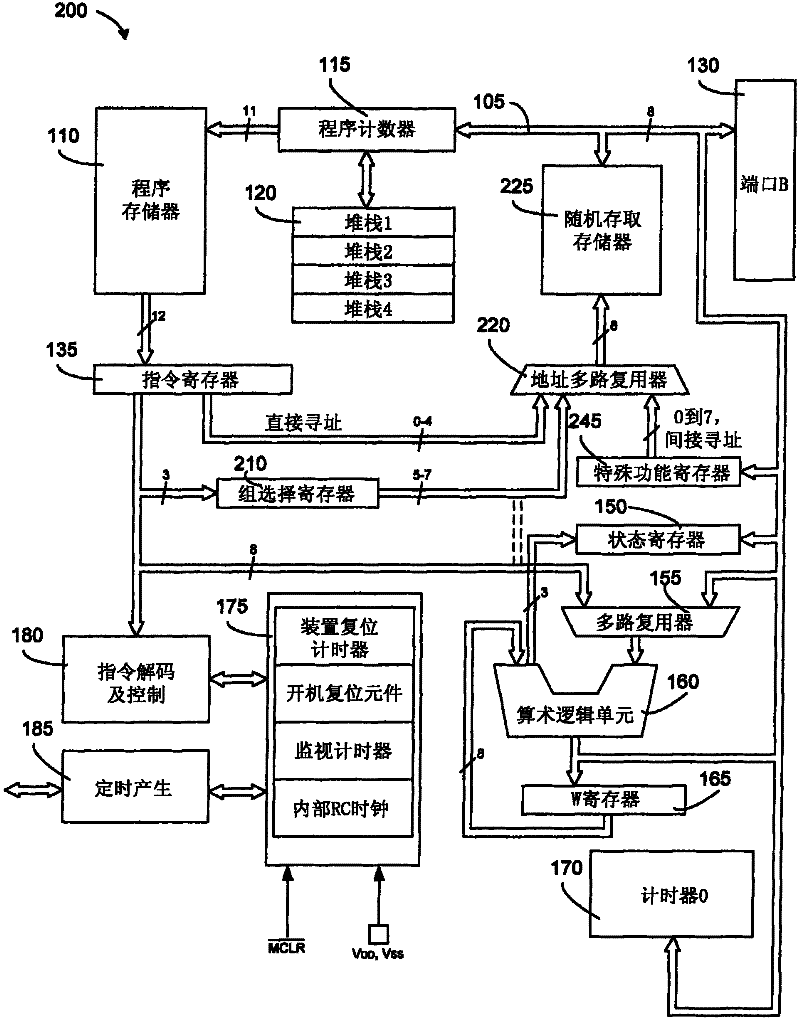

Embodiment Construction

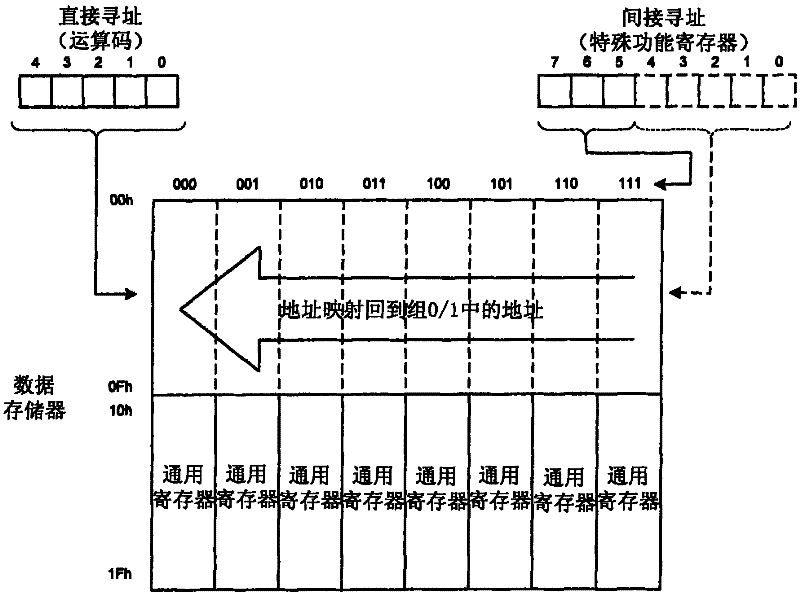

[0031] In accordance with the teachings of the present invention, a non-memory mapped bank select register (BSR) is provided for selecting one of a plurality of memory banks for direct addressing. Memory-mapped registers are used for indirect addressing independent of the selected memory bank. The addition of specialized grouping instructions (e.g., "move literal into BSR register (MOVLB)") allows all data bytes in a bank of memory to be used for general purpose data, and thus, allows strides that do not contain any mapped special functions Contiguous addressing of multiple memory banks of registers. Therefore, the BSR registers that select the active memory bank are not mapped in the data registers, but may be accessed with specialized commands.

[0032] Therefore, multiple memory banks are available that do not have or require special registers. This allows indirect addressing of adjacent banks of memory via indirect addressing registers (FSRs) without having to worry abou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More