Dynamic allocation method for instruction memory cell for multi-core heterogeneous system

An instruction storage, heterogeneous system technology, applied in memory systems, program control design, instruments, etc., can solve problems such as insufficient loading

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] A preferred embodiment of the present invention is described in detail as follows in conjunction with accompanying drawing:

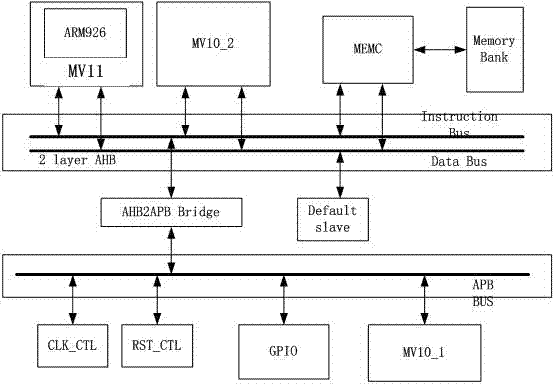

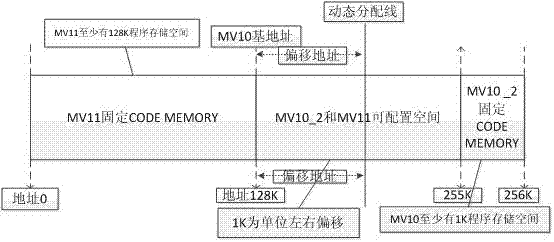

[0048] The method for dynamically allocating instruction storage units of this multi-core heterogeneous system, configures a special function register through the programming of the main control processor of the system, so that an offset address is added to the instruction addressing of the non-master control processor, and adopts the following workflow (see figure 1 ) to realize the dynamic allocation of multi-core heterogeneous system instruction storage units:

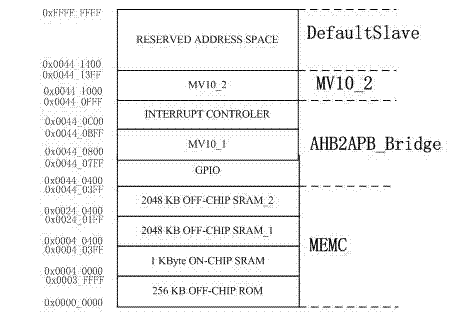

[0049] 1. In the MV12 system, the ARM processor is responsible for the program memory configuration (mapping), and the MV10_2 follows the hardware configuration (mapping).

[0050] 2. MV12 is unified addressing for MV10_2 MCU, MV10_1 MCU and other modules.

[0051] 3. MV11 programming (you can choose whether to remap the instruction memory unit of MV10_2 at the beginning of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More