Method for accelerating analysis and optimization of physical layout of integrated circuit

An integrated circuit and physical technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of slow data processing speed and long time consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

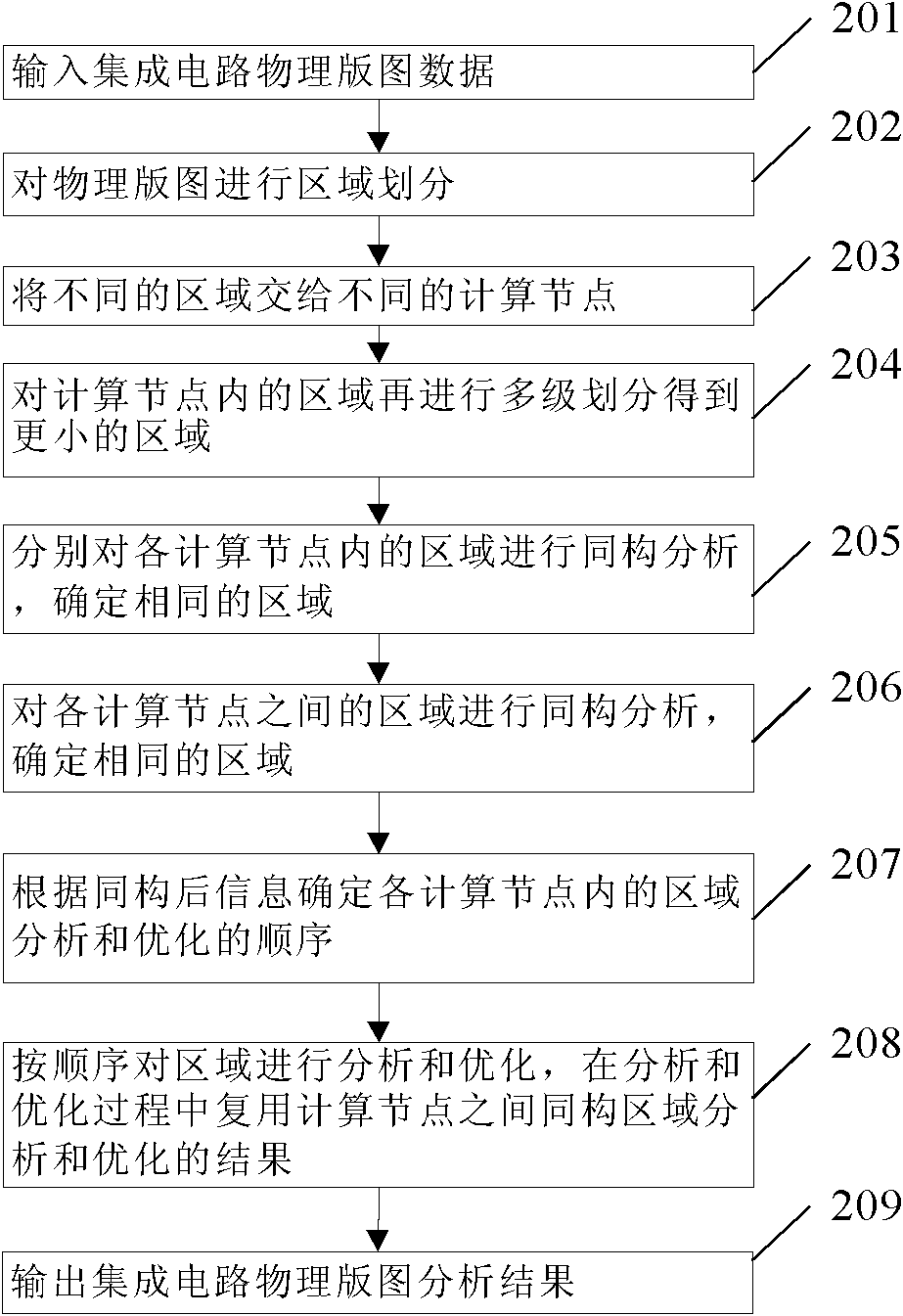

[0037] The technical solutions of the present invention will be further described below in conjunction with the accompanying drawings and embodiments.

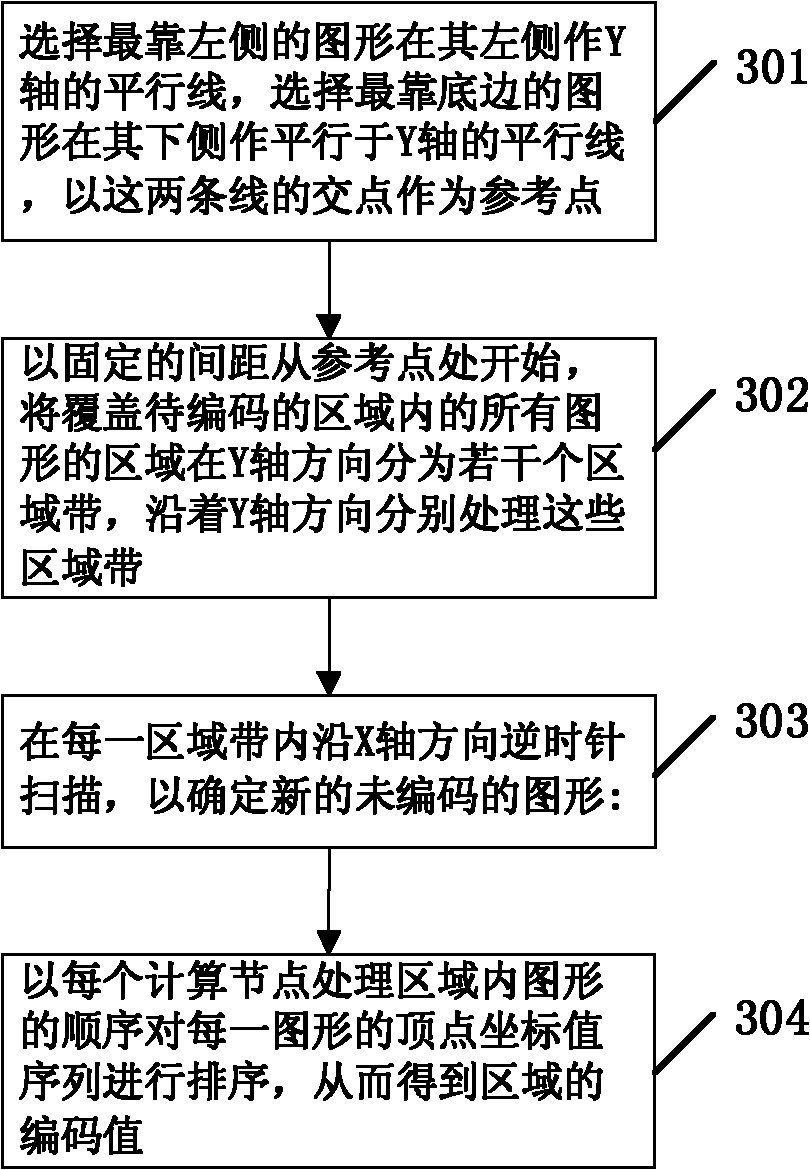

[0038] The present invention divides the physical layout by using a multi-level region segmentation algorithm, and reuses the calculation results by using the region isomorphism algorithm. The multi-level reduction of the calculation scale and the multiplexing of the calculation results greatly accelerate the analysis and optimization speed of massive physical layouts.

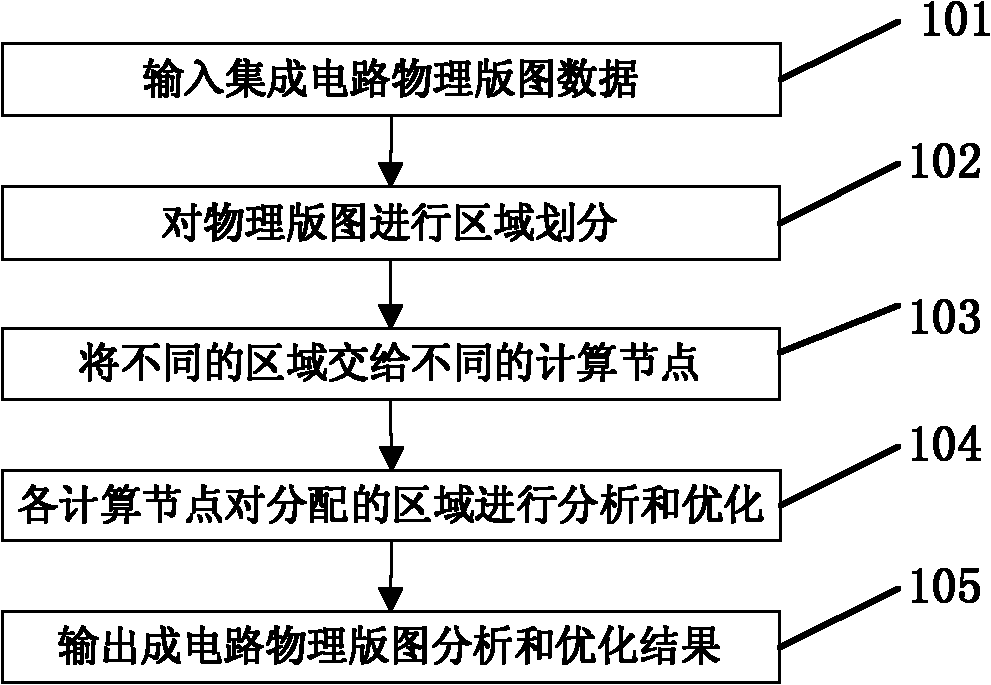

[0039] see figure 2 , the method for analyzing and optimizing the physical layout of the integrated circuit in the embodiment of the present invention is as follows:

[0040] Step 201: Input the physical layout data of the integrated circuit; that is, input the physical layout data to be analyzed and processed into the computer.

[0041] Step 202: Divide the physical layout into regions; the division is by using a multi-level region segmentation algorithm. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More