Control system and method for controlling output clocks of different PLLs in a processor

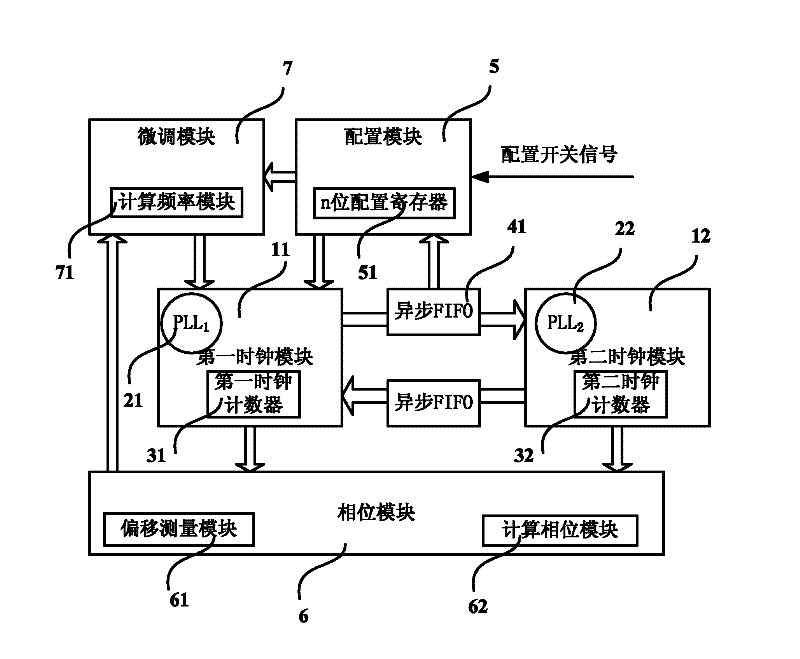

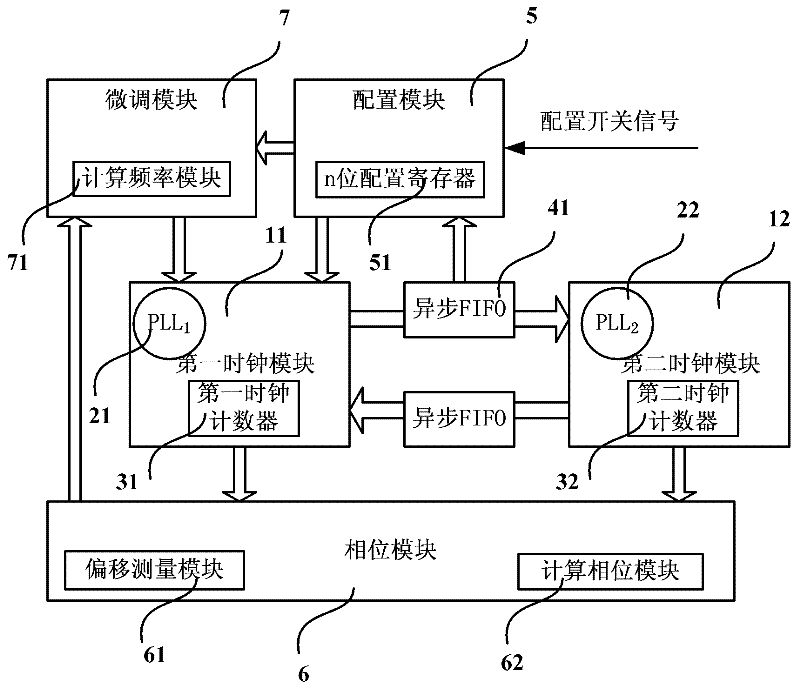

A technology for outputting clocks and control systems, which is applied in the field of control systems for controlling the output clocks of different phase-locked loops, and can solve the problems of no corresponding relationship and no connection between clock signals, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

[0064] The configuration module 5 configures the frequency ratio between at least two clocks to obtain the optimal frequency ratio, as an implementable manner, including the following steps:

[0065] Step S110, the configuration module receives the configuration switch signal sent from the outside, and starts to configure the frequency ratio r;

[0066] As a possible implementation, the clock of the first clock module 11 is faster than the clock of the second clock module 12. When the configuration module 5 receives the configuration switch signal as 1, it starts to configure the frequency ratio, which randomly configures a frequency ratio. r, and output the frequency ratio r to the first clock module 11.

[0067] It should be noted that, in the embodiment of the present invention, a clock module with a fast clock is used as the first clock module 11, but a clock module with a fast clock can also be used as the second clock module 12, then the following embodiments relate to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More