Method and device for realizing data pre-fetching

A prefetch and prefetcher technology, applied in electrical digital data processing, instruments, sustainable buildings, etc., can solve the problem of wasting processor access to on-chip cache bandwidth and power consumption, low storage utilization efficiency, and inability to determine whether the prefetch address is For problems such as addresses that have been prefetched, it can improve storage utilization efficiency, optimize performance, and reduce bandwidth requirements and power consumption overhead.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] The technical solutions of the present invention will be described in detail below in conjunction with the accompanying drawings and preferred embodiments. It should be understood that the embodiments described below are only used to illustrate and explain the present invention, and are not intended to limit the technical solution of the present invention.

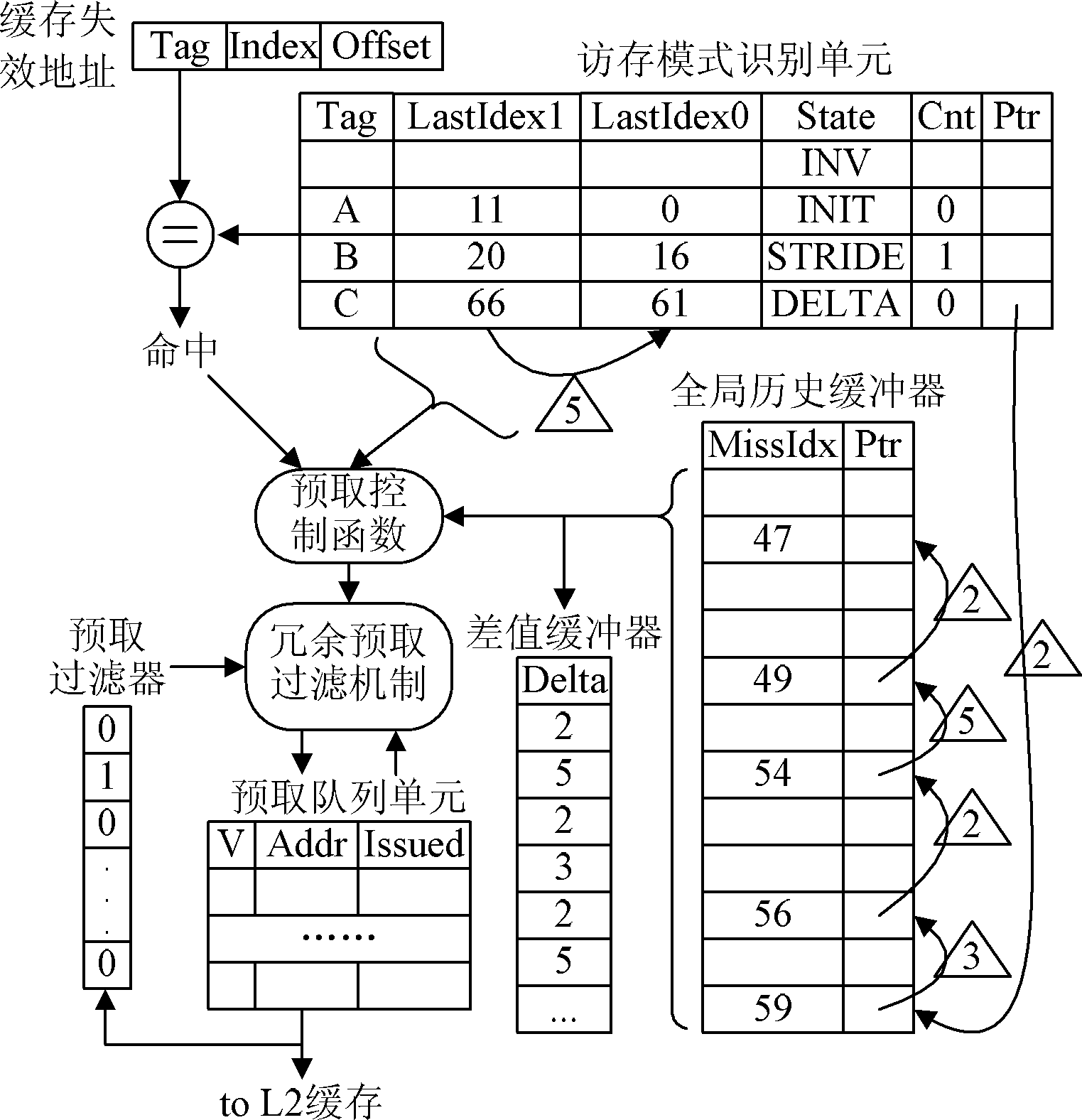

[0053] Such as figure 1 As shown, the internal structure of the embodiment of the prefetcher device for realizing data prefetching of the present invention is represented, including the memory access pattern recognition unit, wherein:

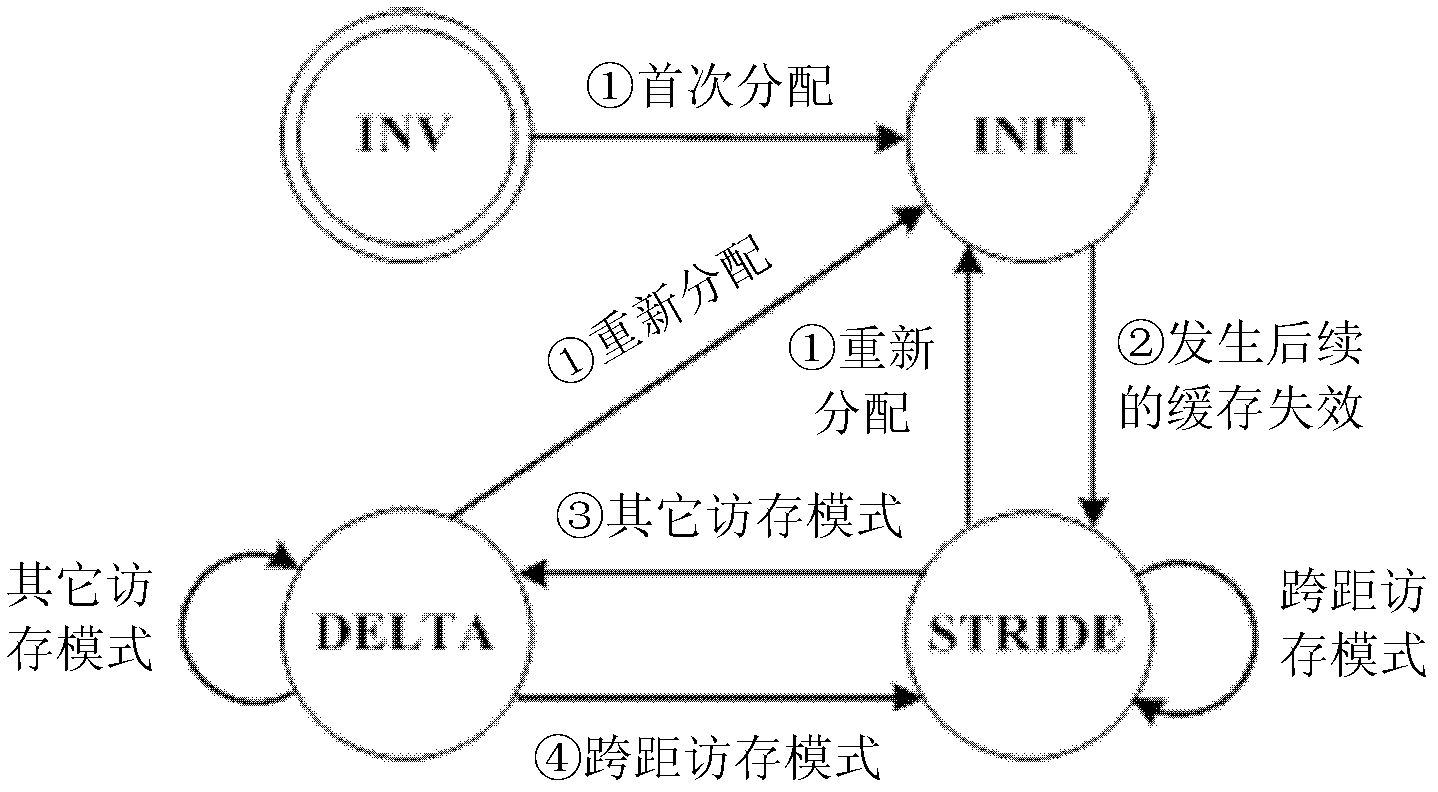

[0054] The memory access pattern recognition unit is used to divide the global invalidation address stream into local invalidation address streams, record the address information of the two most recent cache failures in the local invalidation address stream as historical memory access information in chronological order, and according to the Records capture stride fetch patterns and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More