FPGA/CPLD (Field Programmable Gate Array/Complex Programmable Logic Device)-based program downloader

A program download and device technology, applied in the field of programming tools, can solve the problems of inconvenient portability, complex hardware circuits, and high cost, and achieve the effects of compactness, flexibility, simplified hardware circuits, and enhanced stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

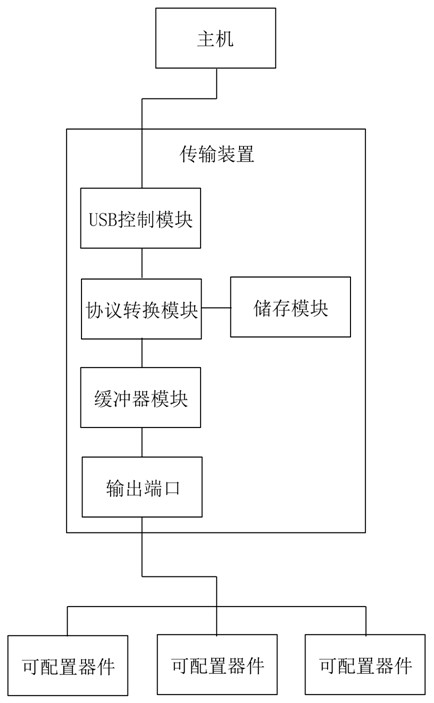

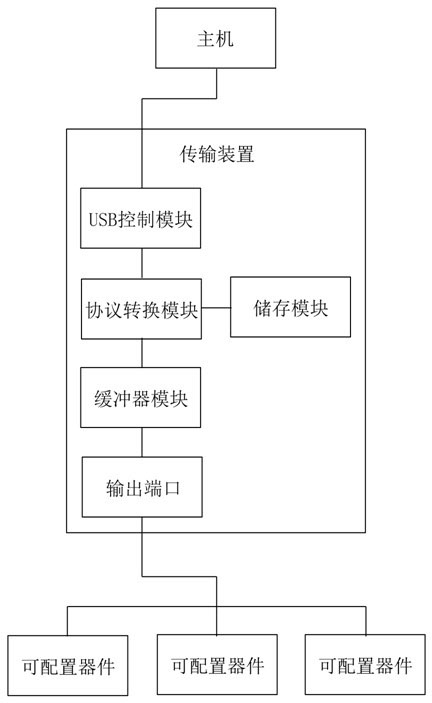

[0025] like figure 1 As shown, a program downloader based on FPGA / CPLD of the present invention includes a host, a transmission device and a configurable device that constructs a hardware structure by programming, and the transmission device is connected to the host and the configurable device that constructs a hardware structure by programming , wherein the transmission device includes a USB control module, a protocol conversion module, a buffer module and an output port; the USB control module is connected to the USB interface of the host, the protocol conversion module is connected to the USB control module, the buffer module is connected to the protocol conversion module, and the protocol The conversion module is connected to the output port, and the output port is connected to the input por...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More