Multi-core simulation parallel accelerating method based on sampling

A multi-core, sampling strategy technology, applied in software simulation/interpretation/simulation, program control devices, etc., can solve problems such as unfavorable simulation, multi-time cost, acceleration, etc., and achieve a large simulation speed effect

Active Publication Date: 2013-04-17

SHENZHEN INST OF ADVANCED TECH CHINESE ACAD OF SCI

View PDF3 Cites 10 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

The sampling strategies cited above all have a common defect, that is, it is necessary to determine the parameters in the sampling strategy through static analysis or tentative simulation, such as the size of instruction sample fragments, etc., and static analysis or tentative simulation requires more cost time cost, and when the simulated micro-architecture changes, it is necessary to re-perform static analysis or trial simulation, duplication of labor, which is not conducive to the acceleration of simulation

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment

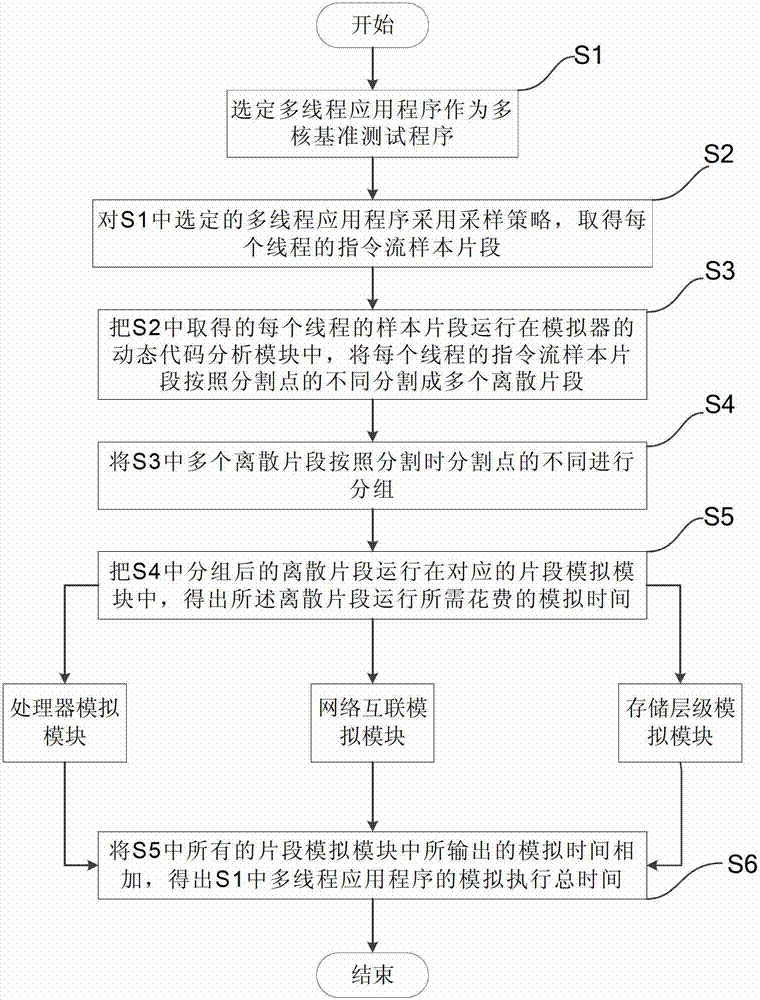

[0034] Such as figure 1 As shown, a sampling-based multi-core simulation parallel acceleration method provided in this embodiment includes:

[0035] S1: selected multi-thread application program as multi-core benchmark test program;

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

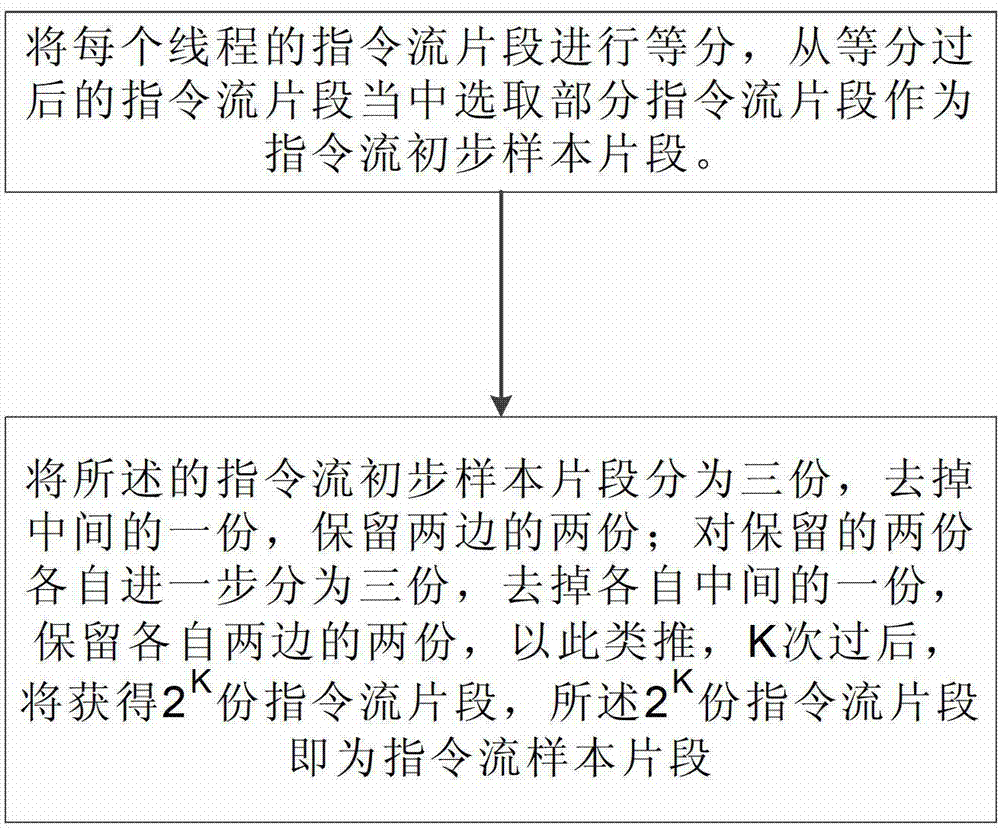

The invention provides a multi-core simulation parallel accelerating method based on sampling. The method includes the steps of S1, selecting a multithread application program as a multi-core benchmark test program; S2, adopting a sampling strategy to the selected multithread application program to acquire an instruction stream sample fragment of each thread; S3, operating the instruction stream sample fragment, acquired in S2, of each thread in a dynamic code analyzing module of a simulator, and segmenting the instruction stream sample fragment of each thread into multiple dispersing segments according to segmenting points; S4, grouping the multiple dispersing segments according to different segmenting points during segmenting; S5, operating the dispersing segments grouped in S4 in corresponding segment simulating modules to obtain simulation time needed for operating the dispersing segments; and S6, sum up all simulation time output by the segment simulating modules in S5 to obtain total time of the multithread application program in S1. Simulation speed is increased evidently, and evaluation cycle is shortened.

Description

technical field [0001] The invention relates to the field of computer architecture system simulation, in particular to a sampling-based multi-core simulation parallel acceleration method. Background technique [0002] With the rapid development of SoCs, the popularity of multi-core processors and the emergence of many-core processors, more and more components are integrated on a single chip. How to quickly find the optimal solution from the exponentially growing design solutions has gradually become a design key to such systems. For example, how to design a topological structure to interconnect hundreds of processing units and storage units, how to allocate storage levels, and how to determine the size of storage space required for each level, etc. Many design parameters will constitute a huge design space. Quickly locating the optimal design scheme in space has become a major challenge for this type of system design. [0003] Microarchitecture simulation is a key technolo...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): G06F9/455

Inventor 喻之斌须成忠姜春涛

Owner SHENZHEN INST OF ADVANCED TECH CHINESE ACAD OF SCI