System on a chip (SoC) system clock control method and SoC

A system clock and clock signal technology, which is applied in the direction of data processing power supply, signal generation/distribution, etc., to achieve the effect of reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

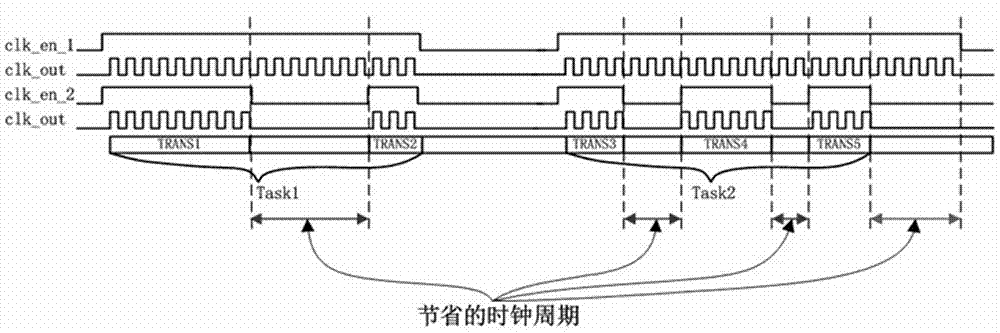

[0025] In response to the technical problems at the first level, this paper implements a method for accurately controlling clocks in SoC and an SoC using this method. In the method, the execution module sends a clock control signal according to its own actual working conditions, which avoids unnecessary dry running of the execution module and realizes precise control of the clock.

[0026] It should be noted that execution module is used again to denote a module corresponding to certain commands.

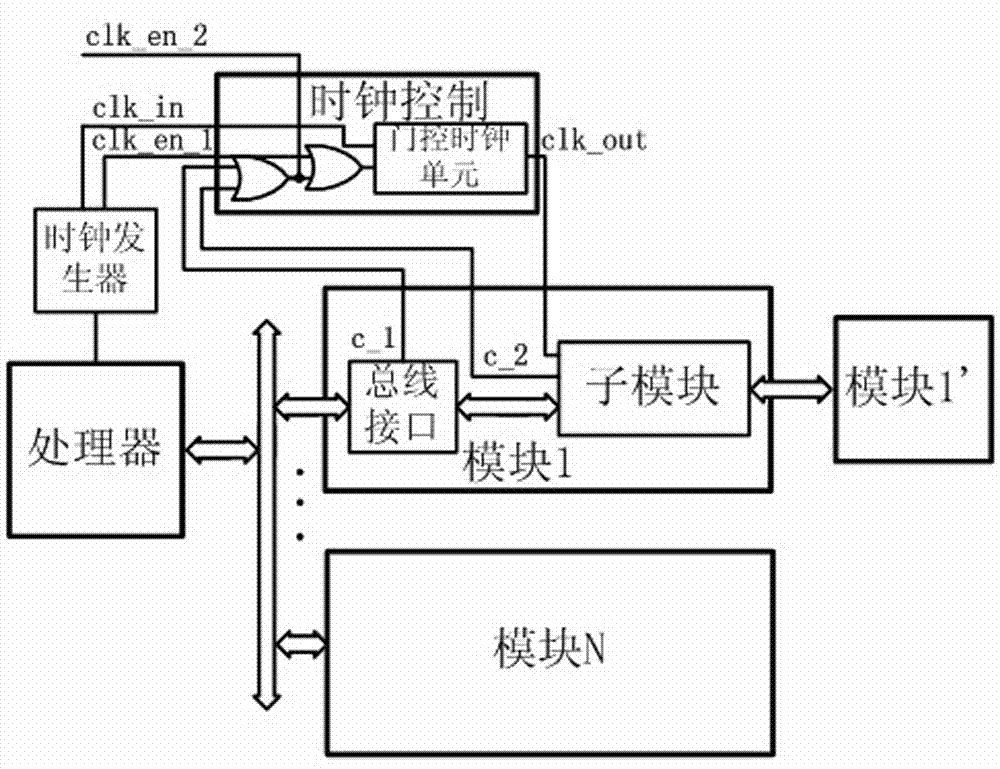

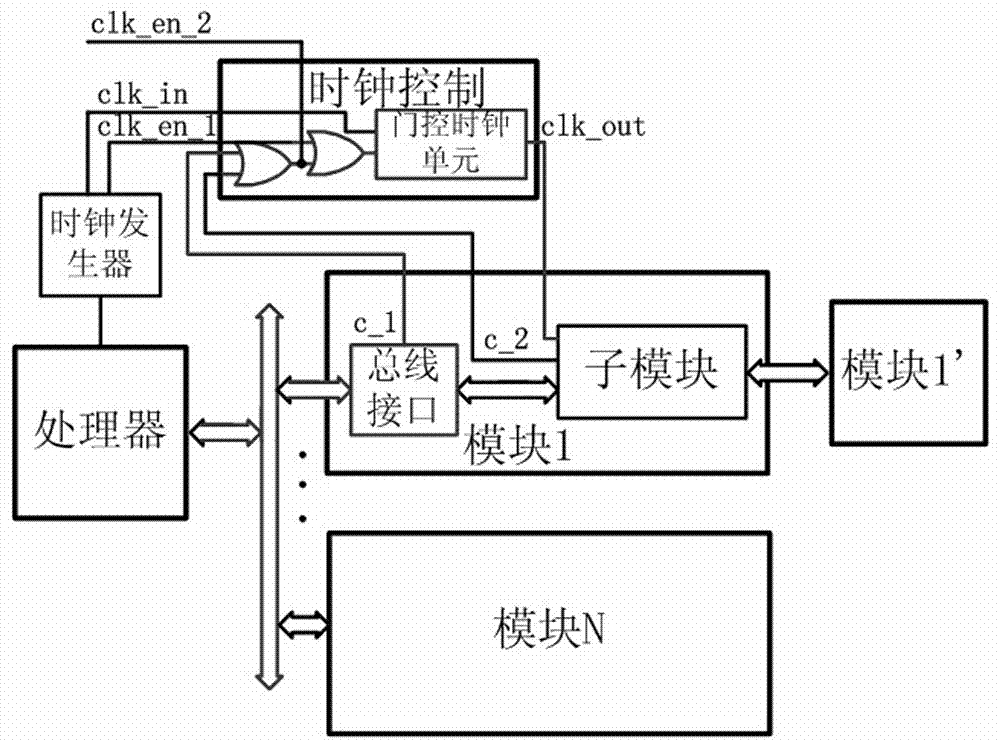

[0027] Regarding the module, a large number of functional modules are integrated in the SoC, in figure 1 In particular, there are 1~N outlets, and N represents a natural number, usually greater than or equal to 1, depending on the SoC product itself, so I won’t repeat it again.

[0028] figure 1 Describes the hardware block diagram of the SoC. The hardware structure in the figure is mainly composed of processor, bus, execution modules and clock control module. The core of this ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com