High speed network data flow load balancing scheduling method based on field programmable gate array (FPGA)

A load balancing and scheduling method technology, applied in the Internet field, can solve the problem of low balance of load balancing methods and achieve the effect of instantaneous balancing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Below in conjunction with accompanying drawing, provide the specific embodiment of the present invention. It should be noted that the parameters in the examples do not affect the generality of the present invention.

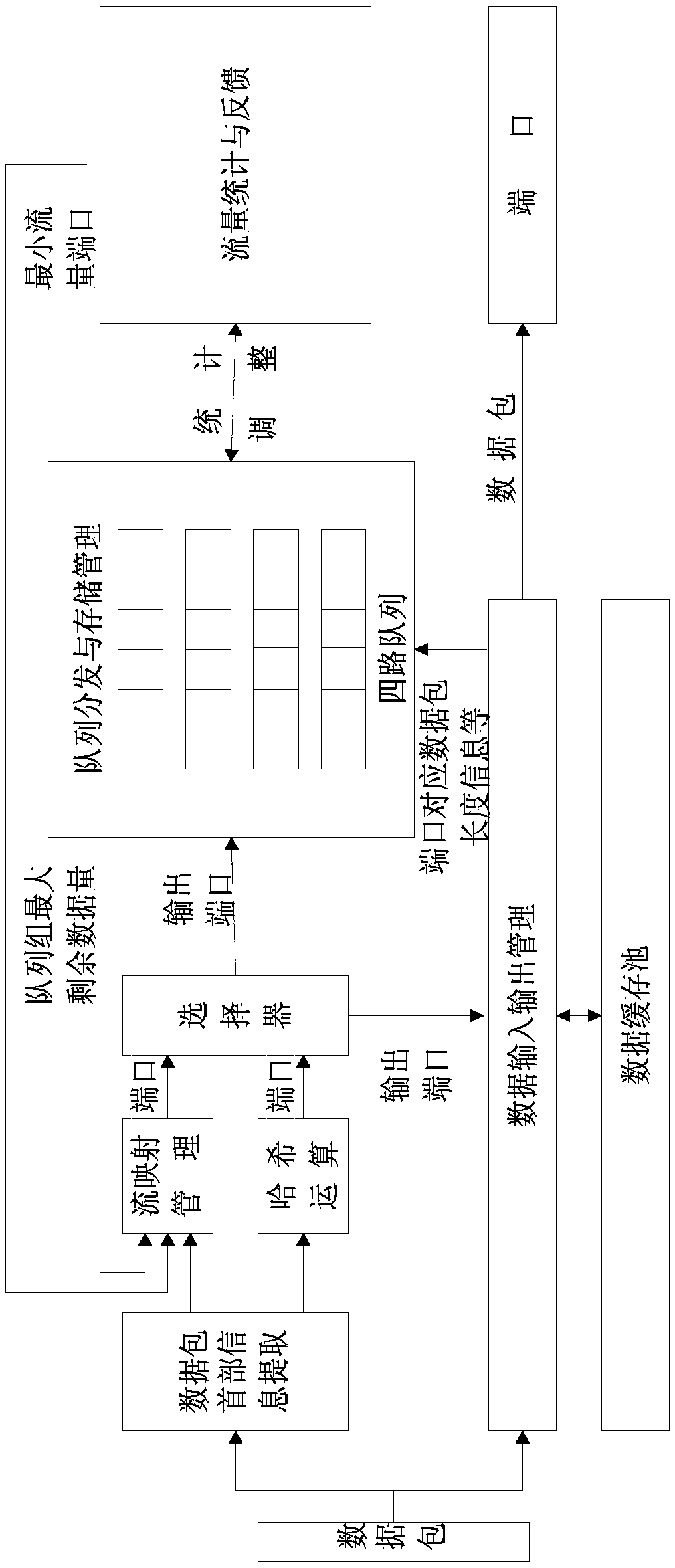

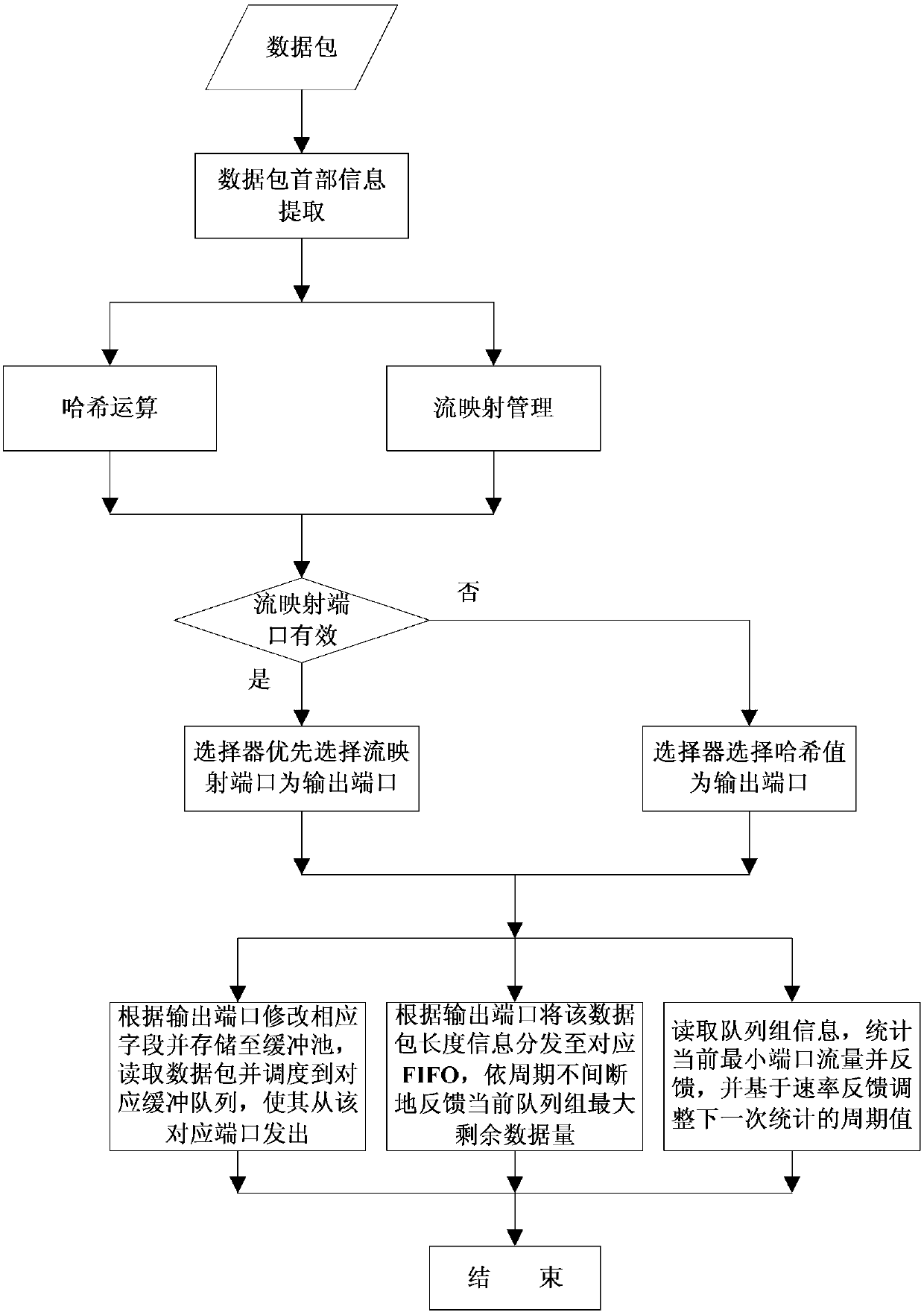

[0030] see figure 1 and figure 2 ,in figure 1 is a schematic diagram of the overall framework of the present invention, figure 2 It is an overall flowchart of the present invention.

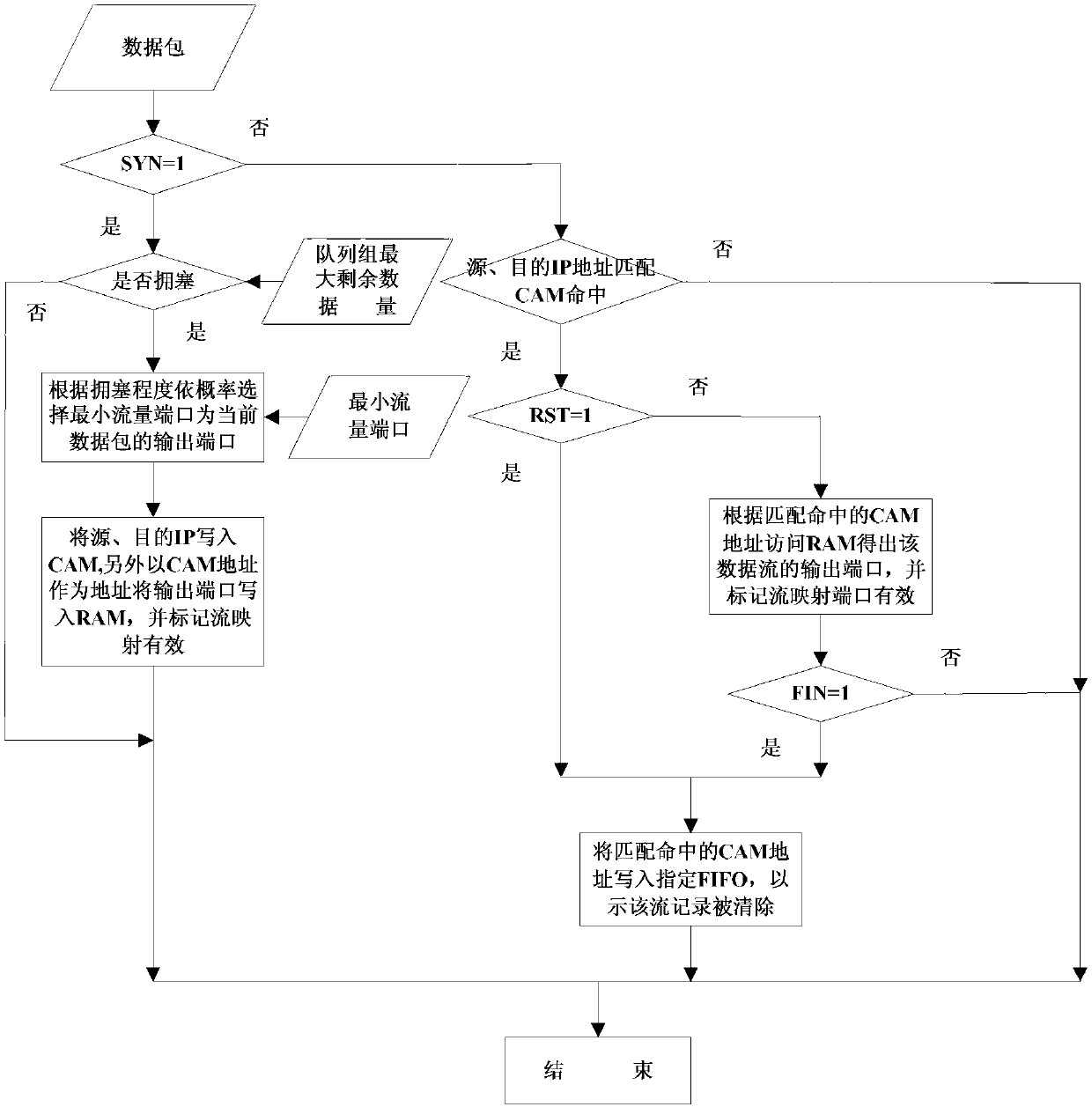

[0031] The specific design of the present invention is: first extract the header information of the data packet, perform hash operation and flow mapping management on the header information concurrently, and store the data packet in a data buffer at the same time, if the port of the flow mapping table is valid, the flow is preferentially selected The mapped port is the output port, otherwise the hash value is used as the output port; the data packets are sent from the corresponding port according to the concurrent execution of the output port, which ensures the sequence...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More