Low-offset full-motion comparator

A comparator and full dynamic technology, applied in the field of comparators, can solve problems affecting the normal operation of comparators, and achieve the effect of reducing the influence of offset voltage and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Below in conjunction with accompanying drawing and specific embodiment, further illustrate the present invention, should be understood that these embodiments are only for illustrating the present invention and are not intended to limit the scope of the present invention, after having read the present invention, those skilled in the art will understand various aspects of the present invention Modifications in equivalent forms all fall within the scope defined by the appended claims of this application.

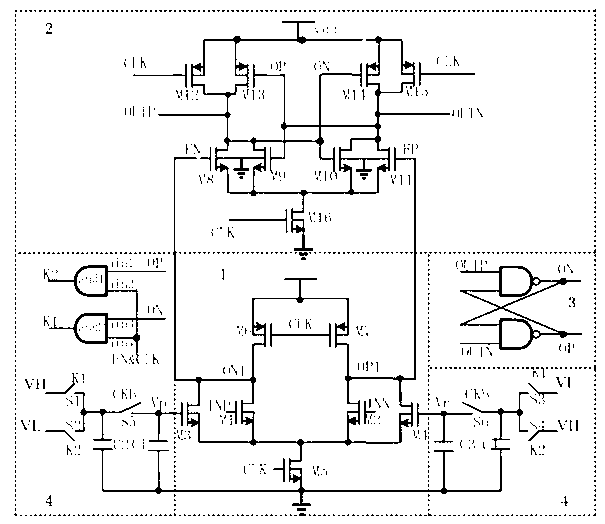

[0018] Such as figure 1 As shown, the present invention includes a pre-amplification circuit 1 , an offset elimination circuit 4 , a NAND gate latch 3 and a latch circuit 2 .

[0019] The latch circuit 2 is an existing circuit, which includes eighth to sixteenth MOS transistors M8-M16, wherein the twelfth to fifteenth MOS transistors M12-M15 are P-type MOS transistors. The gate of the eleventh MOS transistor M11 forms the first input terminal FP of the latch circuit, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More