A Low Offset High Speed Dynamic Comparator

A dynamic comparator, high-speed technology, applied in analog-to-digital converters, multiple input and output pulse circuits, pulse technology, etc., can solve problems such as limiting the response speed of the comparator, affecting the accuracy of the comparator, and limiting the application of the dynamic comparator. , to increase the comparison speed and reduce the effect of the offset voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

[0054] The novel low-offset high-speed dynamic comparator of the present invention can significantly increase the speed of the comparator, reduce the influence of the offset voltage of the comparator, and is very suitable for offset calibration of high-speed analog-to-digital converters.

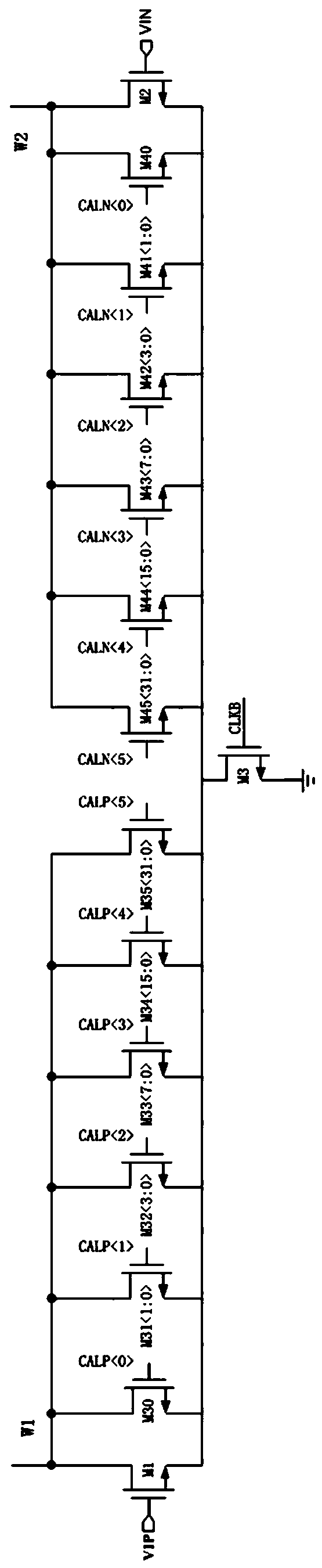

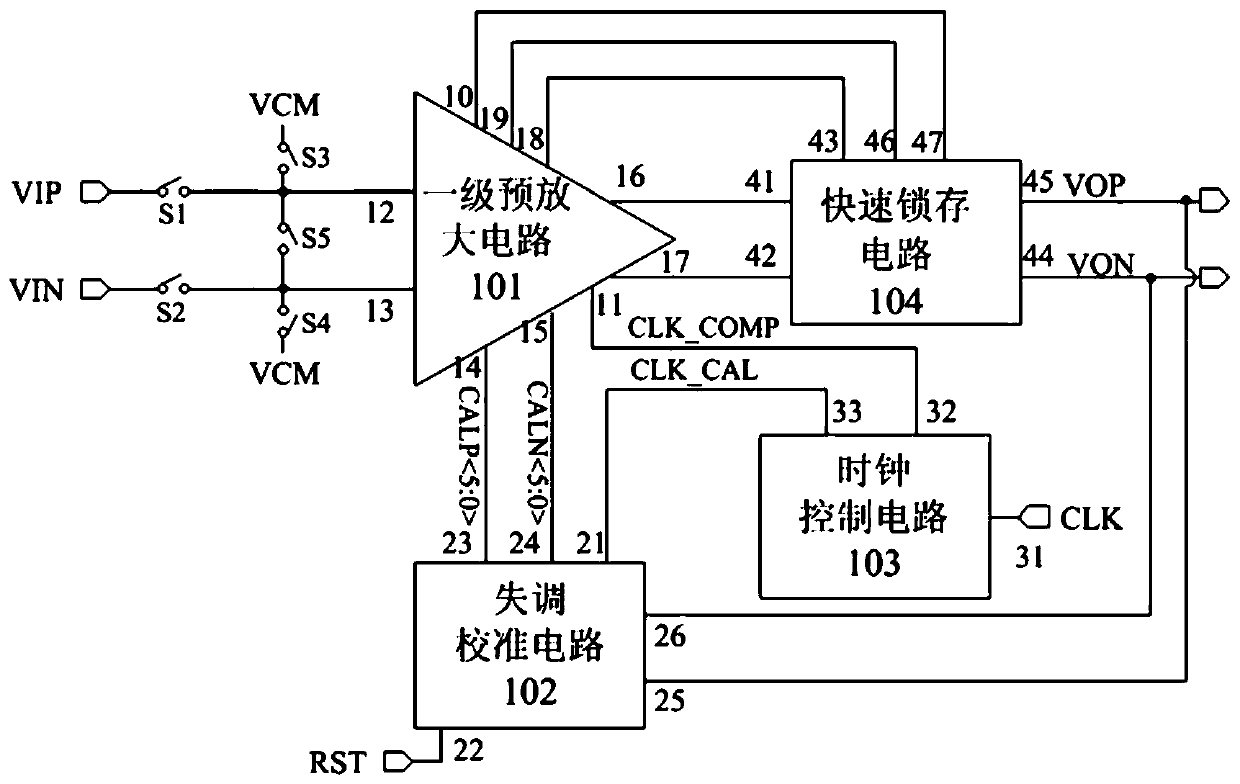

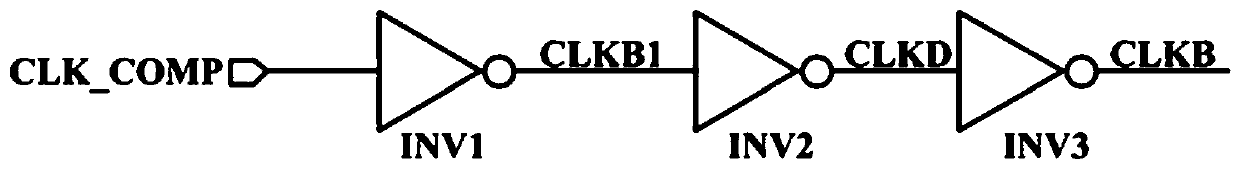

[0055] figure 1 It is a schematic diagram of a low-offset high-speed dynamic comparator according to the present invention, such as figure 1 As shown, the low-offset high-speed dynamic comparator of the present invention includes: a first-stage pre-amplification circuit 101, an offset calibration circuit 102, a clock control circuit 103, a fast latch circuit 104, a first switch S1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More