Device and method for testing field programmable gate array (FPGA) development board

A development board and test unit technology, applied in the field of FPGA testing, can solve problems such as poor contact, dense pin spacing, poor welding, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In order to make the technical problems, technical solutions and advantages to be solved by the present invention clearer, the following will describe in detail with reference to the drawings and specific embodiments.

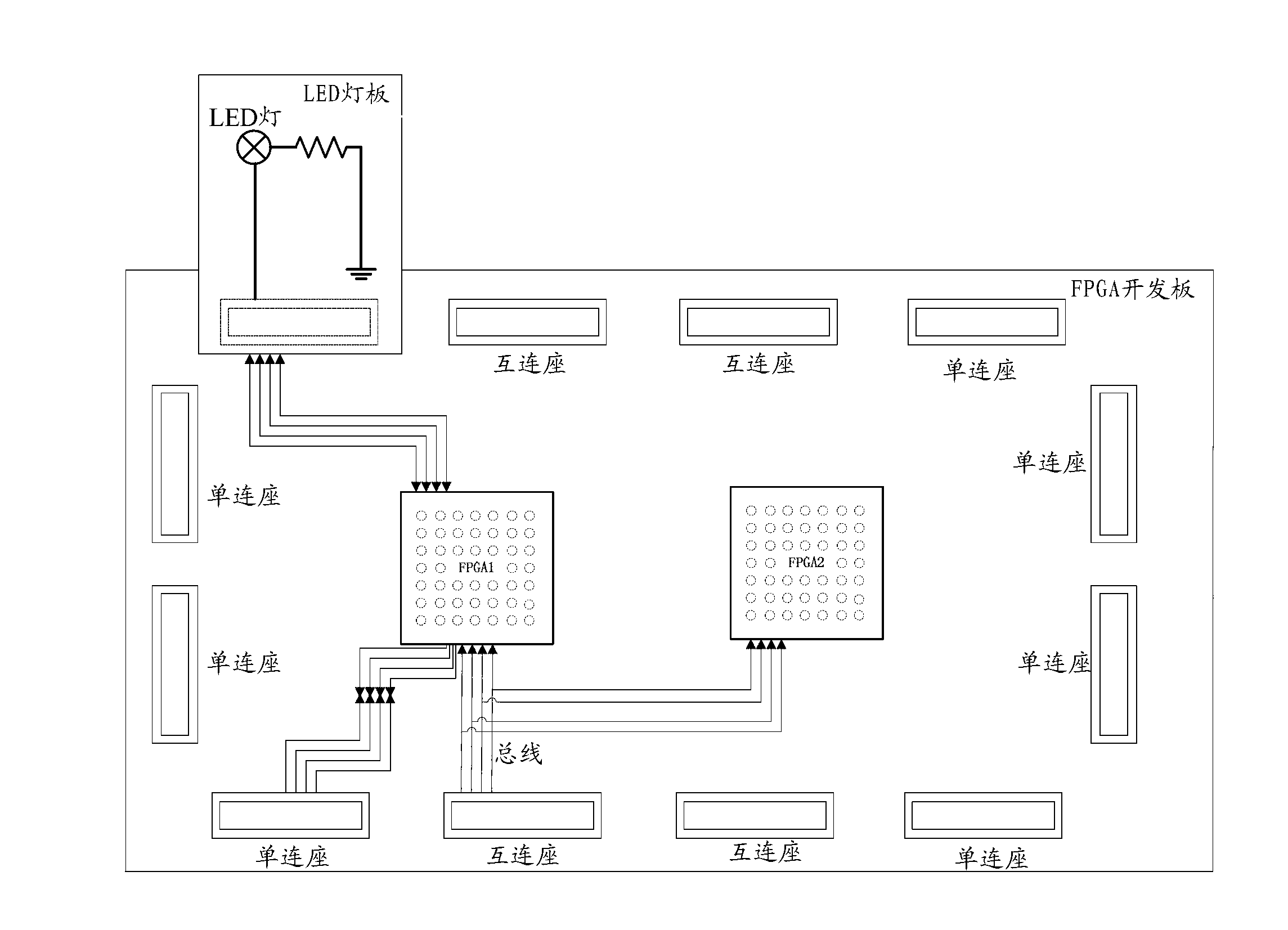

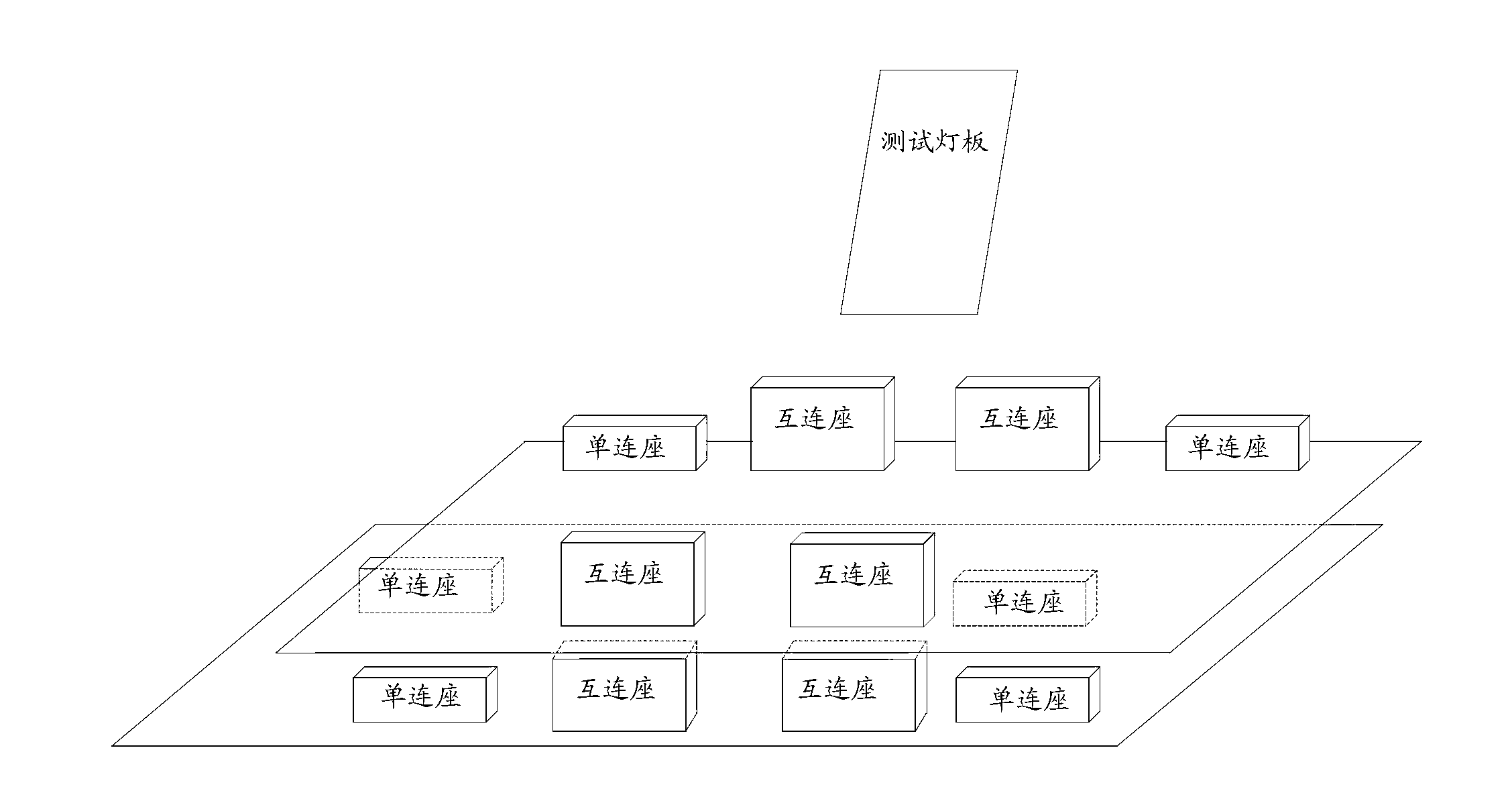

[0020] Embodiments of the present invention provide a device for testing FPGA development boards, such as figure 1 As shown, the FPGA development board includes an FPGA chip,

[0021] Devices include:

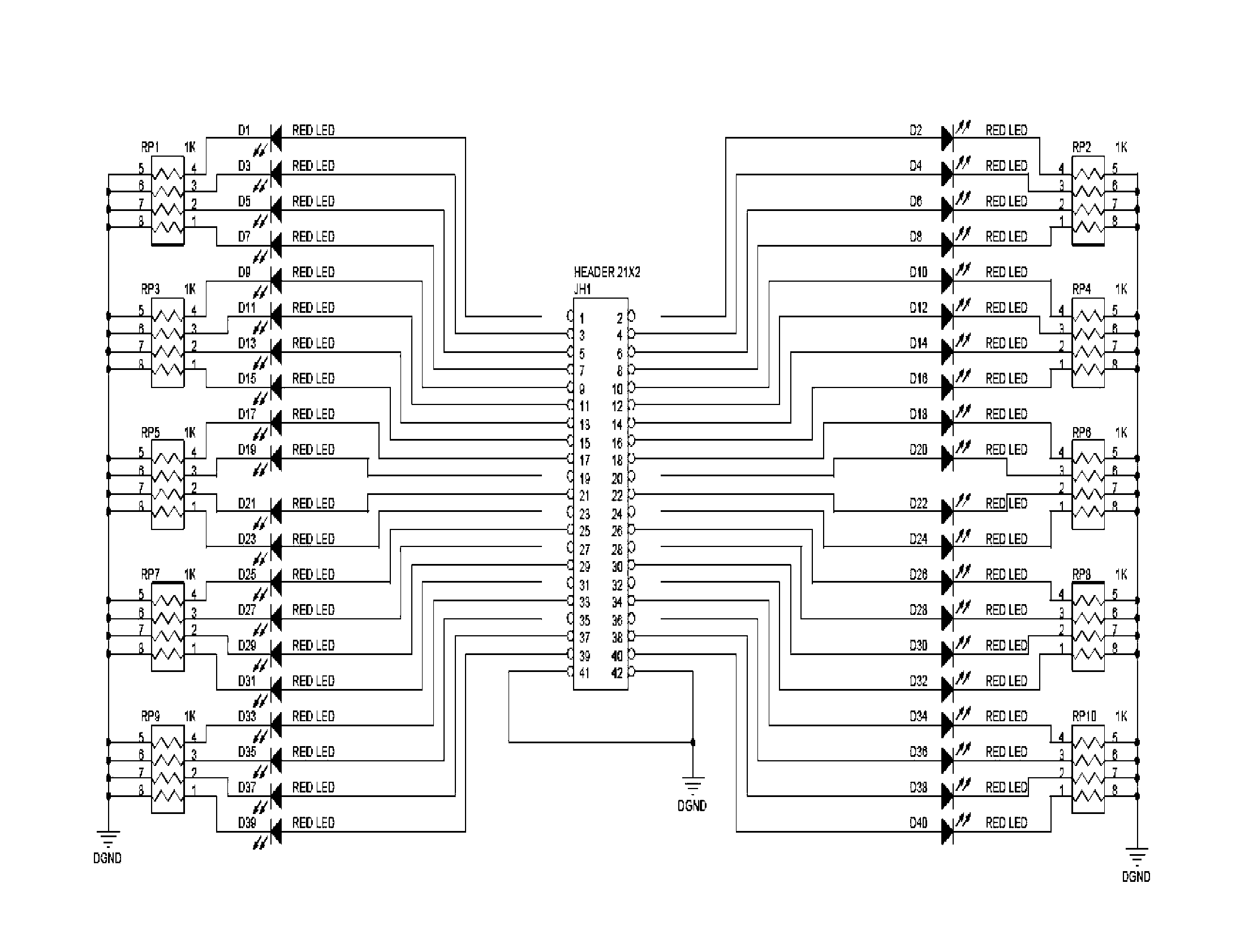

[0022] The LED light board includes a plurality of LED pins, each LED pin is connected to a corresponding LED light, the negative terminals of all LED lights are grounded, and the LED light is lit when the corresponding LED pin is at a high potential;

[0023] The arrangement of the LED pins is consistent with the arrangement of the communication pins of the high-speed seat in the FPGA development board, and supports electrical connection with the communication pins;

[0024] The communication pins of the high-speed seat are electrically connected to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More