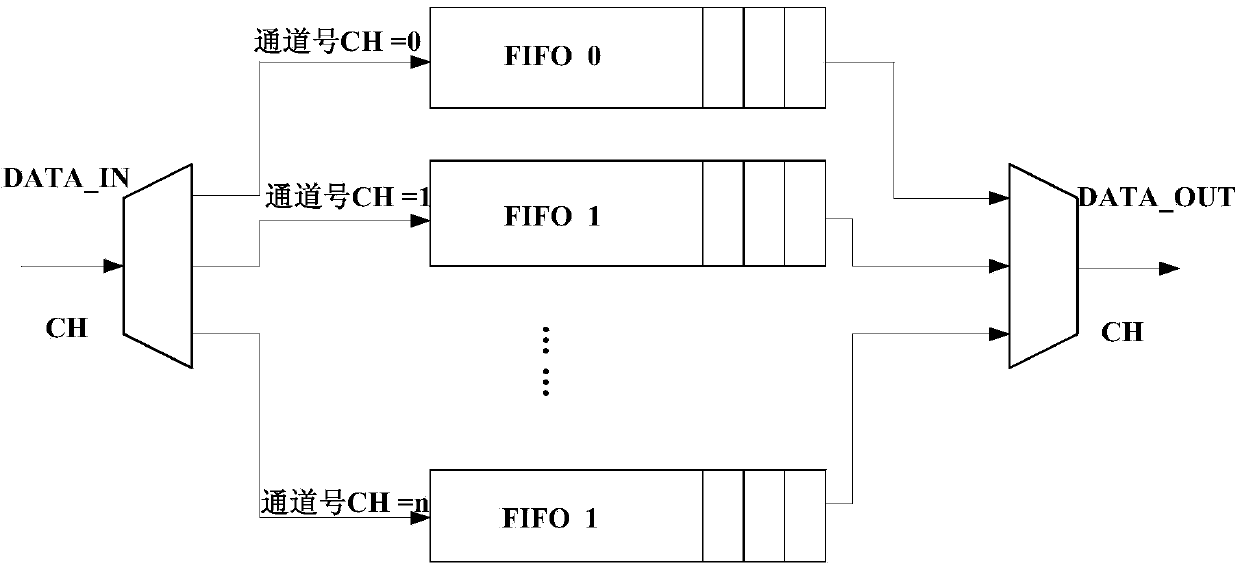

Multi-channel first-in first-out buffer queue controller and access method

A first-in-first-out, cache queue technology, applied in the field of data transmission, can solve problems such as poor reliability and unrecoverable

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

[0121] Such as Figure 4 As shown, in the multi-channel FIFO queue controller of Example 1, the address determination circuit is implemented by two independent circuit modules, namely: FIFO write address remapping unit 401 (responsible for determining the address of the write operation) and FIFO read address remapping unit 401 Mapping unit 402 (responsible for determining the address of the read operation), the control circuit (in Figure 4 not shown in the figure) to control the read and write operations of data in the data cache (RAM) 403 by sending out RAM read and write enable signals (ram_wr_en, ram_rd_en) respectively.

[0122] The functions of the above-mentioned FIFO write address remapping unit 401 and FIFO read address remapping unit 402 are independent of each other. For the entire multi-channel FIFO queue controller, only the read or write operation of RAM403 can be performed at present, and the read operation of RAM can also be performed simultaneously. and write...

example 2

[0169] The structure and working principle of the multi-channel FIFO queue controller provided in Example 2 are similar to the multi-channel FIFO queue controller provided in Example 1, for example Figure 8 As shown, the multi-channel FIFO queue controller also includes a FIFO write address remapping unit 801 (responsible for determining the address of the write operation) and a FIFO read address remapping unit 802 (responsible for determining the address of the read operation), a data cache 803, a read-write control unit( Figure 8 not shown in ), table item automatic refresh unit 804, and FIFO alarm unit 805, the difference is that, for FIFO write address remapping unit 801 and FIFO read address remapping unit 802, the table items it contains are the same as those in Example 1 different.

[0170] Specifically, as Figure 8 As shown, the FIFO write address remapping unit 801 and the FIFO read address remapping unit 802 respectively include a quantity table (BLK_NUM_TBL), a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More