Chip routing selection circuit free of quiescent dissipation

A technology for chip bonding and circuit selection, which is applied in the direction of logic circuit coupling/interface, logic circuit connection/interface layout, etc. using field effect transistors, and can solve problems affecting the layout of integrated circuits.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

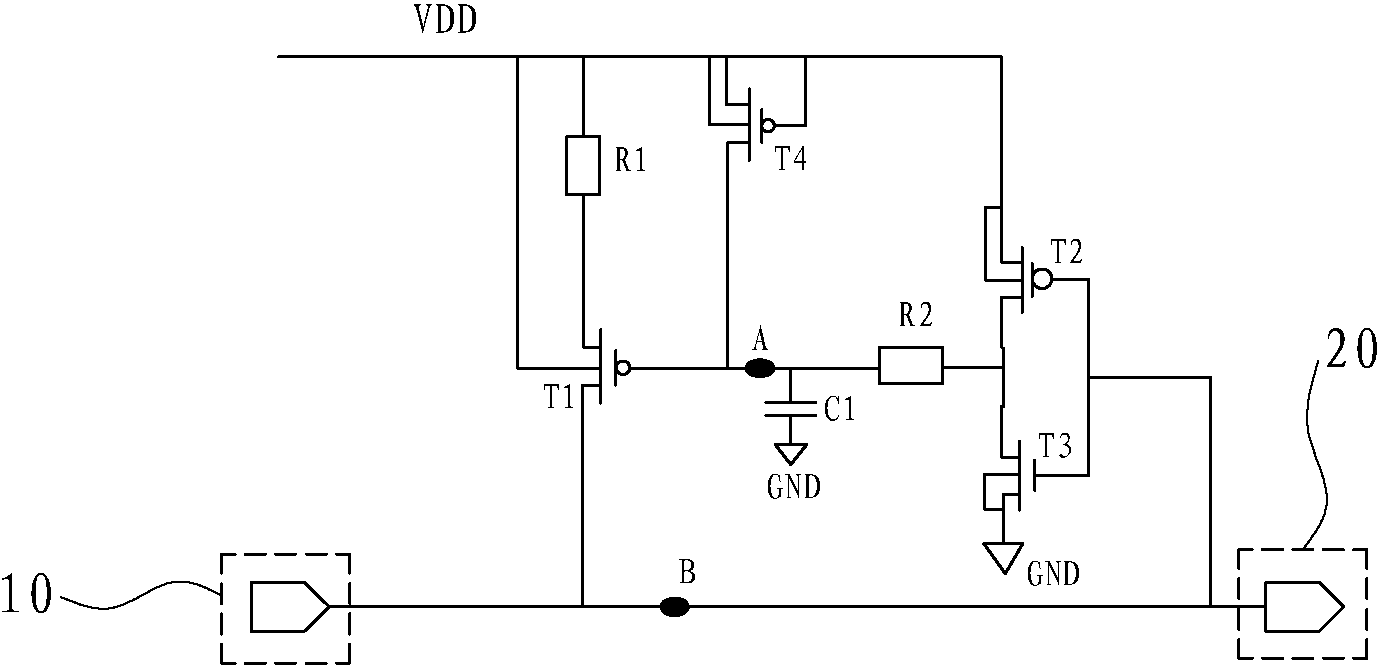

[0025] refer to image 3 As shown, a chip bonding selection circuit without static power consumption disclosed by the present invention includes a PMOS transistor T1, a resistor R1, a capacitor C1, a PMOS transistor T2, an NMOS transistor T3, a resistor R2 and a PMOS transistor T4.

[0026] The D pole of the PMOS transistor T1 is connected to the circuit control terminal 10 and the circuit controlled terminal 20, the circuit control terminal 10 is the chip bonding connection plate, the chip bonding connection plate is suspended or connected to GND; the circuit controlled terminal 20 is the output logic pin , The output logic pin is connected to the chip.

[0027] The S pole of the PMOS transistor T1 is connected in series with the resistor R1 to VDD, the S pole and the G pole of the PMOS transistor T4 and the S pole of the PMOS transistor T2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More