Chip burning checking method

A verification method and chip technology, applied in the direction of response error generation, redundant code error detection, etc., can solve the problems of low product quality and safety factor, high abnormal programming error, and poor stability of overall programming verification, etc. Achieve the effect of improving the overall test efficiency, improving the quality and safety factor, and avoiding programming errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] In order to allow those skilled in the art to better understand the technical solutions of the present invention, the present invention will be further described below in conjunction with the accompanying drawings.

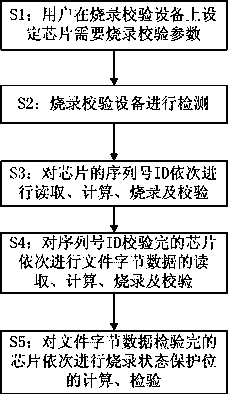

[0016] Such as figure 1 As shown, the present invention discloses a method for realizing the programming and verification of the BQ2022A new encryption IC, specifically, an integrated multi-channel programming and verification calculation and comparison method, including the following programming and verification steps:

[0017] S1: The user sets the serial number ID parameters, file byte parameters, and programming status protection bit parameters of the chip that need to be burned and verified on the burning verification device; specifically: the user sets the burning file name path, serial number ID , checksum calculation area range and checksum programming address, chip programming status protection bit area, serial number ID, required programming file ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More