SRAM and its method for improving write redundancy

A technology of static randomness and write redundancy, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of small equivalent resistance and small write redundancy, and achieve an increase in equivalent Resistance, improved hole mobility, and improved write redundancy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to illustrate the technical content, structural features, achieved goals and effects of the present invention in detail, the following will be described in detail in conjunction with the embodiments and accompanying drawings.

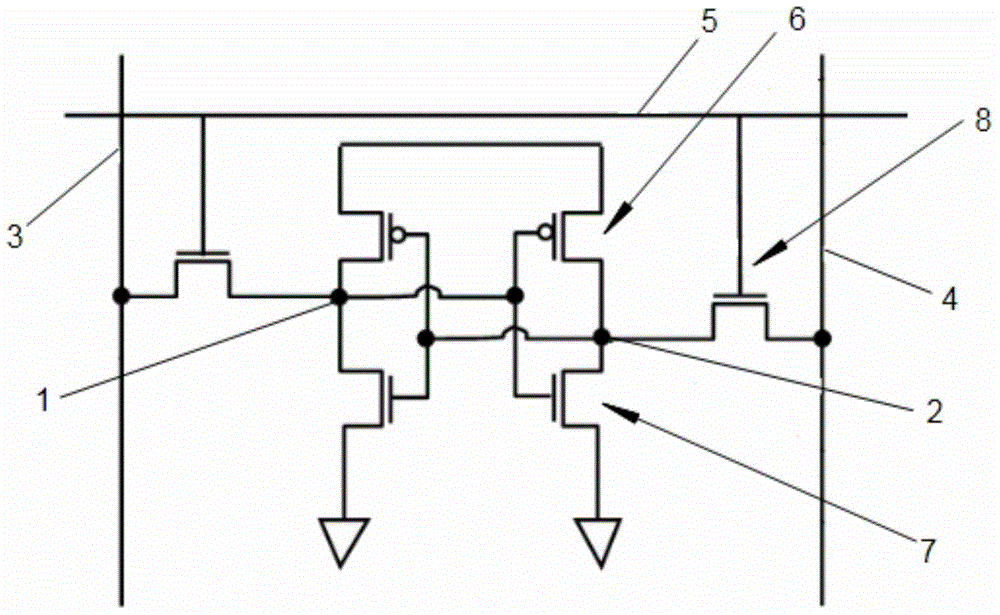

[0025] see figure 1 , figure 1 Shown is a schematic diagram of an equivalent circuit for writing in the SRAM of the present invention. Write margin (Write Margin) is an important parameter to measure the write performance of the SRAM unit. In the writing equivalent circuit of the SRAM, it is assumed that the first node 1 stores data at a low potential (that is, the stored data is "0"), and the second node 2 stores data at a high potential (that is, stores The data is "1"), non-limiting list, for example, writing a high potential to the first node 1, writing a low potential to the second node 2, before the writing action, the first bit line 3 will be precharged to a high potential, and the second bit line 4 will be precharged to a low ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More