Patents

Literature

63results about How to "Increase the equivalent resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for suppressing vehicle network low-frequency oscillation and system thereof

ActiveCN106505588AIncrease the equivalent resistanceIncrease dampingPower oscillations reduction/preventionElectrical resistance and conductanceEngineering

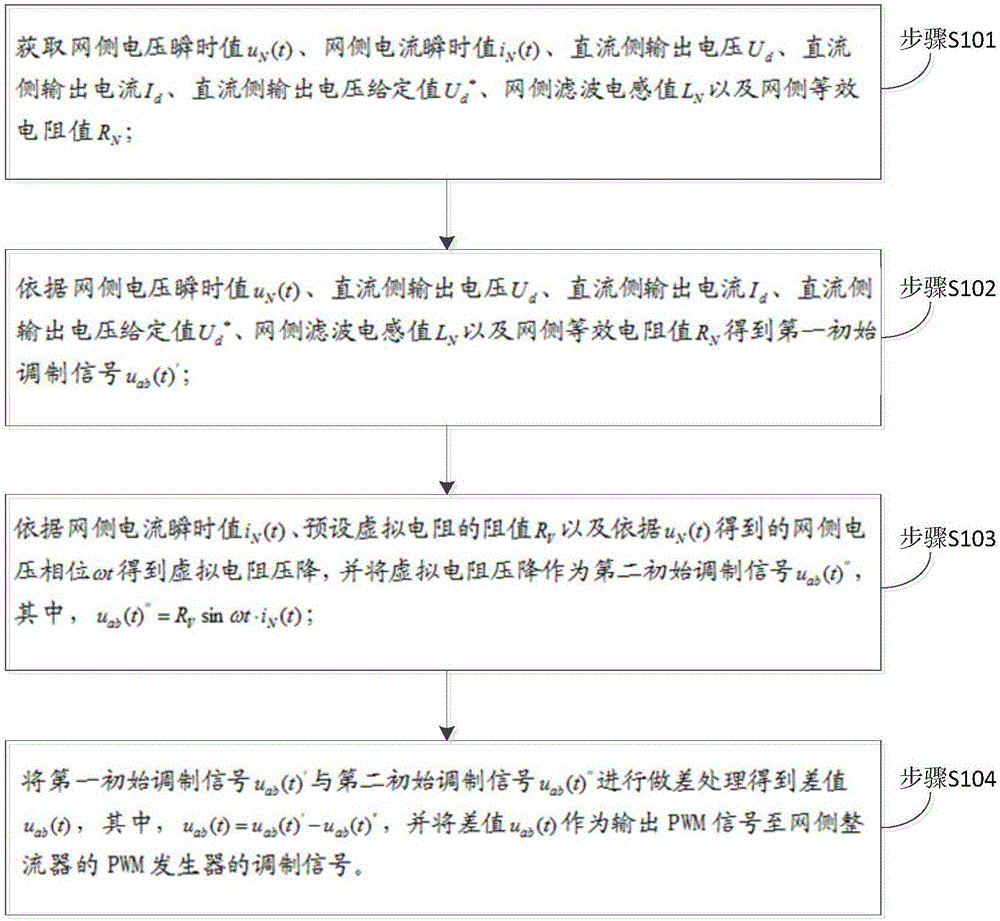

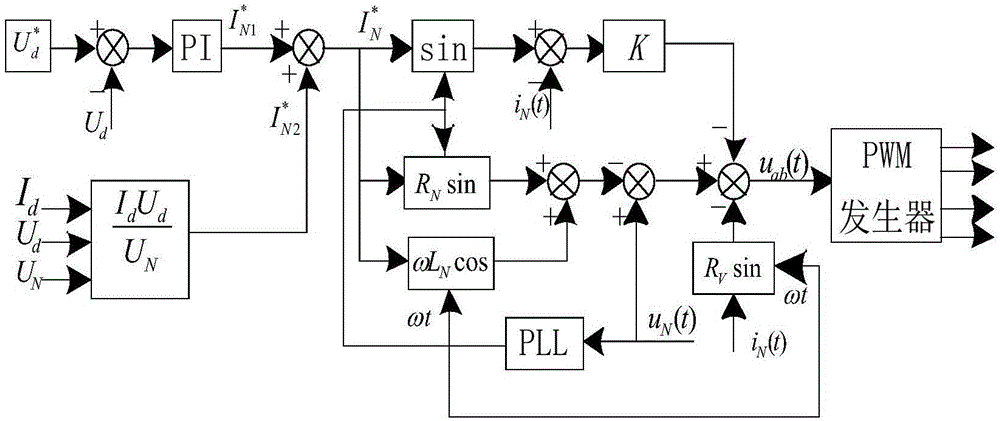

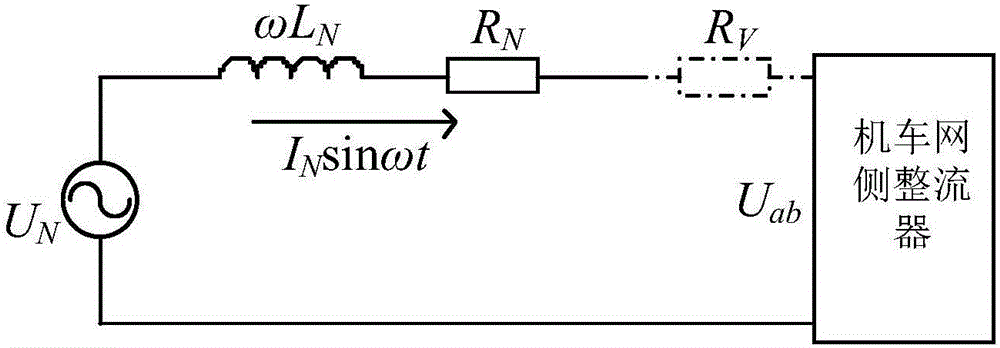

The invention discloses a method for suppressing vehicle network low-frequency oscillation and a system thereof. The method comprises the steps that a network side voltage instantaneous value, a network side current instantaneous value, DC side output voltage, DC side output current, a DC side output voltage given value, a network side filtering inductance value and a network side equivalent resistance value are acquired; a first initial modulation signal is obtained according to the network side voltage instantaneous value, the DC side output voltage, the DC side output voltage given value, the network side filtering inductance value and the network side equivalent resistance value; a second initial modulation signal is obtained according to the network side current instantaneous value, the resistance value of a preset virtual resistor and the network side voltage phase obtained according to the network side voltage instantaneous value; and difference processing is performed on the first initial modulation signal and the second initial modulation signal so that a difference value is obtained, and the difference value acts as an output PWM signal to the modulation signal of the PWM generator of a network side rectifier. The low-frequency oscillation of the vehicle network system can be effectively suppressed so that the stability of the vehicle network system can be enhanced without increasing hardware cost.

Owner:CSR ZHUZHOU ELECTRIC LOCOMOTIVE RES INST

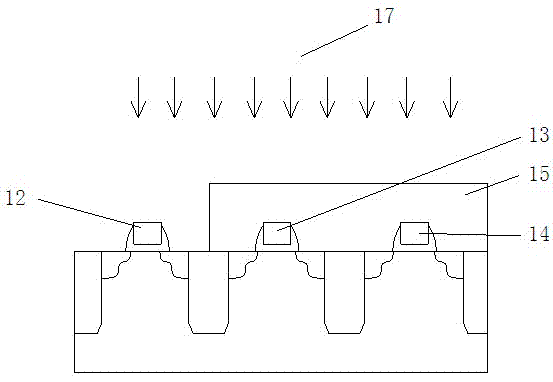

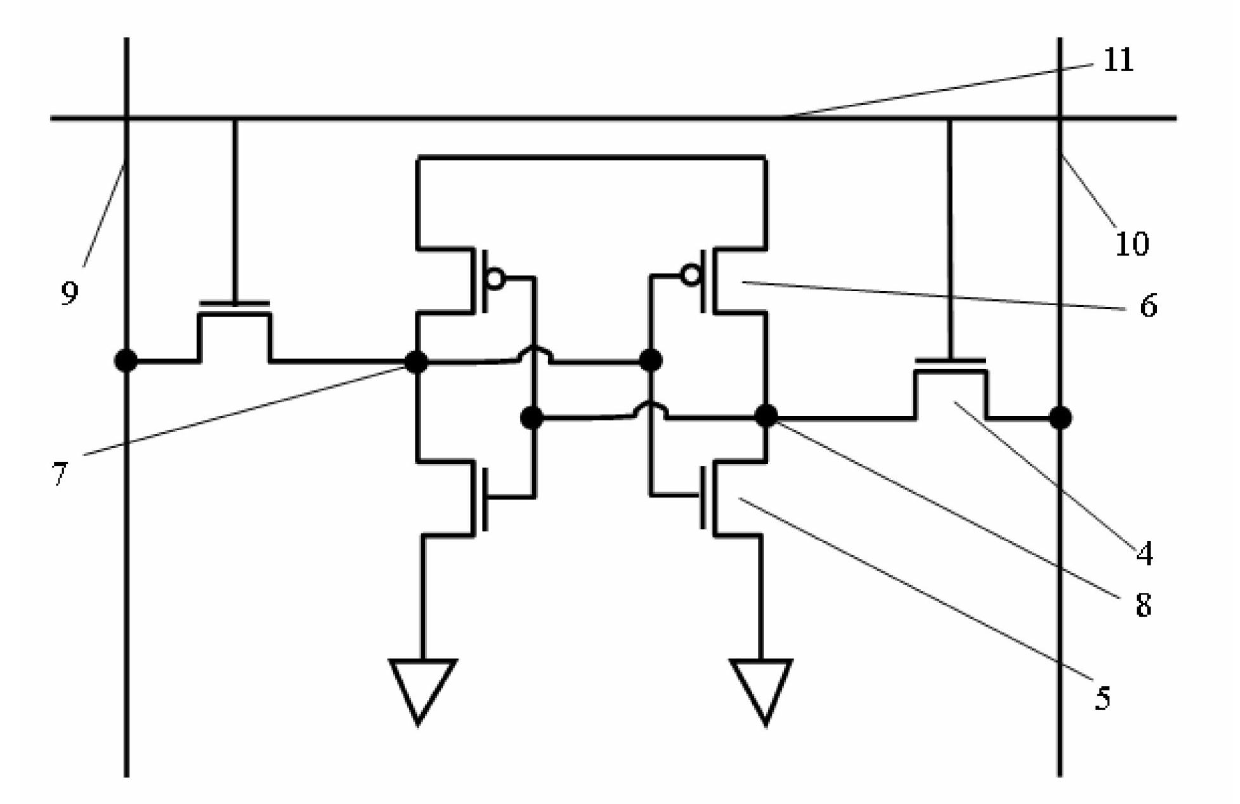

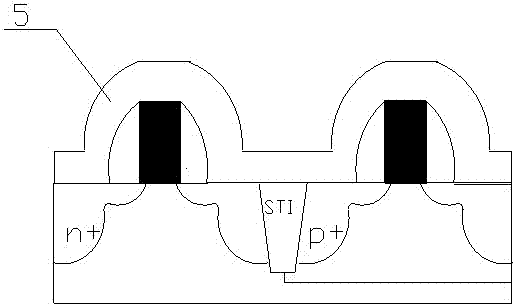

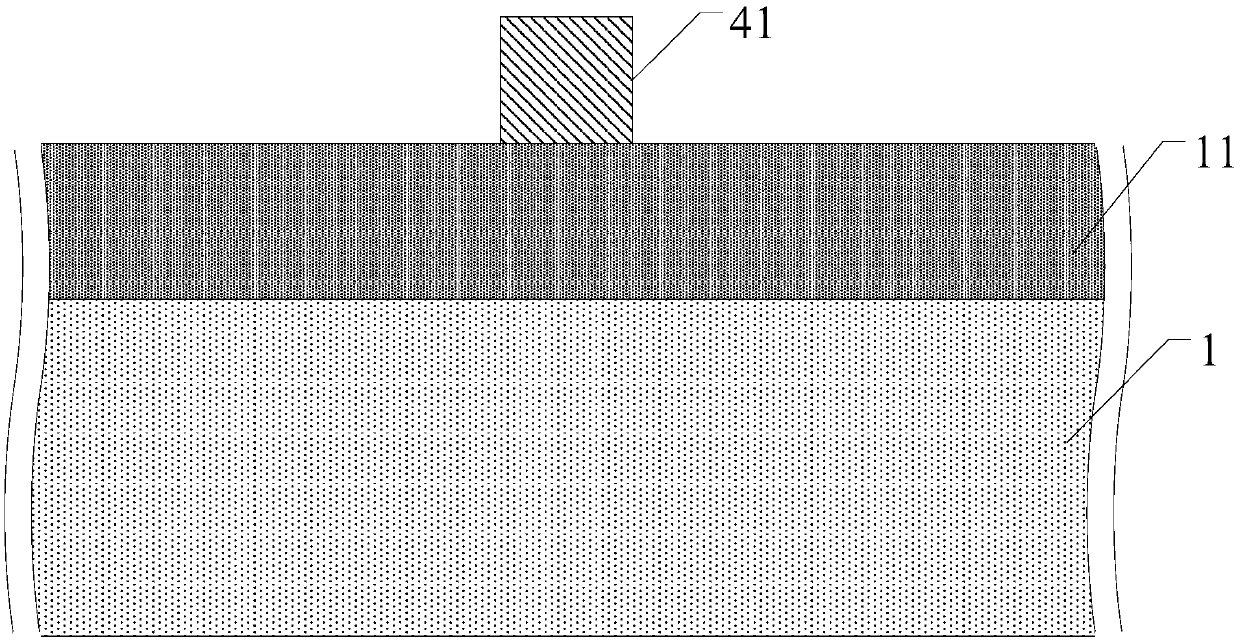

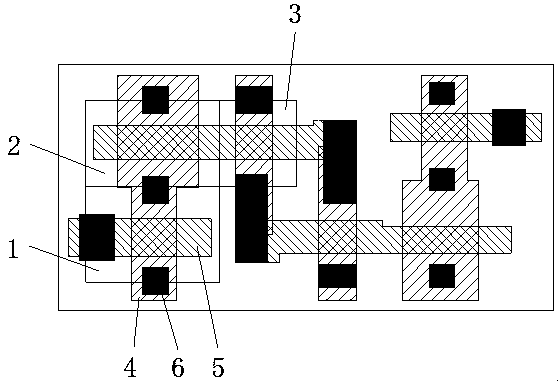

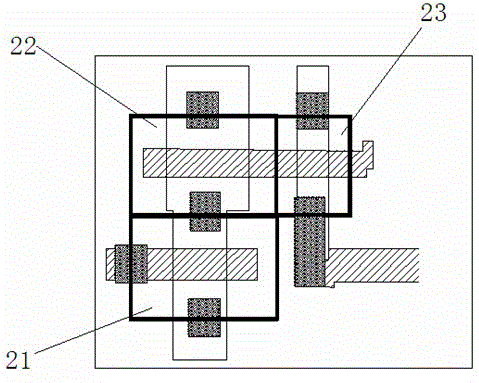

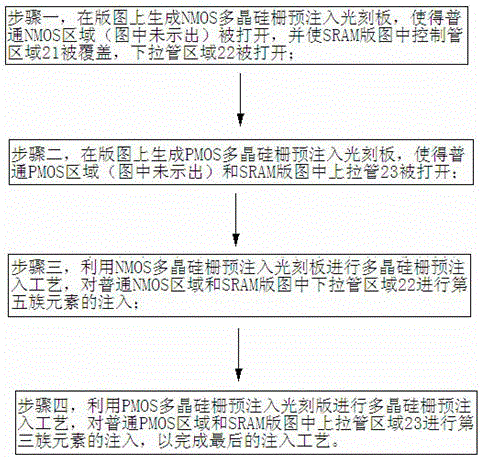

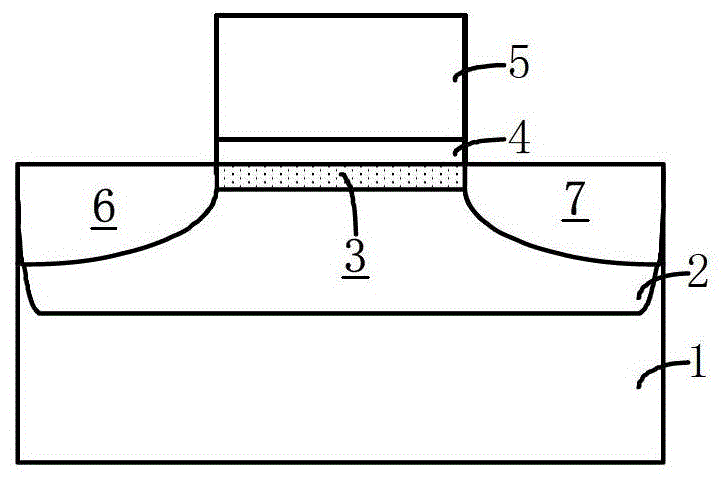

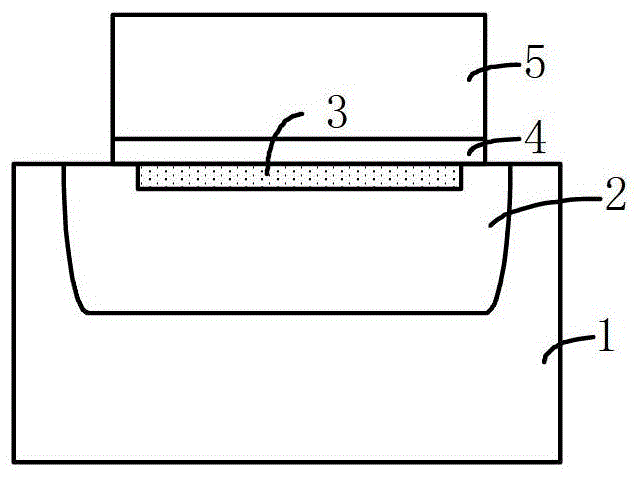

Method for improving write redundancy of high SRAM (static random access memory)

ActiveCN102738084AIncrease the tensile stressIncrease the equivalent resistanceSemiconductor/solid-state device manufacturingOxide semiconductorMetal

The invention discloses a method for improving write redundancy of a high SRAM (static random access memory). An NMOS (n-channel metal oxide semiconductor), a PMOS (p-channel metal oxide semiconductor) and an upper pulling pipe with cover layers are involved. The method comprises the following steps of: firstly simultaneously removing the cover layers of the NMOS device and the upper pulling pipe; and carrying out carbon injection on the PMOS and the upper pulling pipe with the cover layers so that a source drain end of the NMOS and a source drain end of the upper pull pipe form a crystal lattice structure and the tensile stress in a channel direction is improved. Through the method for improving the write redundancy of the high SRAM, disclosed by the invention, a carbon injection process is utilized to the source drain end of the upper pull pipe so that the tensile stress of the upper pull pipe in the channel direction is improved, the carrier mobility of the upper pull pipe is effectively reduced, the equivalent resistance of the upper pull pipe is increased, and simultaneously the write redundancy of an RAM (random-access memory) is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

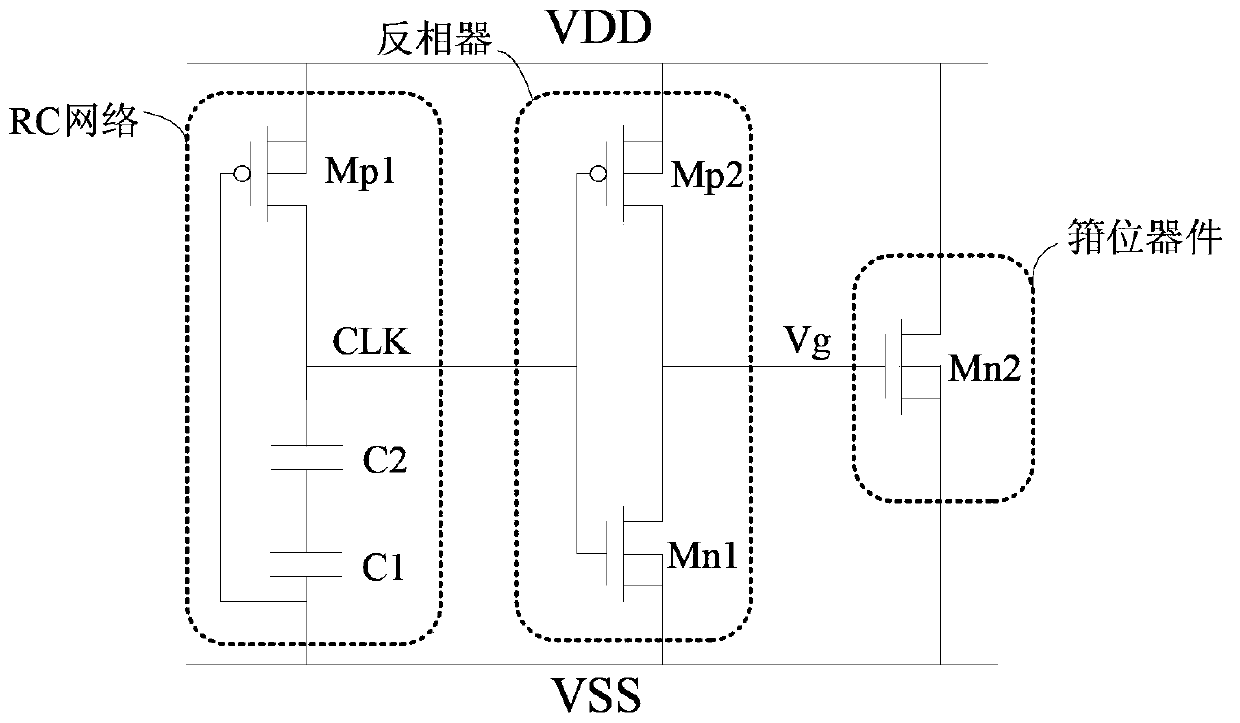

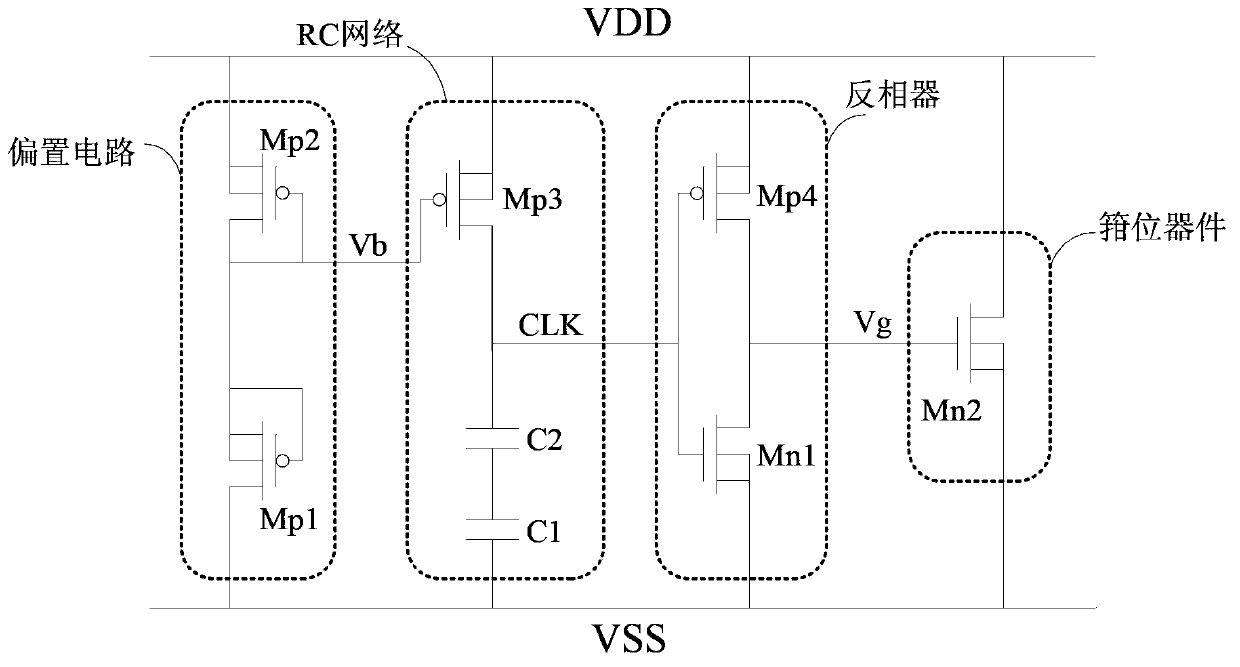

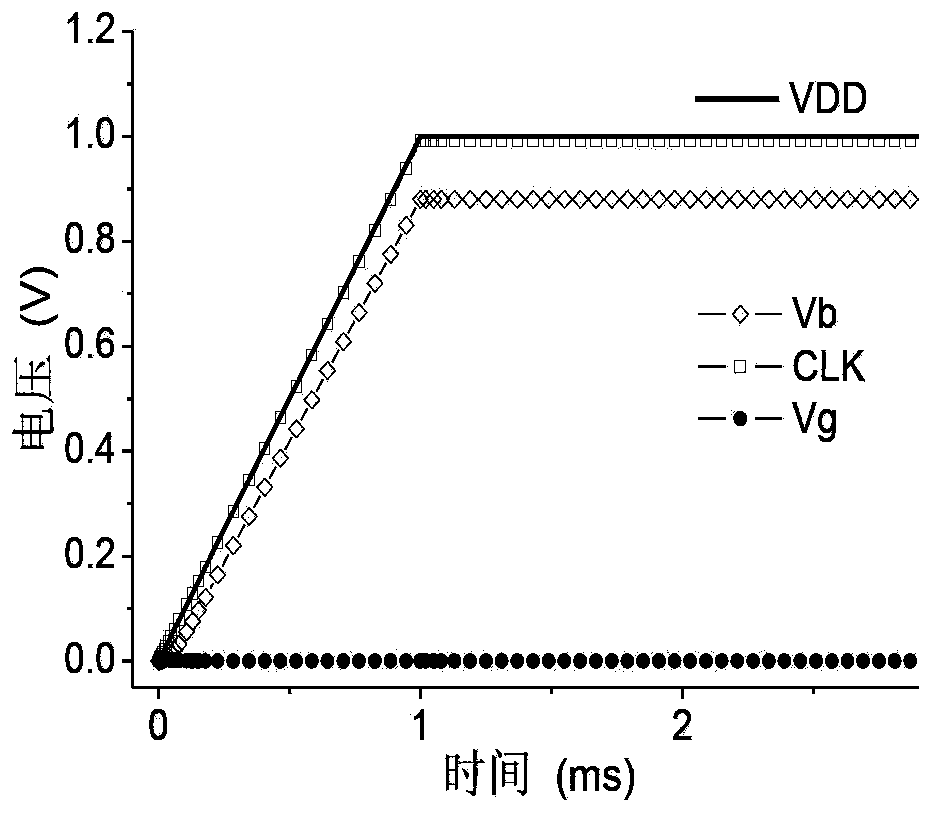

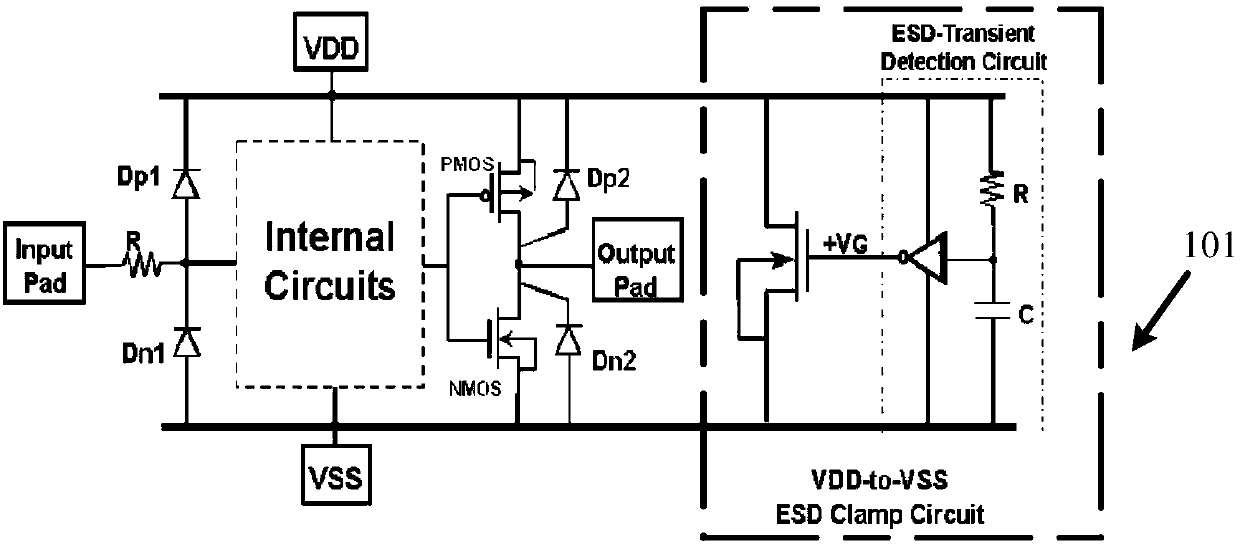

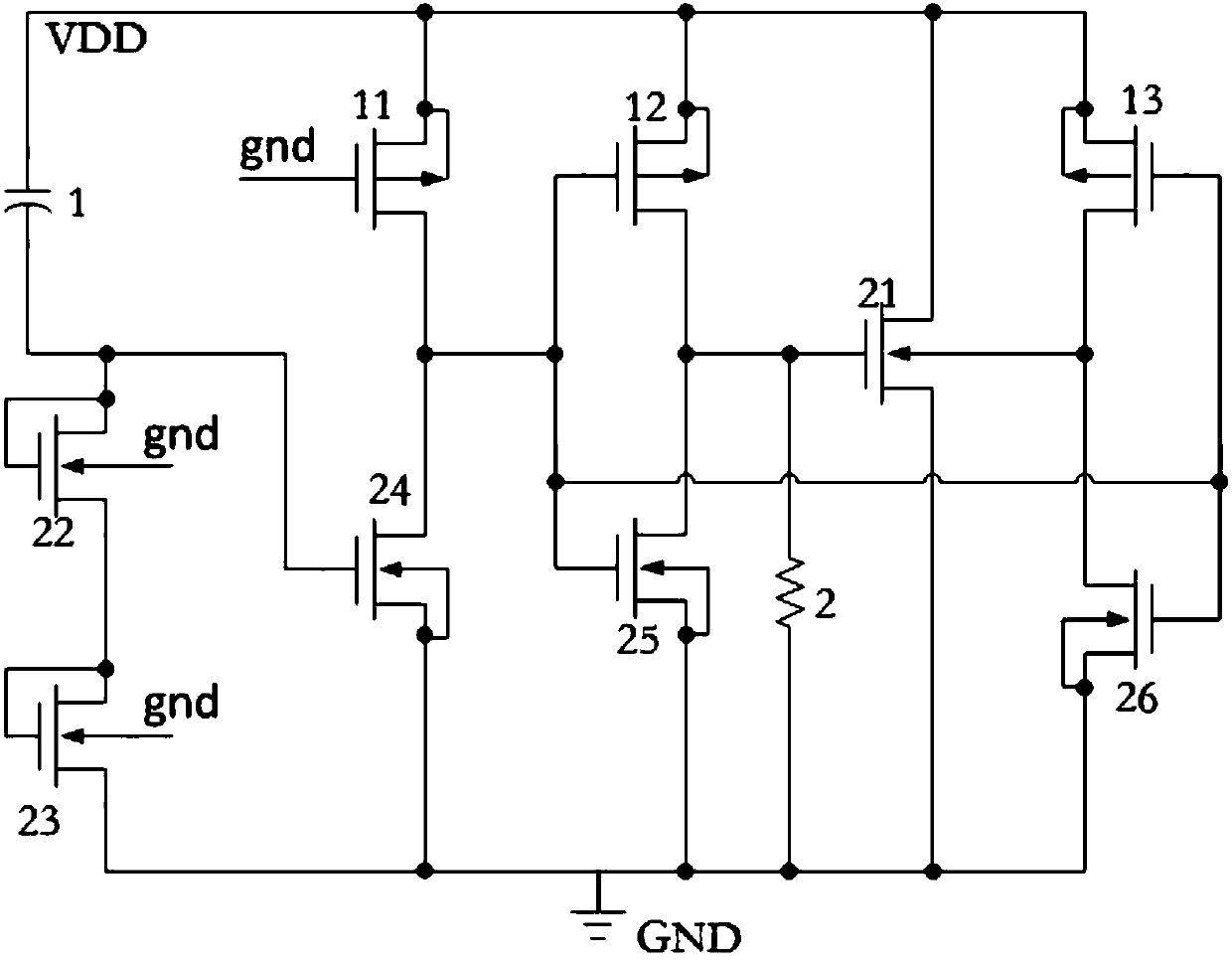

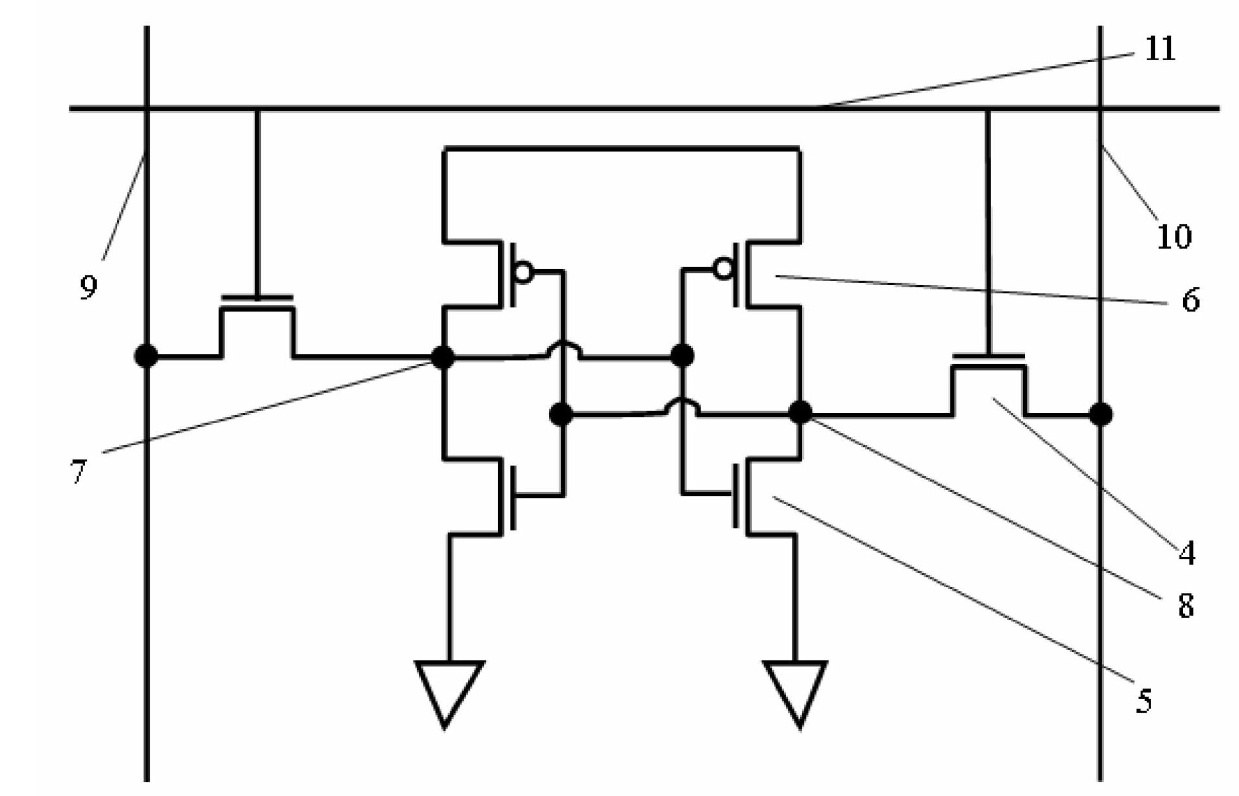

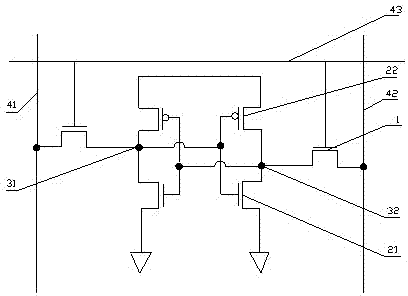

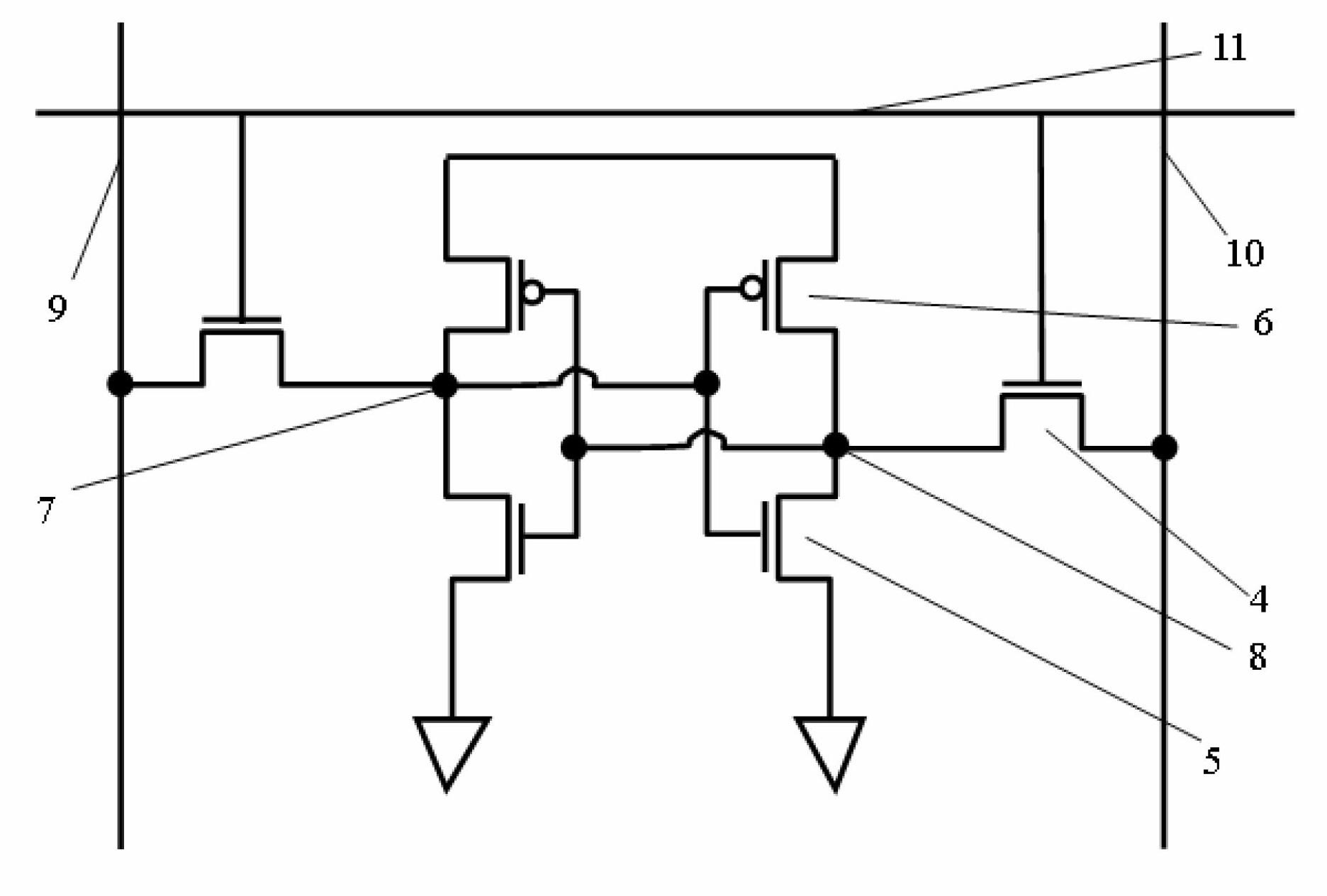

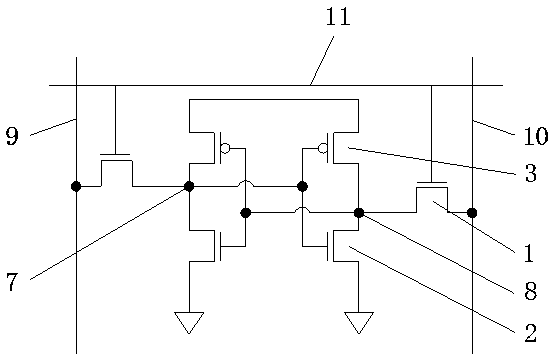

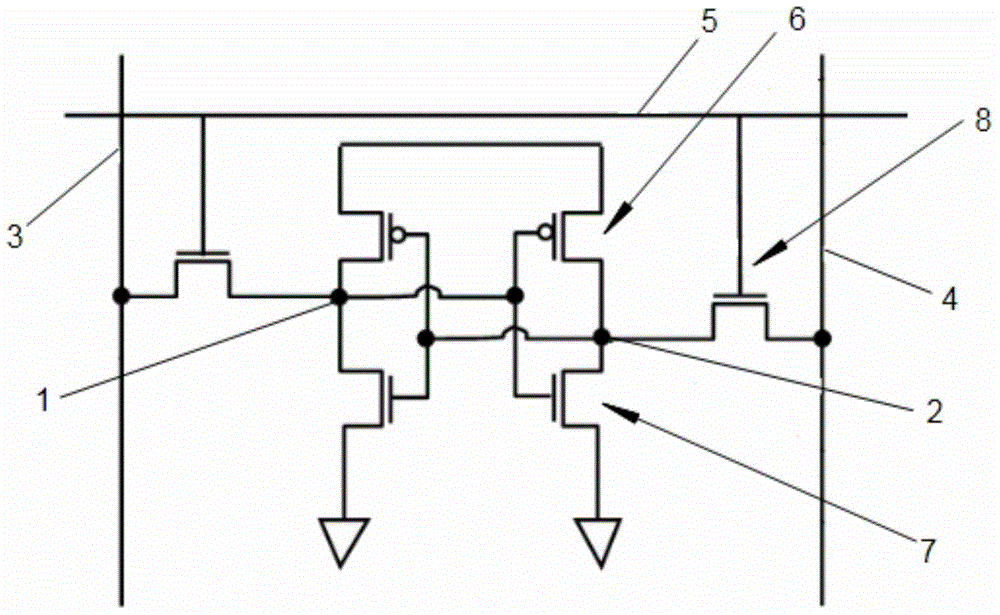

Static discharge clamping circuit with bias circuit in 90 nanometer CMOS (complementary metal-oxide-semiconductor transistor) process

ActiveCN103400827AReduce static leakageReduce source-gate voltageSemiconductor/solid-state device detailsSolid-state devicesNanometer cmosResistance capacitance

The invention discloses a static discharge clamping circuit with a bias circuit in a 90 nanometer CMOS (complementary metal-oxide-semiconductor transistor) process. The static discharge clamping circuit mainly solves the problem of great RC (resistance-capacitance) network static electricity leakage in the static discharge clamping circuit in the existing 90 nanometer CMOS process. The circuit comprises an RC network, a phase inverter, a clamping device and a bias circuit, wherein the bias circuit provides bias voltage Vb of a grid electrode for a PMOS (P-channel metal oxide semiconductor) tube Mp3 in the RC network, as the bias voltage Vb is high voltage, the source grid voltage of the PMOS tube Mp3 is reduced, the equivalent resistance is increased, and the static electricity leakage of the RC network is reduced; during the static discharge, after the bias RC network detects the static discharge, the detection voltage CLK is input into the phase inverter, after the phase inverter receives the detection voltage, the grid electrode driving voltage Vg is input into the clamping device for starting the clamping device, and the static discharge charges are discharged. The static discharge clamping circuit has the advantages that the energy efficiency of the static discharge clamping circuit in the 90 nanometer CMOS process is improved, and the static discharge clamping circuit can be used for the design of integrated circuits.

Owner:XIDIAN UNIV

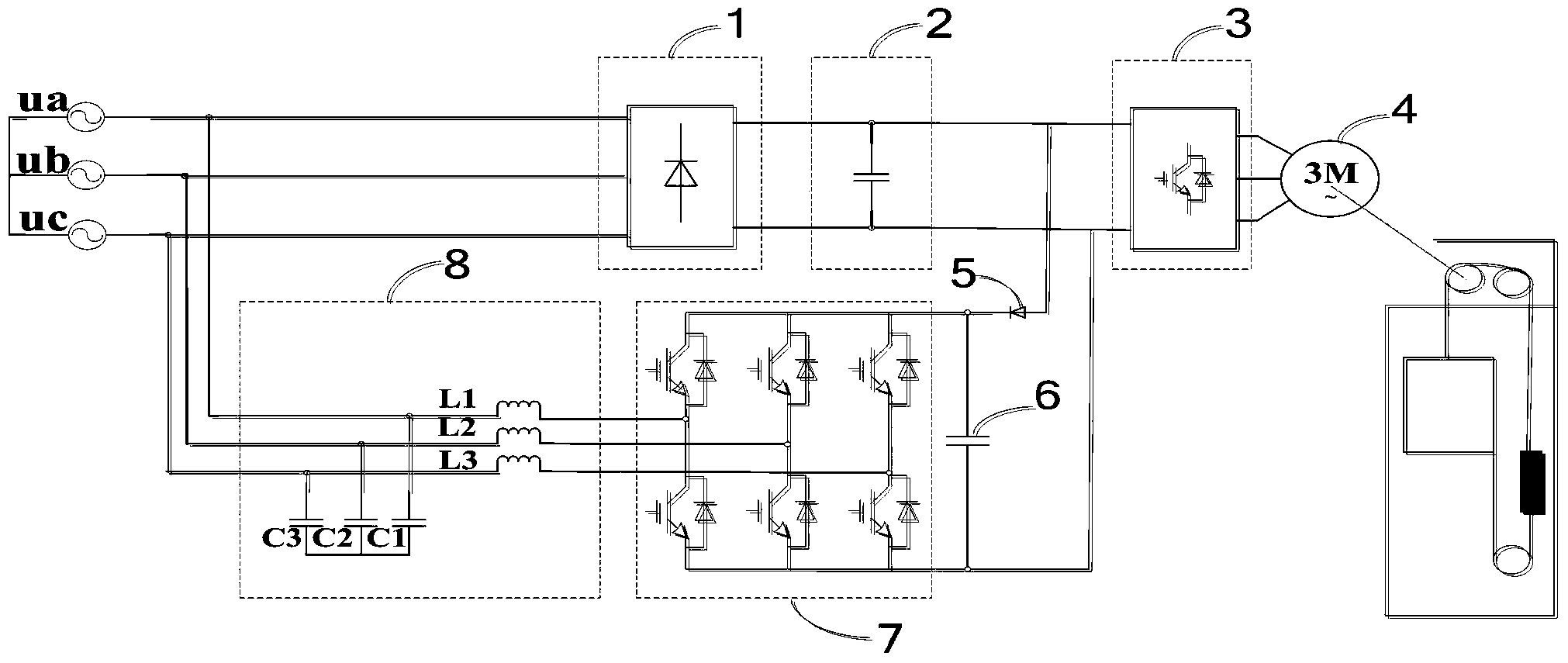

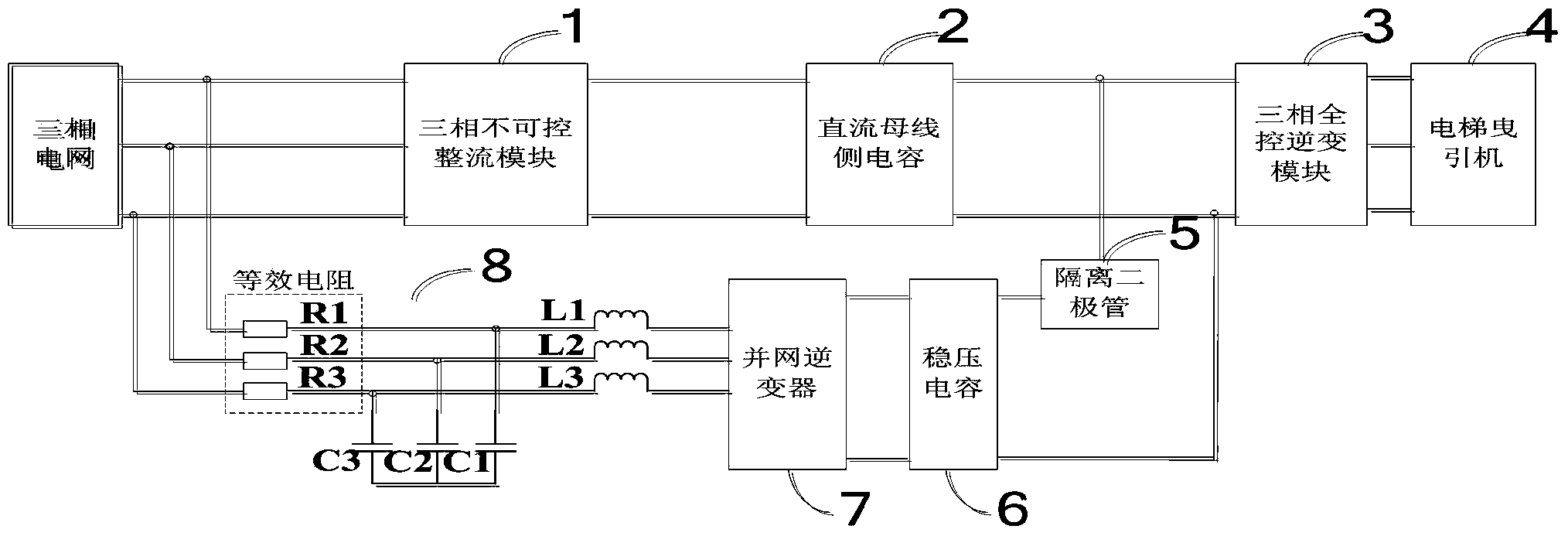

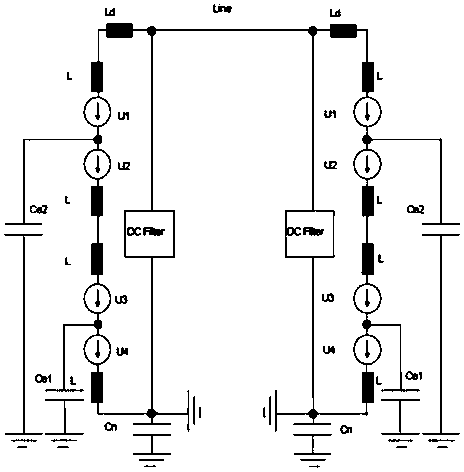

LC filter elevator energy feedback device

InactiveCN103944184AEffective filteringSimple parameter designSingle network parallel feeding arrangementsHarmonic reduction arrangementCapacitanceFull bridge

The invention relates to an LC filter elevator energy feedback device which comprises a three-phase uncontrollable rectifier module, a direct-current bus side capacitor, a three-phase full-bridge controllable inverter module and an elevator traction machine, wherein the three-phase uncontrollable rectifier module, the direct-current bus side capacitor, the three-phase full-bridge controllable inverter module and the elevator traction machine are sequentially connected. The three-phase full-bridge controllable inverter module is connected with a three-phase power grid through a grid -connected inverter at the same time. The device is characterized in that an LC filter, an isolating diode and a voltage stabilizing capacitor are further included, the LC filter is connected between the output end of the grid-connected inverter and the three-phase power grid, the voltage stabilizing capacitor is connected with the input end of the grid-connected inverter in parallel, the P electrode of the isolating diode is connected with the positive pole of the direct-current bus side capacitor, and the N electrode of the isolating diode is connected with the positive pole of the voltage stabilizing capacitor. According to the elevator energy feedback device, the characteristic that a low-power elevator system with the power of 7.5 KW or below has large circuit equivalent resistance is fully used, oscillation can be effectively prevented through network side equivalent resistance, grid-connected current high harmonics are filtered, extra loss is not generated, system stability is high, and social benefits and economic benefits are remarkable.

Owner:TIANJIN XINBAOLONG ELEVATOR GRP

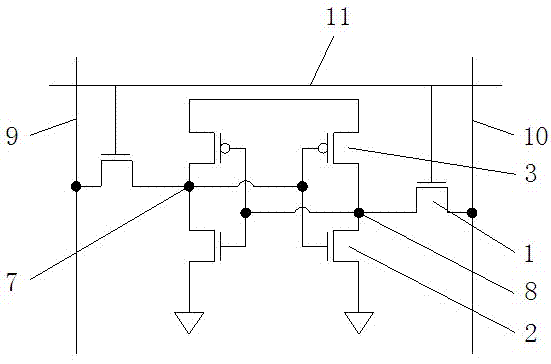

Electron static discharge (ESD) clamping circuit and integrated circuit

ActiveCN107863339AIncrease the equivalent resistanceReduce the capacitance CTransistorSolid-state devicesIntegrated circuitEngineering

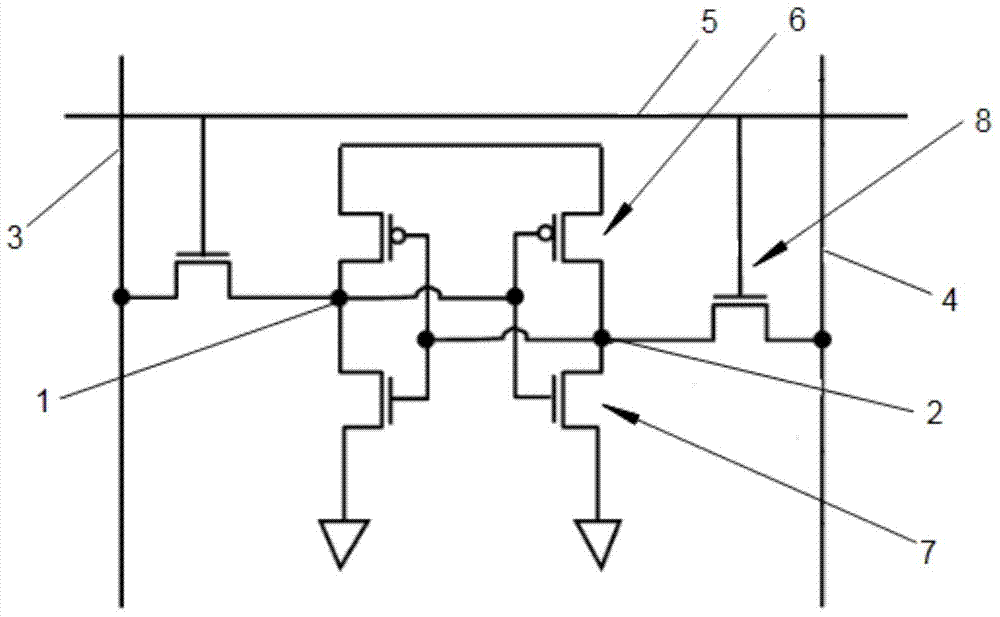

The invention discloses an electron static discharge (ESD) clamping circuit and an integrated circuit. The clamping circuit comprises a capacitor, a resistor, a first P-type transistor, a second P-type transistor, a third P-type transistor, a first N-type transistor, a second N-type transistor, a third N-type transistor, a fourth N-type transistor, a fifth N-type transistor and a sixth N-type transistor, wherein a source of the second N-type transistor is connected with a drain of the third N-type transistor, the capacitor is connected between the drain of the second N-type transistor and a power supply, a gate of the second N-type transistor is connected with the drain of the second N-type transistor, a source of the third N-type transistor is connected with ground, and a gate of the third N-type transistor is connected with a drain of the third N-type transistor. With the circuit provided by the invention, the technical problem of excessively large occupied layout area of the clamping circuit for electrostatic protection in the prior art is solved, and the technical effect of reducing the layout area is achieved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

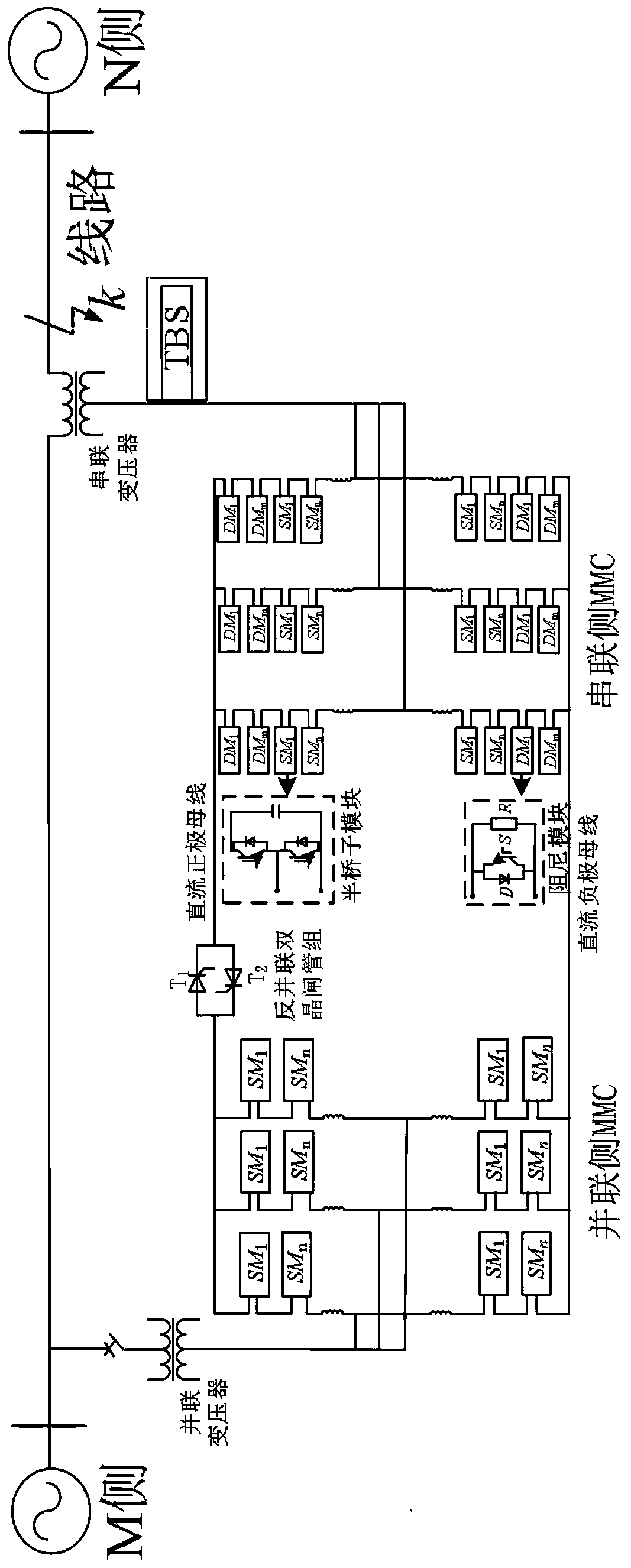

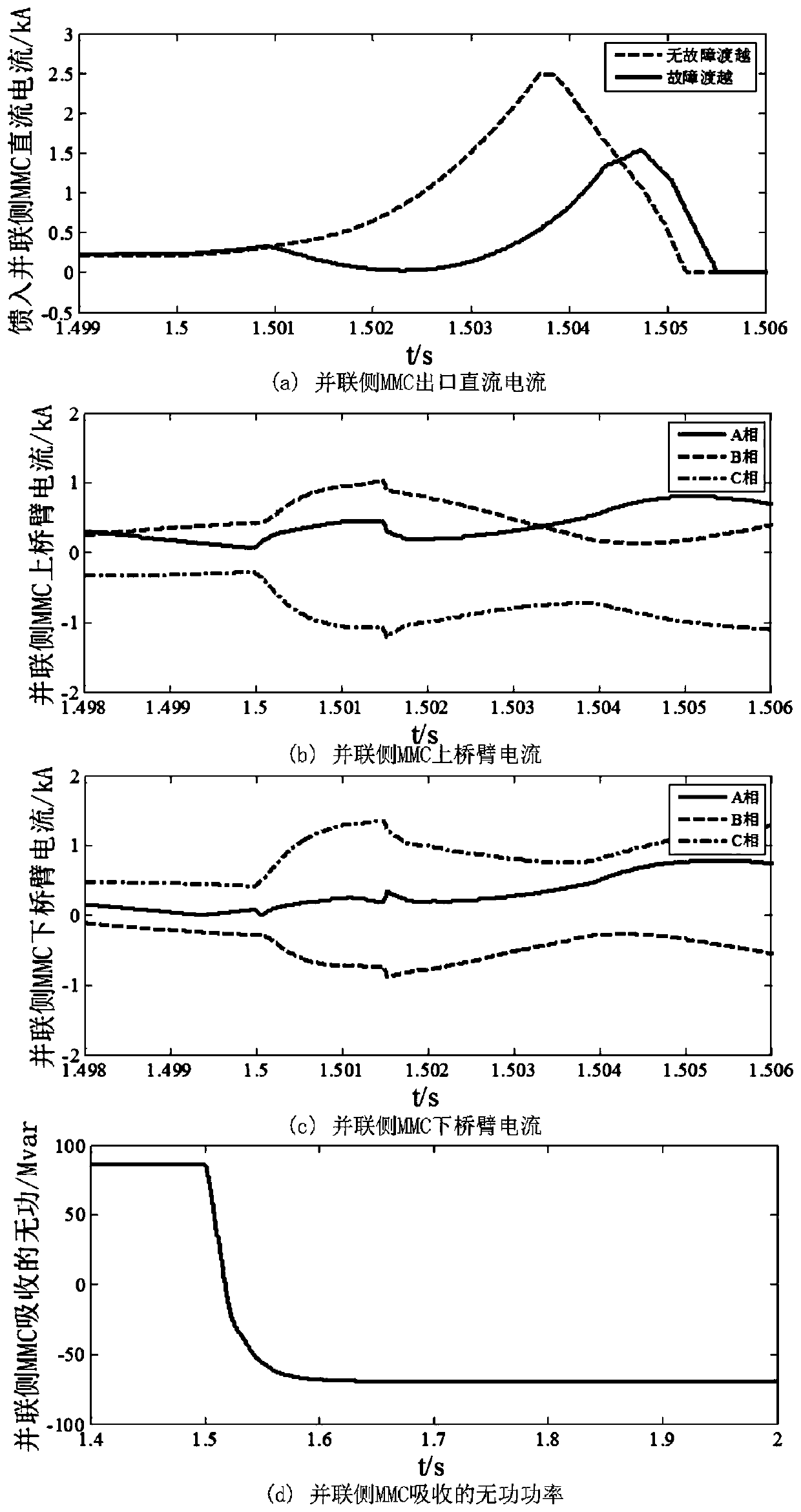

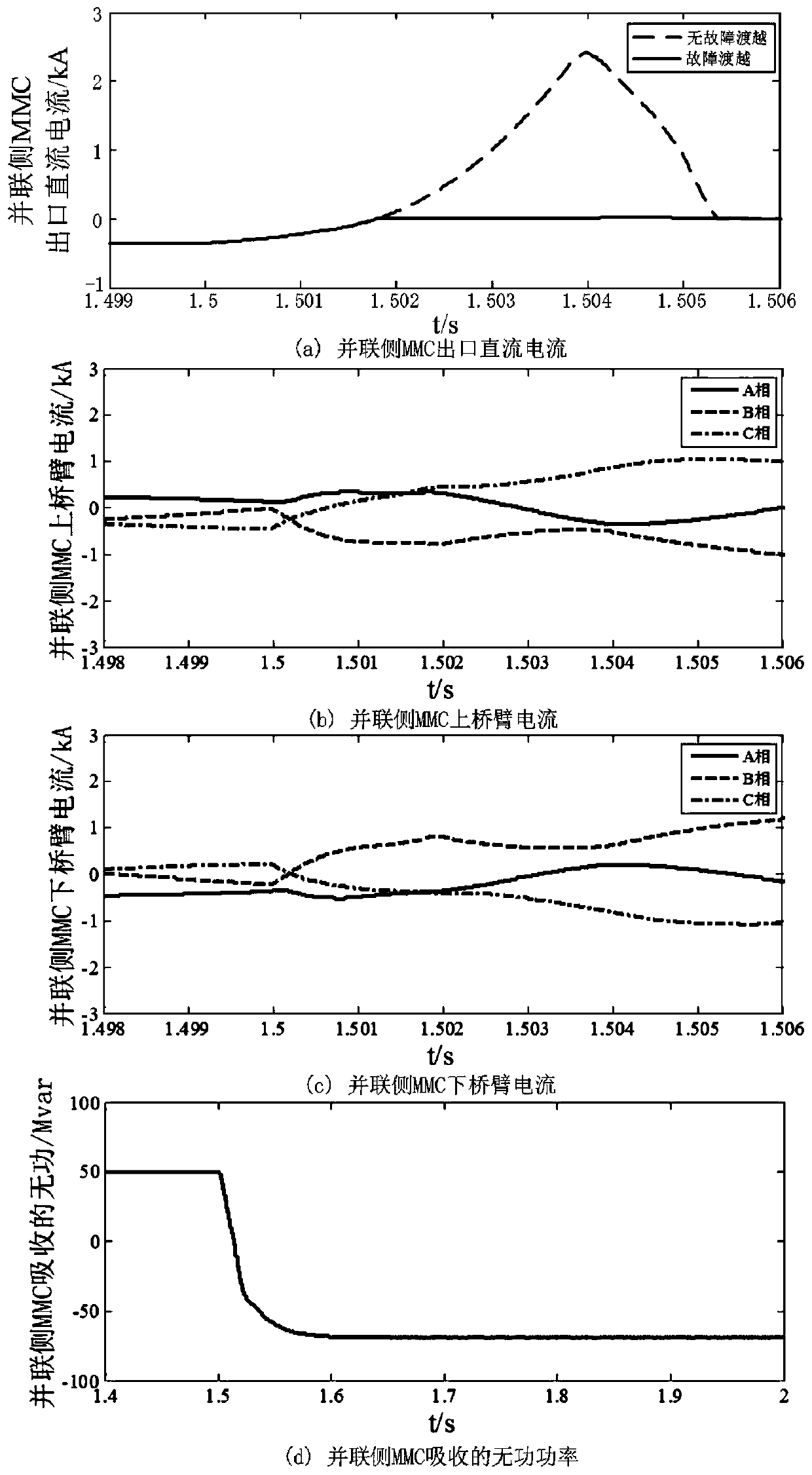

UPFC fault transition device and method based on additional damping resistor

ActiveCN111313407AIncrease the equivalent resistanceGuaranteed safe operationFlexible AC transmissionReactive power adjustment/elimination/compensationConvertersCut-off

The invention discloses a UPFC fault transition device and method based on an additional damping resistor. The MMC-UPFC fault transition is realized through the series connection of an anti-parallel double-thyristor group at a DC positive bus and the addition of a damping module at an MMC bridge arm at a series side. When an alternating current system has a short-circuit fault, the fault current is coupled to the valve side through the series transformer and the series side MMC is locked, When the active power transmission direction between the UPFC normal operation converters is from the series side to the parallel side, the series side MMC damping module IGBT is locked, the damping resistor is inputted, the fault current of the series side MMC fed into the direct current bus is inhibited, and the parallel side MMC cannot be locked in an overcurrent mode; when the active power transmission direction between the UPFC normal operation converters is from the parallel side to the series side, the anti-parallel double-thyristor group automatically cuts off the reverse fault current of the DC bus, the MMC at the parallel side is isolated from the MMC at the series side, and the UPFC isswitched to the STATCOM mode, thereby providing reactive power support for the bus voltage of the system after the fault, and facilitating the safe operation of the power system after the fault.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

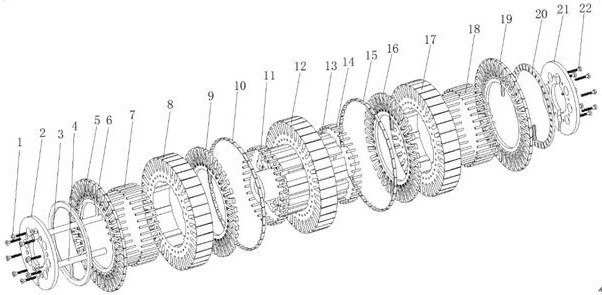

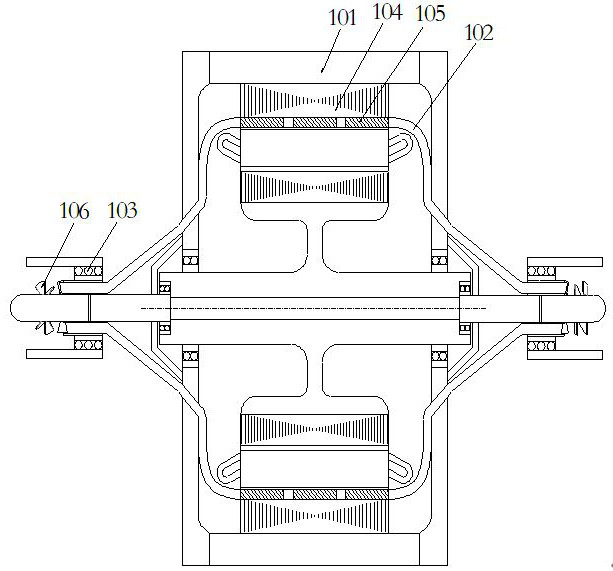

Water cooling structure of axial segmentation inner stator of outer rotor hub motor

InactiveCN113014040AReduce temperature riseLow failure rateMagnetic circuit stationary partsCooling/ventillation arrangementThermodynamicsElectric machine

The invention relates to the technical field of hub motors, in particular to a water cooling structure of an axial segmentation inner stator of an outer rotor hub motor. The structure comprises the axial segmentation inner stator, a radial radiation type waterway cooling disc, an axial connection cooling pipe, a stator bracket and a fastening pressure disc. According to the present invention, the stator adopts an axial segmentation structure, the radial radiation type waterway cooling discs are arranged between every two adjacent blocks, cooling water cools the segmented stator through the radial radiation type waterway cooling discs and the axial connection cooling pipes, waterways can make full contact with the wall face of a stator iron core, and heat dissipation is improved; the temperature rise of the stator iron core and the winding is low, so that the insulation aging acceleration and even motor burnout caused by too high temperature of the stator core and the winding are avoided, and an outer rotor permanent magnet synchronous hub motor works in a safe and efficient range. The stator core segmented structure can also significantly reduce the eddy current loss of the stator core and reduce the heat generation.

Owner:HARBIN UNIV OF SCI & TECH

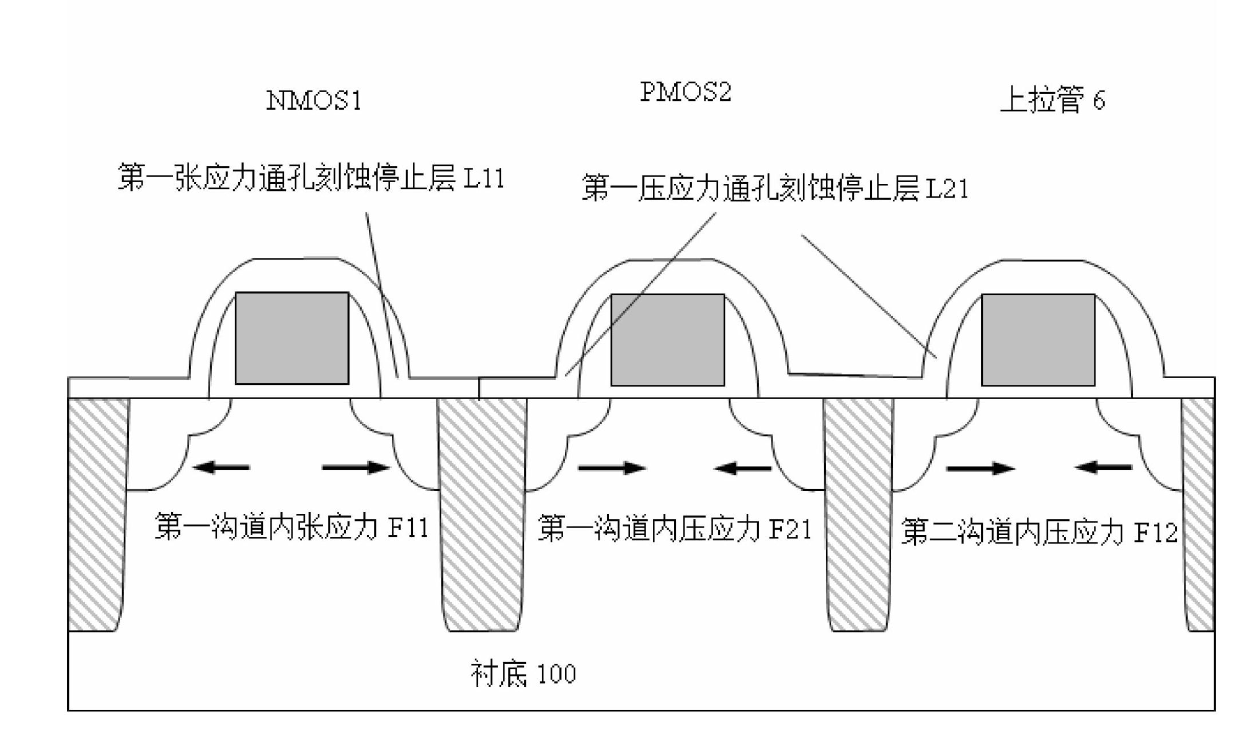

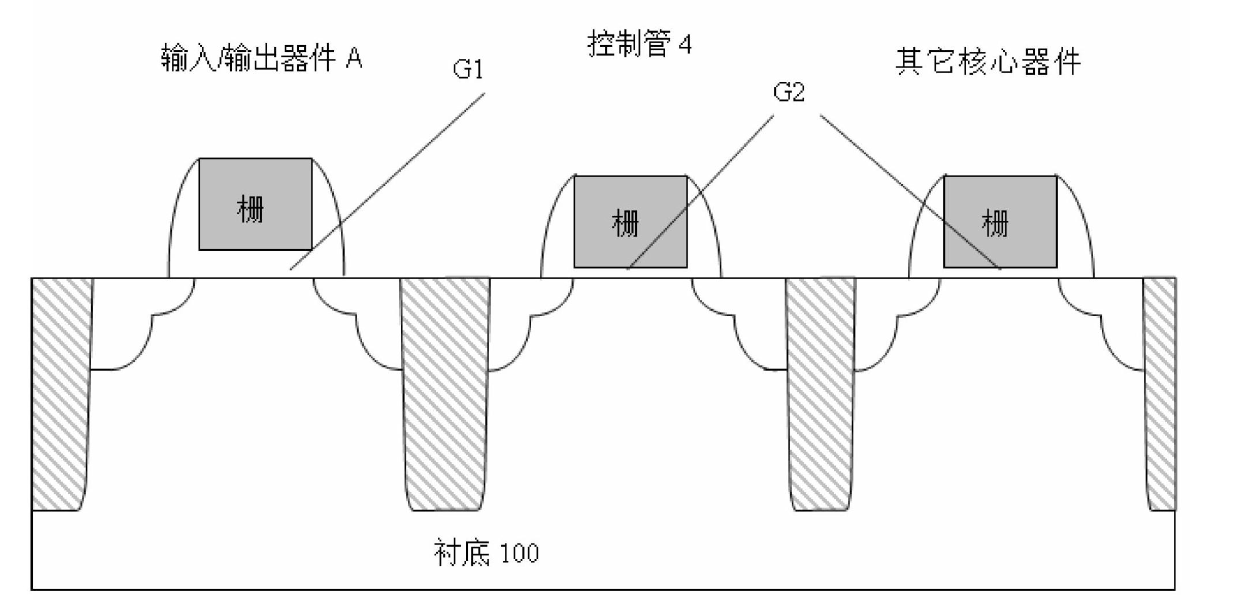

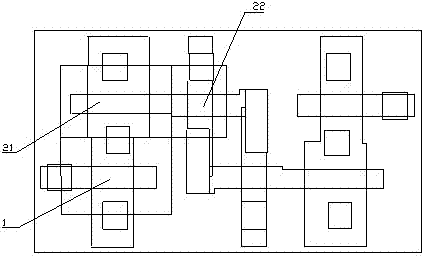

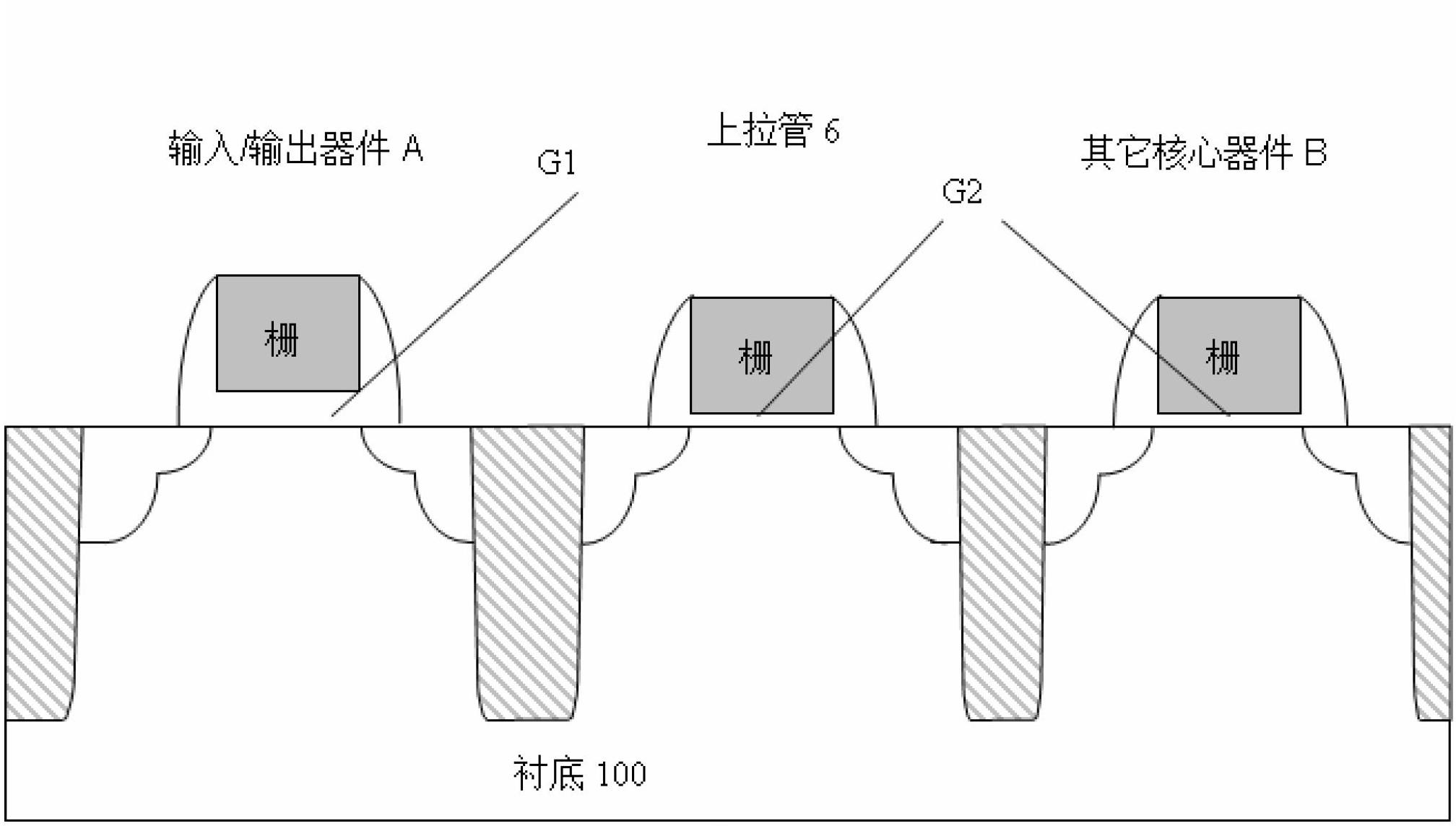

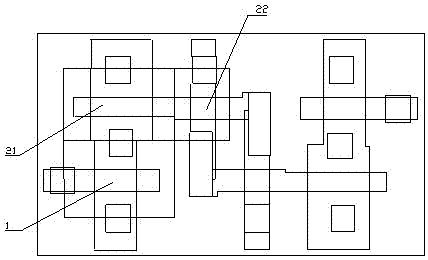

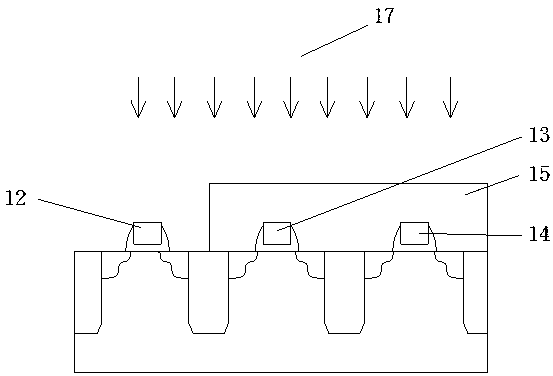

Method for improving write margin of static random access memory

InactiveCN102637644AImprove write redundancyReduced hole mobilitySemiconductor/solid-state device manufacturingStatic random-access memoryRandom access memory

The invention provides a method for improving a write margin of a static random access memory, which comprises the following steps: when a dual-stress through hole etch stop layer stress processing is adopted, the areas of all NMOS (N-channel metal oxide semiconductor) devices are covered by a tensile-stress through hole etch stop layer; the areas of all PMOS (P-channel metal oxide semiconductor) devices except a pull up MOS area are covered by a pressure-stress through hole etch stop layer; the pull up MOS area is covered by the tensile-stress through hole etch stop layer; and therefore the pull up MOS area and the areas of the NMOS devices keep the tensile stress. In the preparation process of the static random access memory, when dual-stress through hole etch stop layer stress engineering is adopted, a through hole etch stop layer capable of generating tensile stress in channels is used for the pull up MOS area, so that hole mobility of the pull up MOS is lowered, the equivalent resistance of the pull up MOS is increased, and the write margin of the static random access memory is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

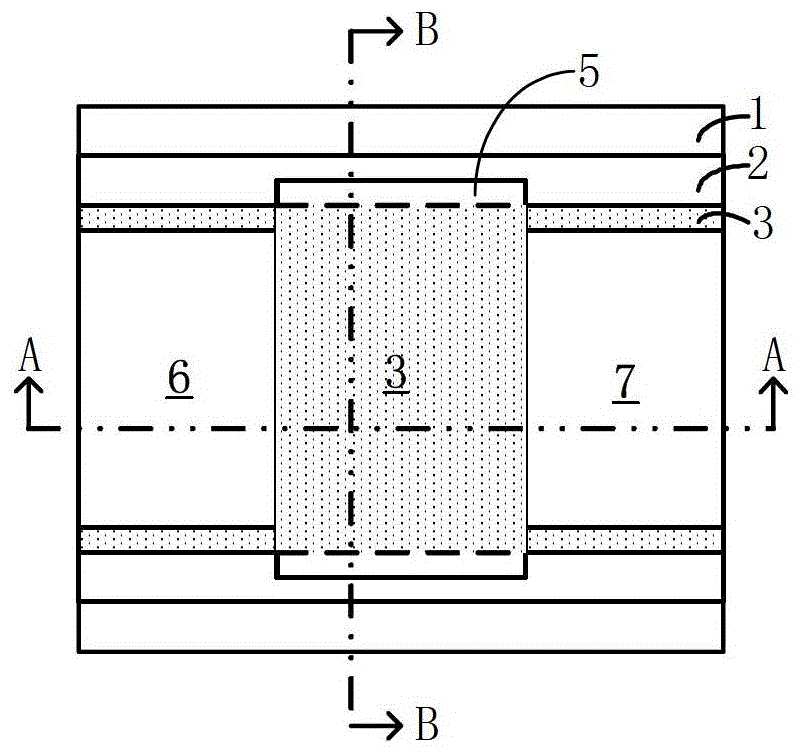

Method for improving read redundancy of static random access memory

ActiveCN102637691AIncrease the equivalent resistanceRaise the threshold voltageSolid-state devicesDigital storageStatic random-access memoryRandom access memory

The invention provides a method for improving the read redundancy of a static random access memory. The static random access memory comprises an input / output device and a core device, wherein the core device comprises a control tube device, the input / output device is used for inputting and outputting signals of a chip and a peripheral circuit, and the thickness of a gate oxide layer of the input / output device is more than that of a gate oxide layer of the core device. The method for improving the read redundancy of the static random access memory comprises: the thickness of a gate oxide layer of the control tube device is enabled to be more than that of gate oxide layers of the other core devices; and the thickness of the gate oxide layer of the control tube device can be enabled to be equal to the thickness of the gate oxide layer of the input / output device. For example, when the gate oxide layer of the control tube device is manufactured, the grown gate oxide layer for the input / output device is not removed, so that the control tube device finally uses the gate oxide layer of the input / output device as the gate oxide layer.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method for improving reading redundancy of static random access memory

InactiveCN102655124AIncrease the equivalent resistanceIncrease read redundancySemiconductor/solid-state device manufacturingStatic random-access memoryP channel

The invention discloses a method for improving the reading redundancy of a static random access memory. The method comprises the following steps of: providing a semiconductor substrate comprising an NMOS (N-channel metal oxide semiconductor) transistor, a PMOS (P-channel metal oxide semiconductor) transistor and a control tube; depositing a nitride film layer on the surface of a semiconductor device; and carrying out photolithography technique on the nitride film layers on the surfaces of the PMOS transistor and the control tube to remove the nitride film layers. According to the invention, the equivalent resistor of the control tube is increased while the existing process steps are not added so as to reduce the potential of a node inside the static random access memory during the reading process, thereby improving the reading redundancy of the random access memory.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

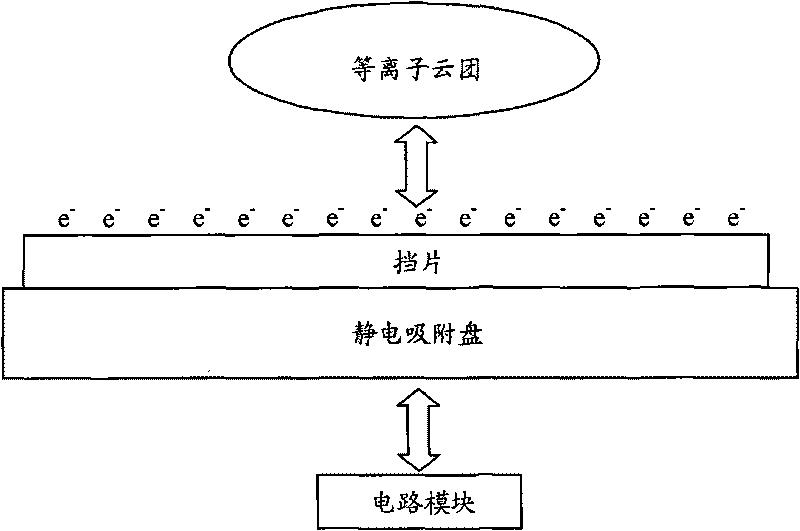

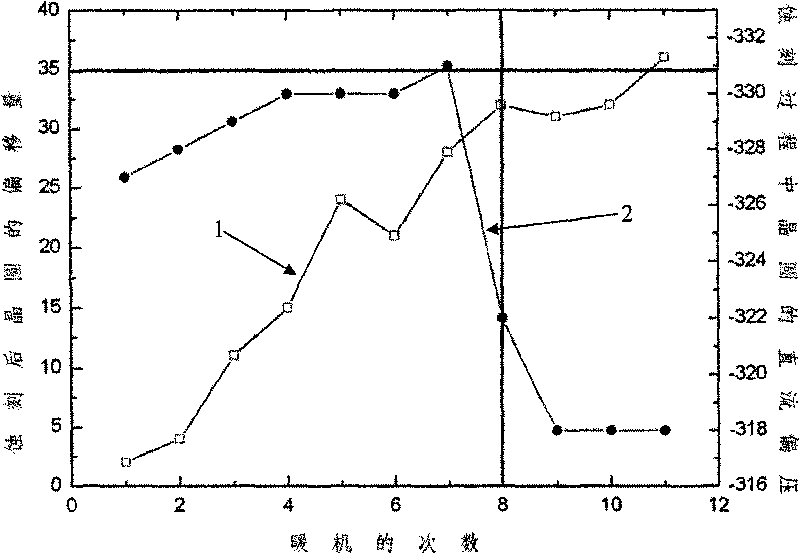

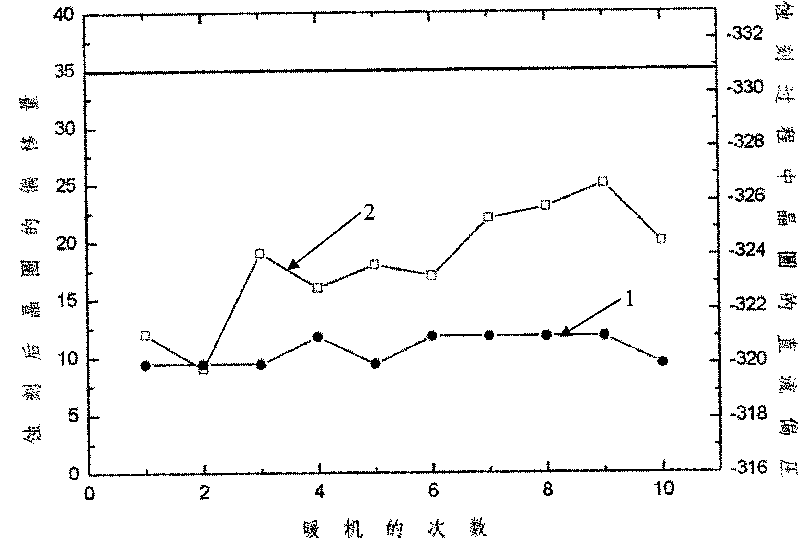

Catch for etching process and method for preventing catch from jumping

ActiveCN101697340AIncrease the equivalent resistanceWeight increaseSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingElectrical and Electronics engineeringJumping

The invention discloses a catch for an etching process, comprising a wafer substrate and a warming film layer arranged on the wafer substrate and an insulated film layer for preventing the jumping is arranged below the wafer substrate. The invention also discloses a method for preventing the catch from jumping, comprising the step that an insulated film layer for preventing the jumping is grown at the bottom of the wafer substrate of the catch. The invention has the advantages that equivalent resistance of the catch can be increased so as to weaken the vibration of the catch during discharge, thereby the jumping probability can be reduced; the insulated film layer is added and further the weight of the catch can be increased, thus the intensity for vibration can be reduced; in addition, the insulated layer can be repeatedly used and has the advantage of low cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

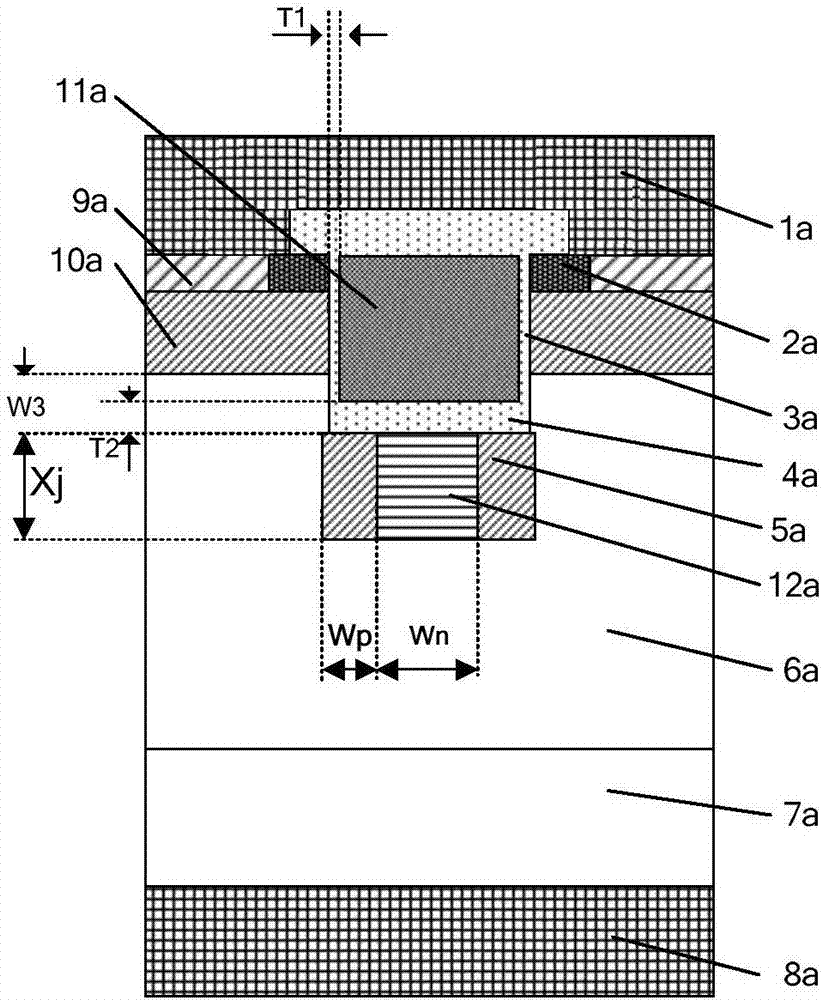

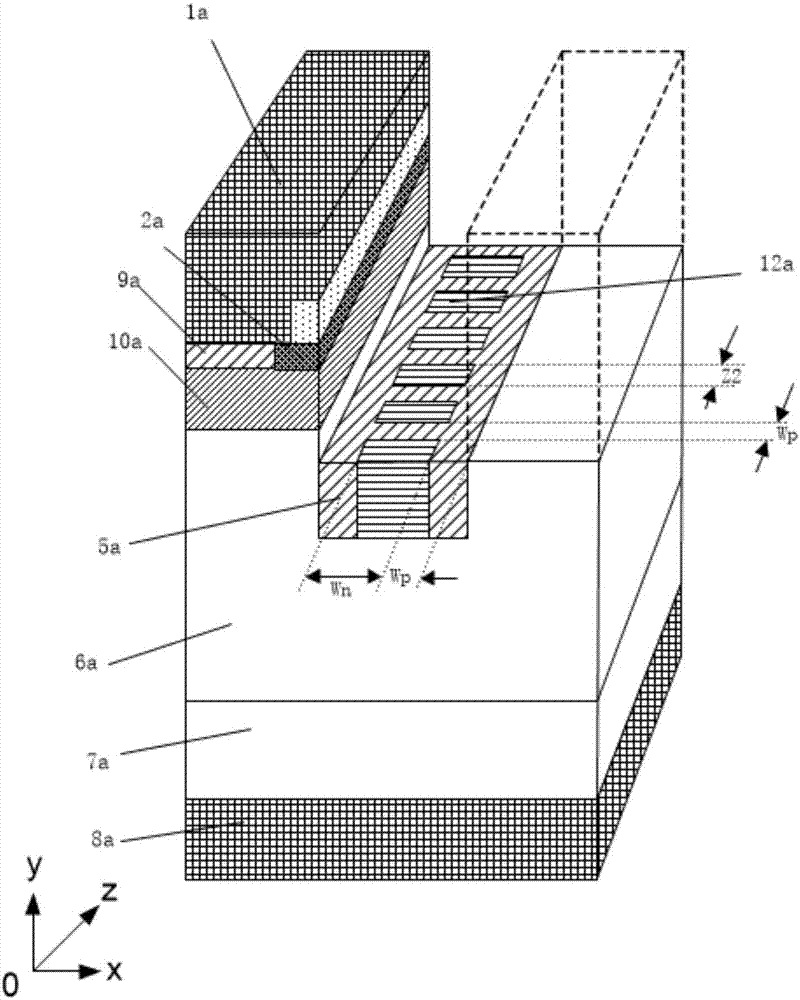

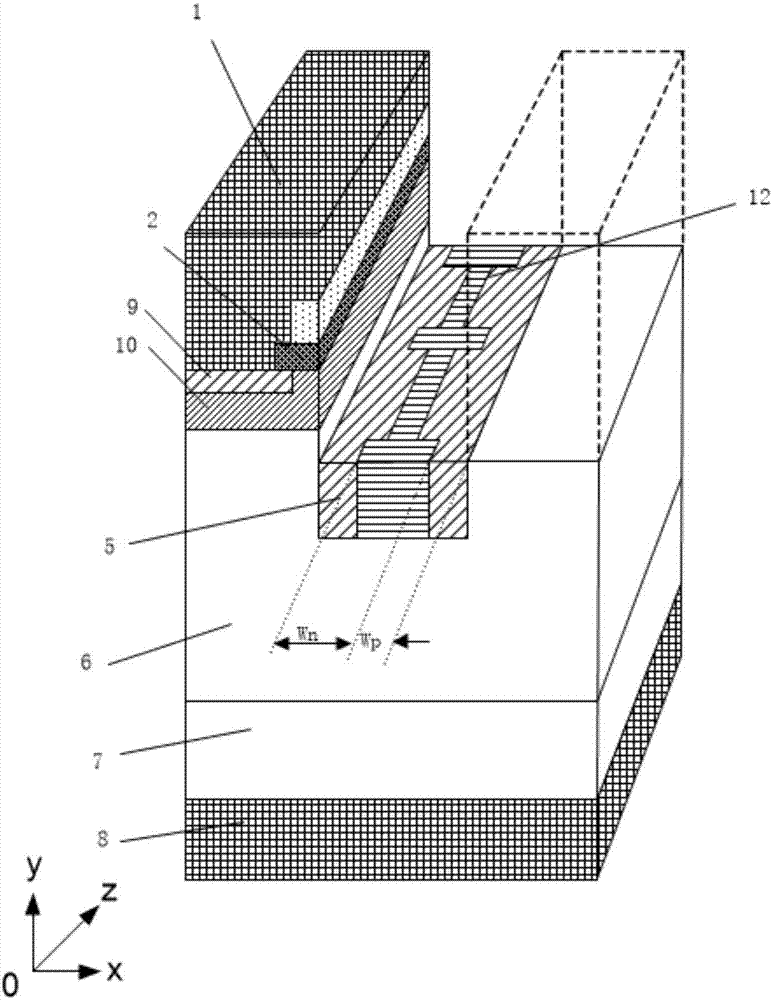

Trench gate metal oxide field effect transistor and manufacturing method thereof

PendingCN106876470AIncrease exhaustRun out fastSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSingle crystal

The invention relates to a trench gate metal oxide field effect transistor, which comprises a front metal electrode, a back metal electrode, an N-type single crystal substrate, an N-type epitaxial layer and a first P-type doping region, wherein a central part of the N-type epitaxial layer and a central part of the first P-type doping region are provided with a vertical trench, a first dielectric layer is arranged between the side wall of a grid electrode in the trench and the first P-type doping region, a second dielectric layer is arranged between the bottom of the grid electrode and the epitaxial layer, the first P-type doping region is provided with a first N-type doping region at the part close to the two sides of the trench, the first P-type doping region is further provided with a second P-type doping region at the part away from the two sides of the trench, the internal part of the epitaxial layer is further provided with a third P-type doping region and a second N-type doping region which are contacted with the lower part of the second dielectric layer, the third P-type doping region and the second N-type doping region are enabled to be mutually staggered and spaced, and a plurality of PN junction units are formed in the length direction and the thickness direction. According to the invention, parasitic capacitance between a grid electrode and a drain electrode of a low trench gate SiC MOSFET can be reduced, the electric field intensity at the bottom of the trench is reduced, and turn-on of a parasitic BJT (Bipolar Junction Transistor) is suppressed.

Owner:SHENZHEN BASIC SEMICON LTD

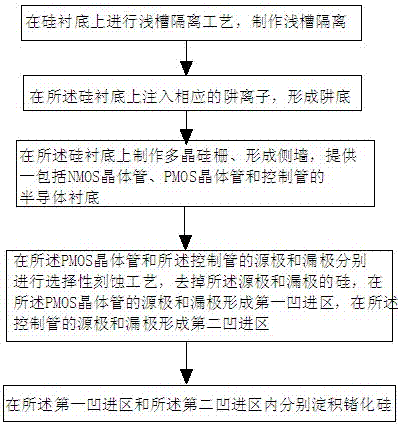

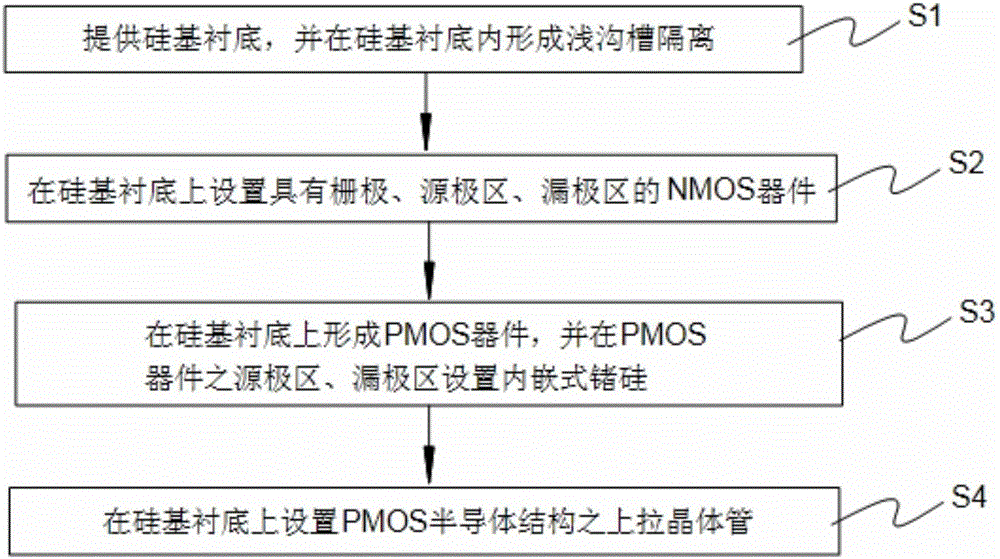

Method for improving writing-in redundancy rate of static random access memory

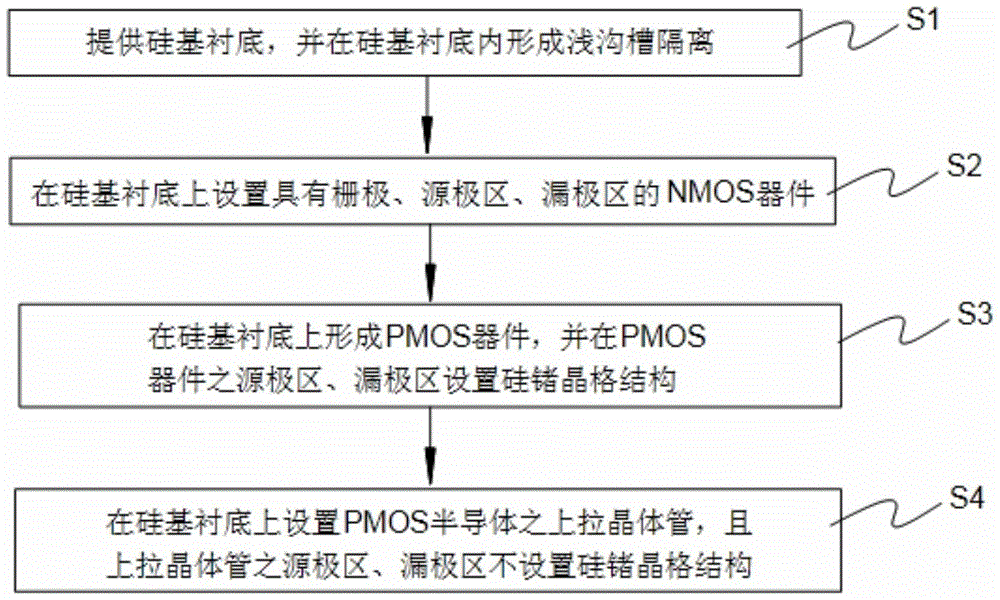

ActiveCN103579118AReduced hole mobilityIncrease the equivalent resistanceTransistorSemiconductor/solid-state device manufacturingStatic random-access memoryMemory effect

A method for improving the writing-in redundancy rate of a static random access memory comprises the first step of providing a silicon-based substrate and forming a shallow-channel isolator, the second step of forming an NMOS device and a PMOS device serving as an upwards-pull transistor, the third step of carrying out source-drain injection in source electrode areas and drain electrode areas of the NMOS device and the PMOS device serving as the upwards-pull transistor and depositing a silicon nitride protective layer, the fourth step of carrying out source-drain annealing process on the NMOS device and the PMOS device serving as the upwards-pull transistor, and the fifth step of etching and removing the silicon nitride protective layer. When a stress memory effect process photolithography mask is manufactured, the PMOS device area of the upwards-pull transistor and the NMOS device are covered; in the stress memory effect process, the upwards-pull transistor and the NMOS device are both covered with the silicon nitride protective layer, then the source-drain annealing process is carried out, the hole mobility of the upwards-pull transistor is reduced, and then the equivalent resistance of the upwards-pull transistor is increased; in the writing-in process, the electric potential of a second node is lowered and then the writing-in redundancy rate can be improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Trench isolation structure and forming method thereof, and semiconductor device and forming method thereof

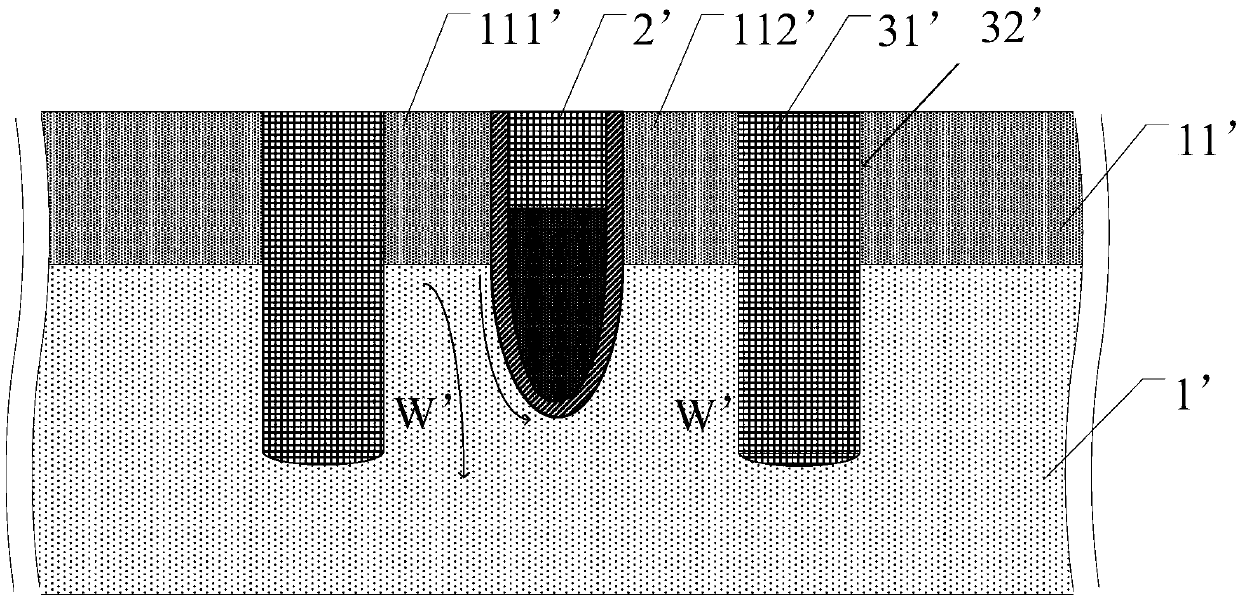

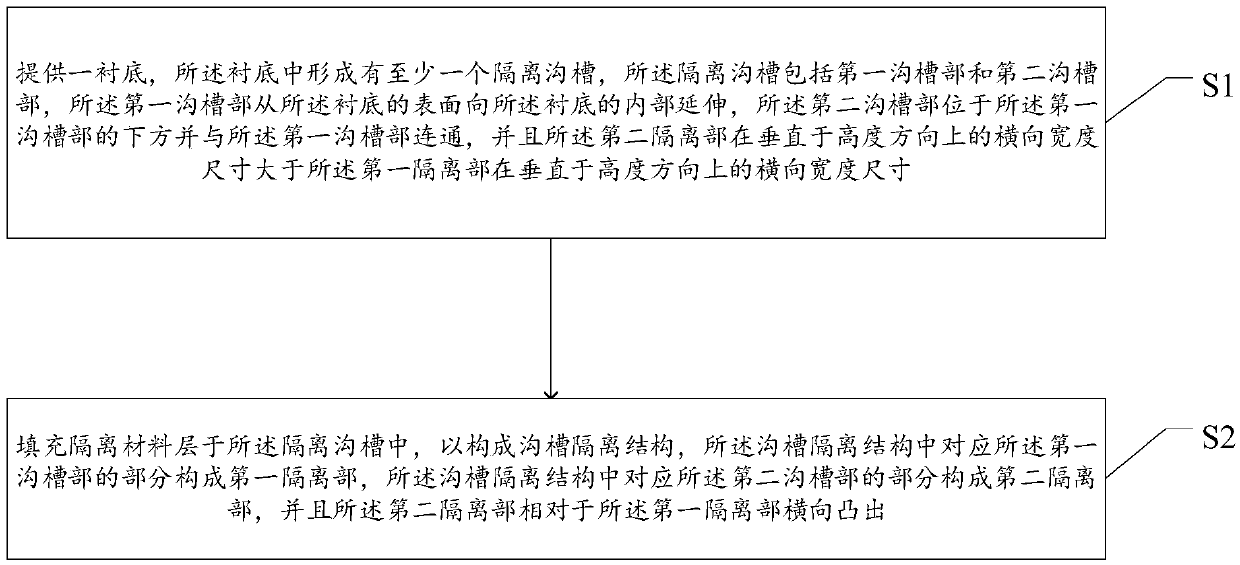

PendingCN110970347AIncrease storage capacityReduce areaSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

The invention provides a trench isolation structure and a forming method thereof, and a semiconductor device and a forming method thereof. The forming method of the trench isolation structure comprises the following steps: forming a trench isolation structure in a substrate, and defining an active region through the trench isolation structure, wherein the trench isolation structure is provided with a first isolation part and a second isolation part which are connected with each other, the second isolation part is located below the first isolation part, and the transverse width of the second isolation part in the direction perpendicular to the height direction is larger than the transverse width of the first isolation part in the direction perpendicular to the height direction, so that thesecond isolation part is enabled to protrude transversely relative to the first isolation part, so that the area of a leakage region is reduced, the equivalent resistance on a leakage path is increased, a leakage current is reduced, and the storage performance of the semiconductor device is improved.

Owner:CHANGXIN MEMORY TECH INC

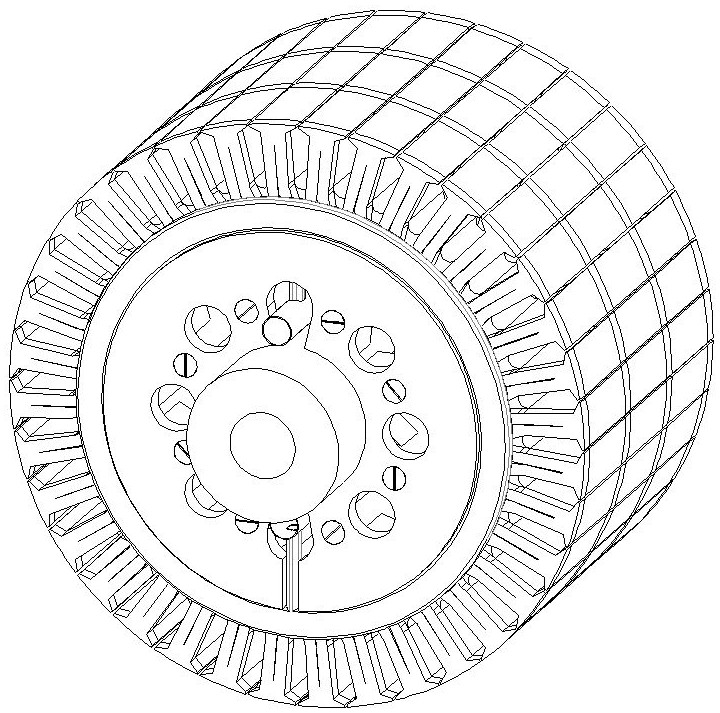

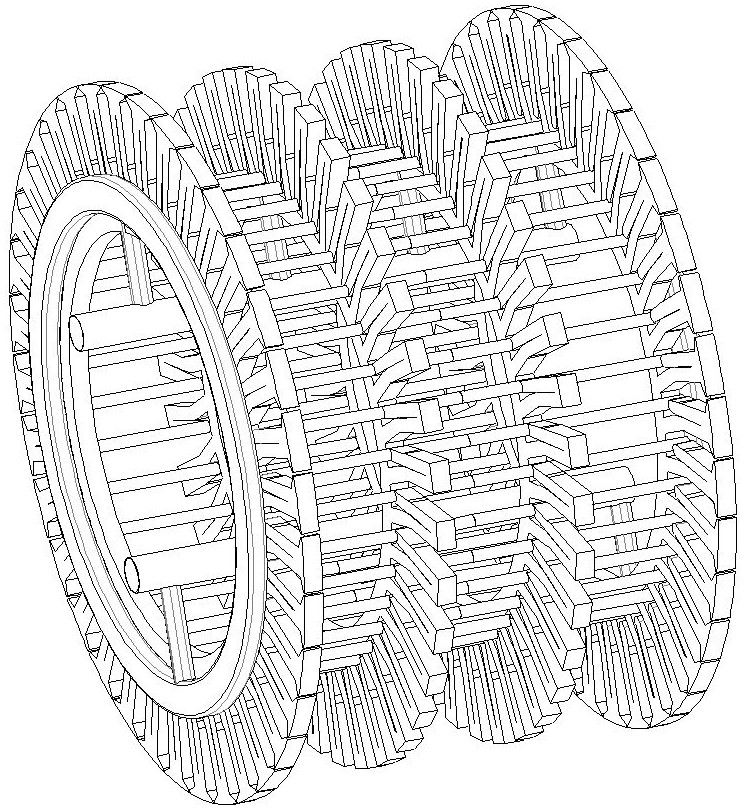

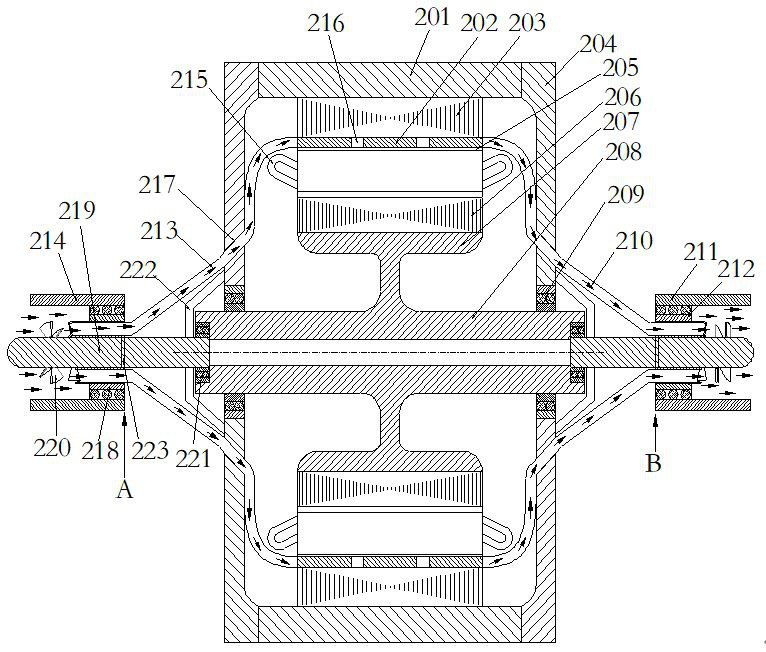

Outer rotor water cooling structure of permanent magnet synchronous hub motor

InactiveCN112564422AAvoid magnetic degradationAvoid irreversible demagnetizationMagnetic circuit rotating partsCooling/ventillation arrangementImpellerElectric machine

The invention relates to the technical field of hub motors, in particular to an outer rotor water cooling structure of a permanent magnet synchronous hub motor, which comprises an outer rotor permanent magnet synchronous hub motor, an outer rotor waterway cooling pipe, a waterproof bearing and an axial flow impeller, the two ends of the outer rotor waterway cooling pipe are welded between the inner ring of the waterproof bearing and the surface of an axial-flow impeller shaft and are tightly attached to the periphery of motor permanent magnets and the inner wall of a rotor core through end covers. When the hub motor rotates, the outer rotor waterway cooling pipe and the axial flow impeller are driven to rotate, and cooling water enters the outer rotor waterway cooling pipe through the axial flow impeller to cool the permanent magnets. A rotor adopts water internal cooling, the temperature rise of the permanent magnets is low, the reduction of magnetic performance and irreversible demagnetization of the permanent magnets due to over-high temperature are avoided, and the motor is reliable in operation. The permanent magnet adopts an axial segmented structure, and omega-shaped coolingwater pipes are arranged between every two adjacent permanent magnets, so that waterways can be in full contact with the permanent magnets and the inner wall of the rotor, and the heat dissipation isimproved; the permanent magnet segmented structure can significantly reduce the eddy current loss of the permanent magnets and reduce heat generation.

Owner:HARBIN UNIV OF SCI & TECH

Low leakage current resetting device applied to capacitive integrating weak current measuring circuit

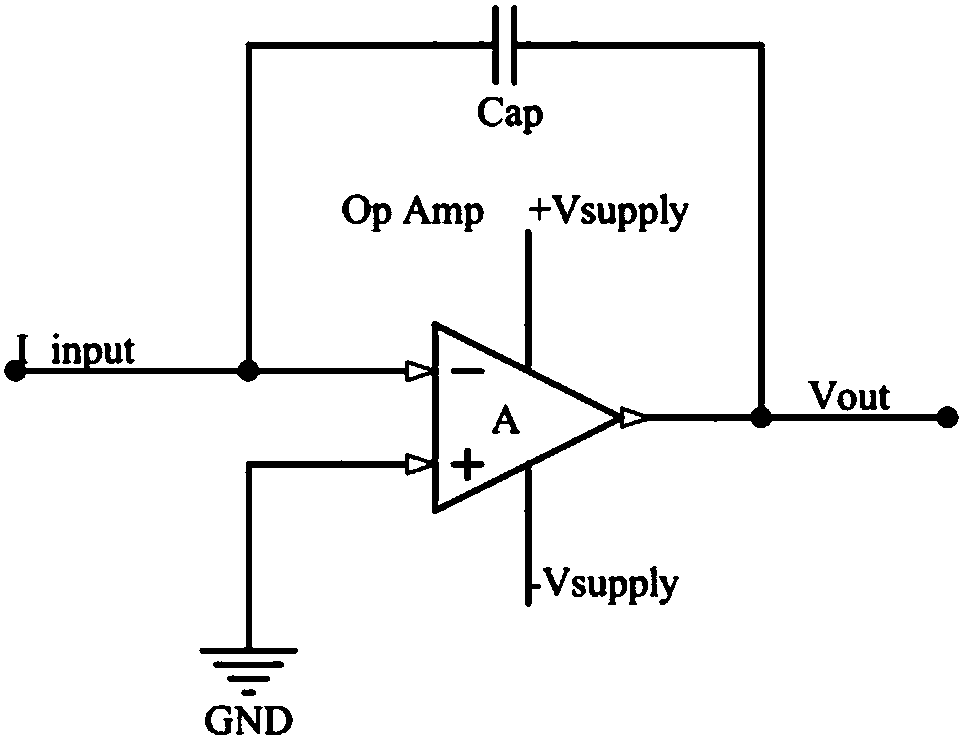

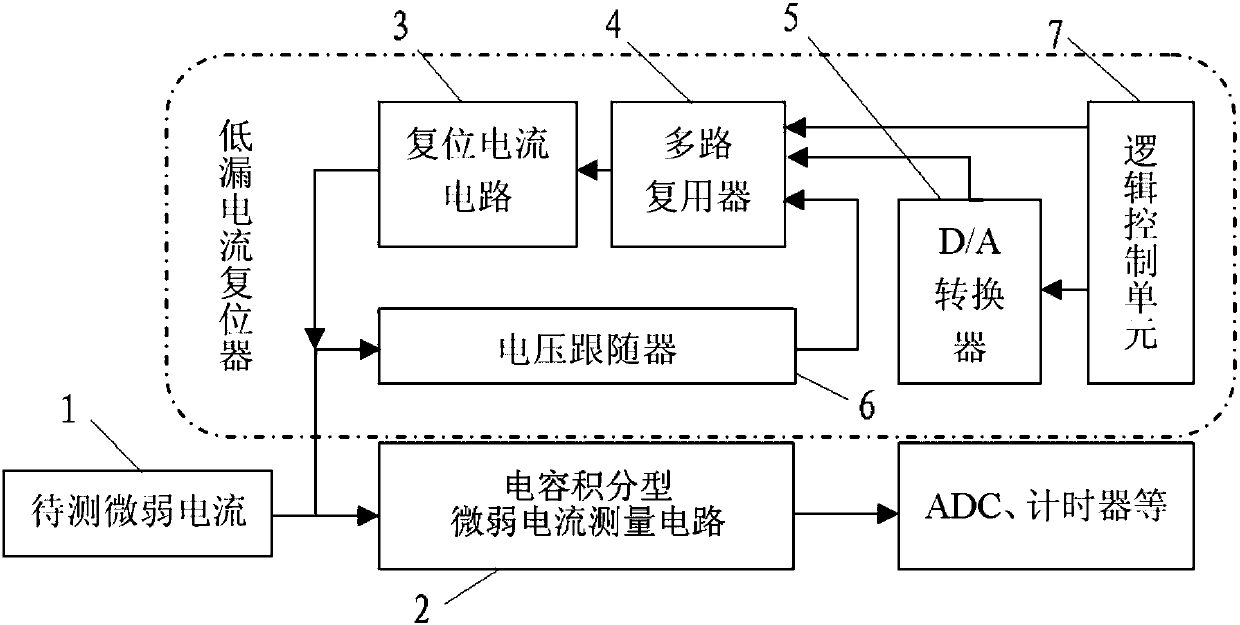

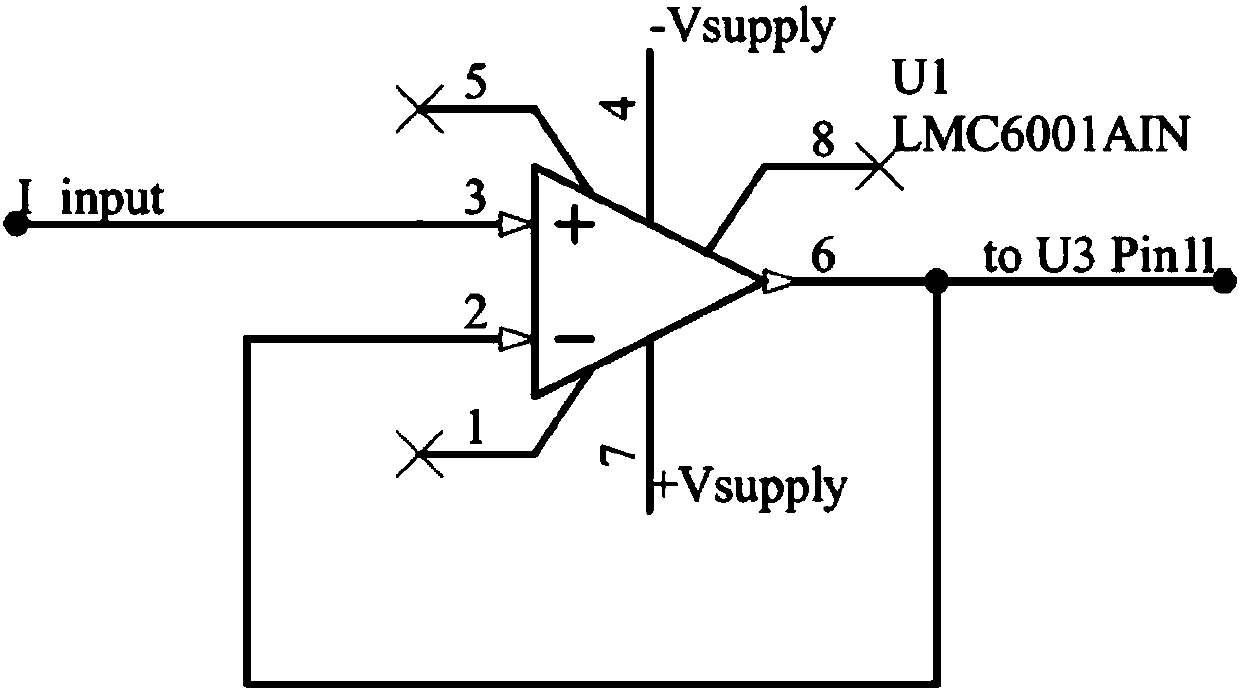

PendingCN108037341AImprove performance indicatorsLow measurement limitVoltage/current isolationMeasurement using digital techniquesLower limitCapacitance

The invention belongs to the technical field of weak current measurement, and particularly relates to a low leakage current resetting device applied to a capacitive integrating weak current measuringcircuit. The resetting device is connected with a capacitance integrating weak current measuring circuit (2) used for measuring weak current to be measured (1). The resetting device comprises a resetcurrent circuit (3), a multiplexer (4), a D / A converter (5), a voltage follower (6) and a logic control unit (7). The voltage follower (6) can copy the voltage of the weak current to be measured (1) as the turn-off voltage of the reset current circuit (3). The D / A converter (5) can provide turn-on voltage with adjustable polarity and magnitude for the reset current circuit (3). The resetting device further comprises a logic control unit (7) which controls the multiplexer (4) to select to output turn-off voltage or turn-on voltage, and controls the polarity and magnitude of the turn-on voltageoutput by the D / A converter (5). According to the invention, the measurement lower limit and the minimum resolution of the capacitive integrating weak current measuring circuit system can be greatly improved.

Owner:CHINA INSTITUTE OF ATOMIC ENERGY

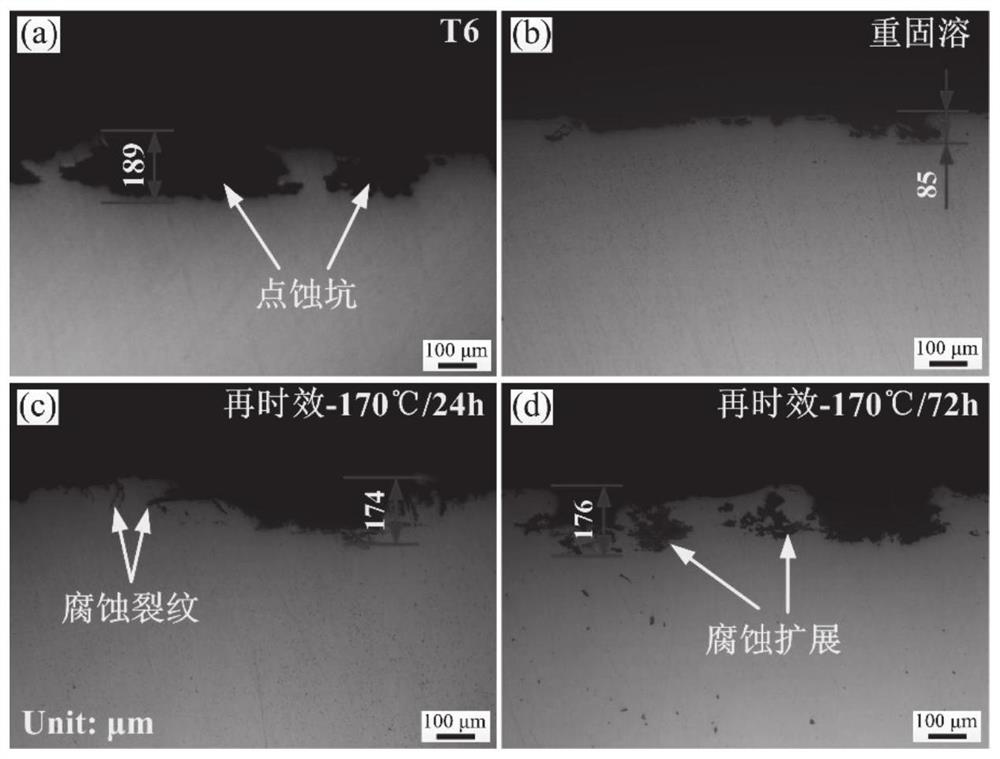

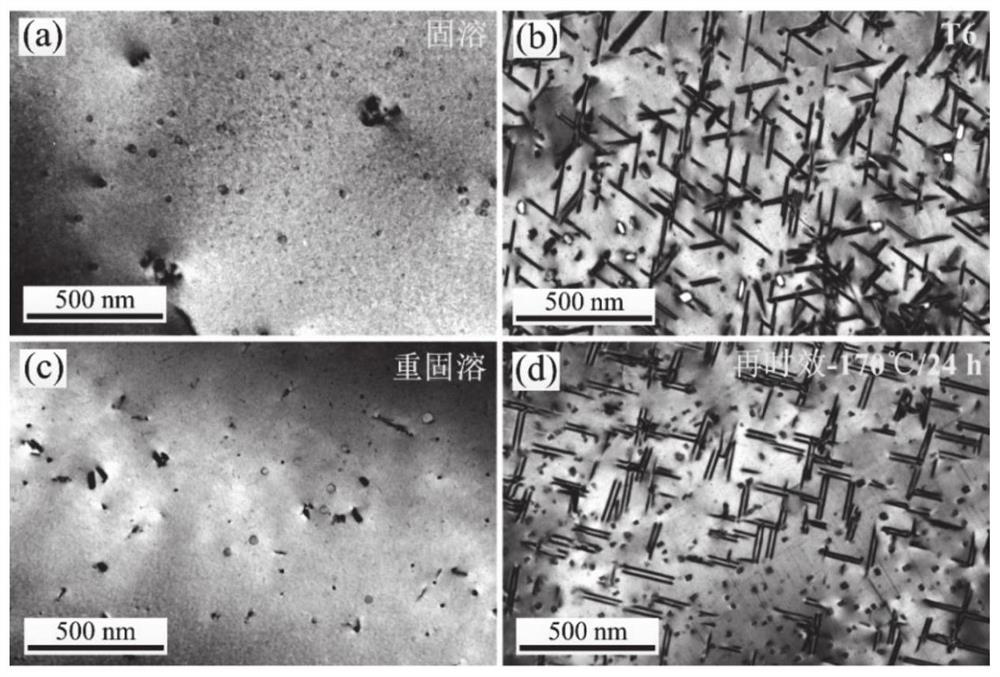

Heat treatment method for pre-aging, re-solid-solution and re-aging of Al-Cu-Li alloy

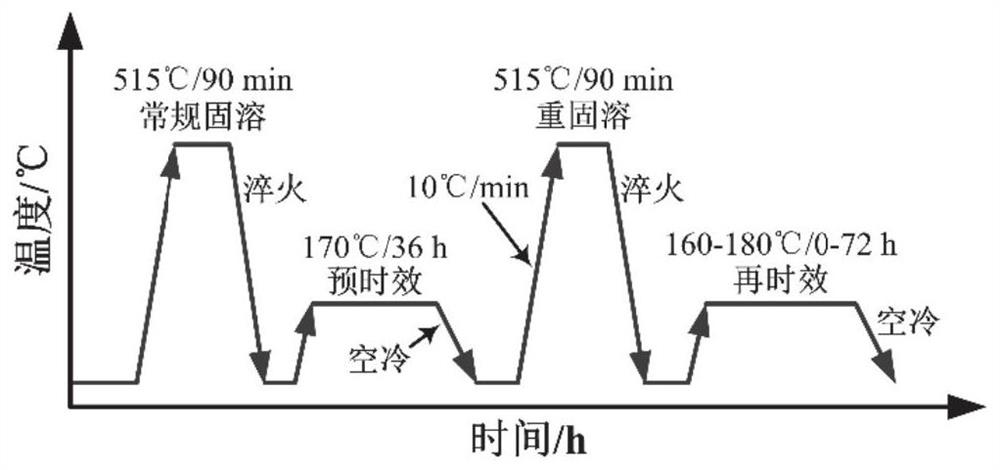

ActiveCN112281092AReduce the effect of strengtheningHigh strengthSolution treatmentHeat conservation

The invention discloses a heat treatment method for pre-aging, re-solid-solution and re-aging of an Al-Cu-Li alloy, belongs to the field of material heat treatment, and aims to perform conventional solid-solution, pre-aging, re-solid-solution and re-aging treatment on an Al-Cu-Li alloy extruded plate by controlling a heat treatment process system and parameters thereof. The conventional solid solution and re-solid solution treatment temperature is 515 + / -10 DEG C, heat preservation is performed for 60-90 min, then water quenching is performed, and the quenching transfer time is shorter than 5s. The pre-aging and re-aging treatment temperature is 160-180 DEG C, heat preservation is performed for 24-48 hours, and the product is taken out for air-cooling. The strength of the alloy can be reduced through re-solid-solution treatment, the plasticity of the alloy is improved, and correction and reprocessing processes are facilitated. The re-aging treatment can effectively regulate and control the variety, density and distribution of precipitated phases, thereby enhancing the strength of the alloy. In addition, due to coarsening of discontinuous grain boundary precipitated phases in the alloy and increasing of the copper content, on the premise that the strength of the alloy is basically not lost, the stress corrosion resistance, the intergranular corrosion resistance and the electrochemical corrosion resistance are improved, and the plasticity of the alloy is improved. The process is simple and feasible and is not limited by the thickness of the plate.

Owner:SHANDONG UNIV

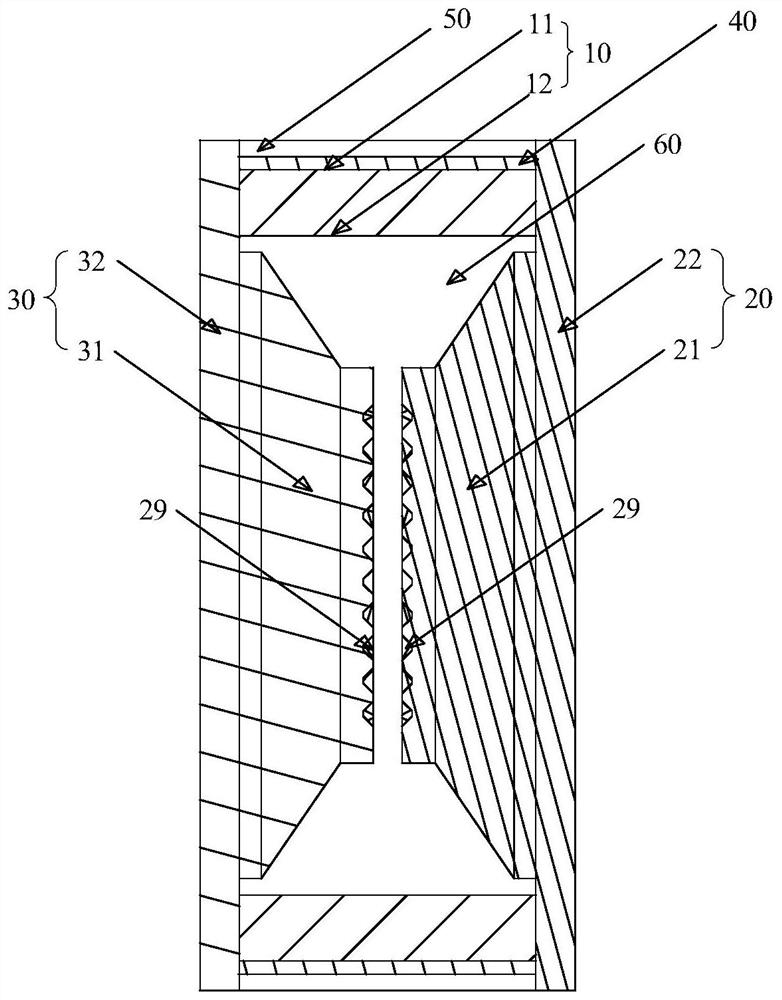

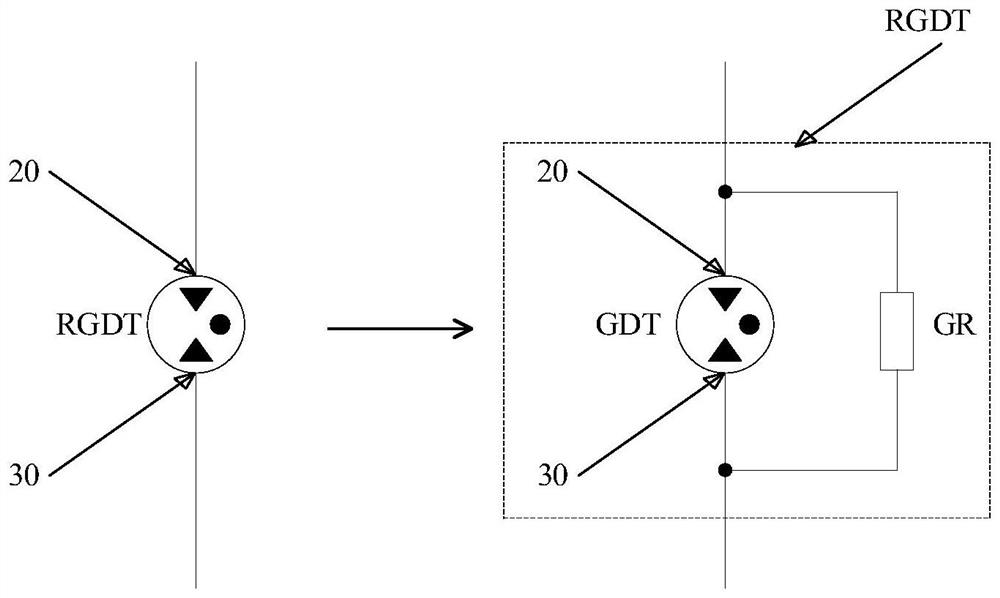

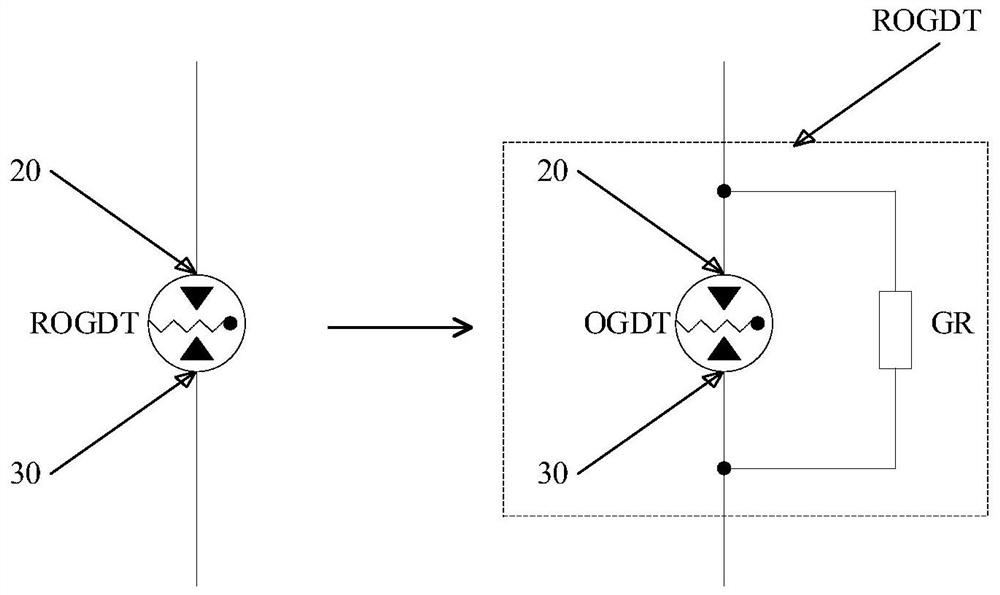

Band-stop gas discharge tube, combined lightning protection device, protection circuit and electronic equipment

PendingCN111786372AIncrease the equivalent resistanceIncrease partial pressureEmergency protective arrangements for limiting excess voltage/currentHemt circuitsEngineering

The embodiment of the invention discloses a band-stop gas discharge tube, a combined lightning protection device, a protection circuit and electronic equipment. The band-stop gas discharge tube comprises: a first porcelain tube; a first electrode and a second electrode which are respectively arranged at two ends of the first porcelain tube, wherein the first porcelain tube, the first electrode andthe second electrode form a closed space, and the closed space is filled with gas; a built-in resistor, wherein one end of the built-in resistor is in contact with the first electrode for electric conduction, and the other end of the built-in resistor is in contact with the second electrode for electric conduction, so that the built-in resistor is connected between the first electrode and the second electrode in parallel. Compared with the prior art, the protection performance of the protection circuit is improved, the service life of the protection circuit is prolonged, on the basis, the built-in resistor is integrated in the band-stop gas discharge tube, the overall structure of the protection circuit can be simplified, the compactness of the protection circuit is better, and the protection circuit can be applied to tight equipment installation.

Owner:SHENZHEN BENCENT ELECTRONICS CO LTD

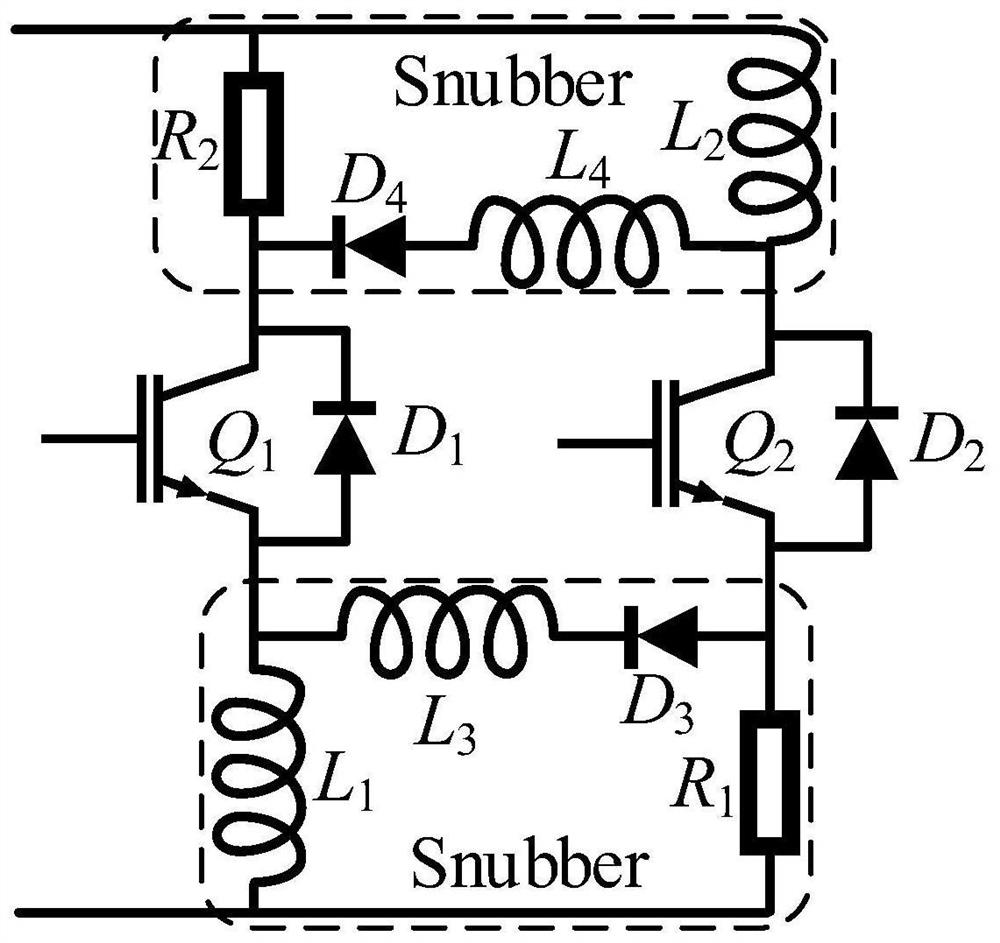

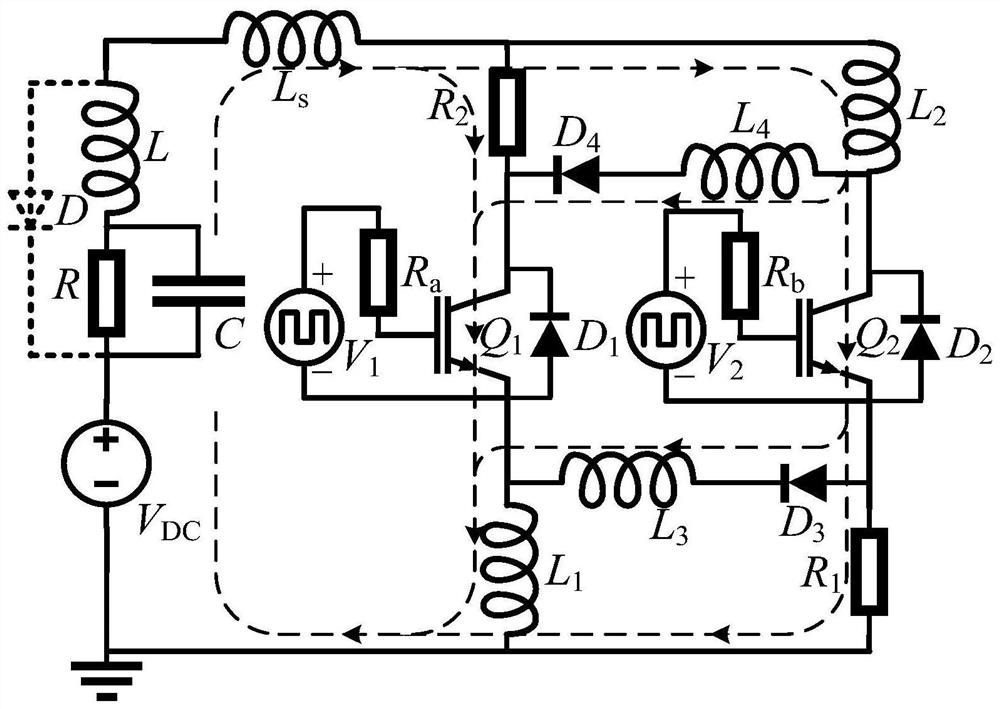

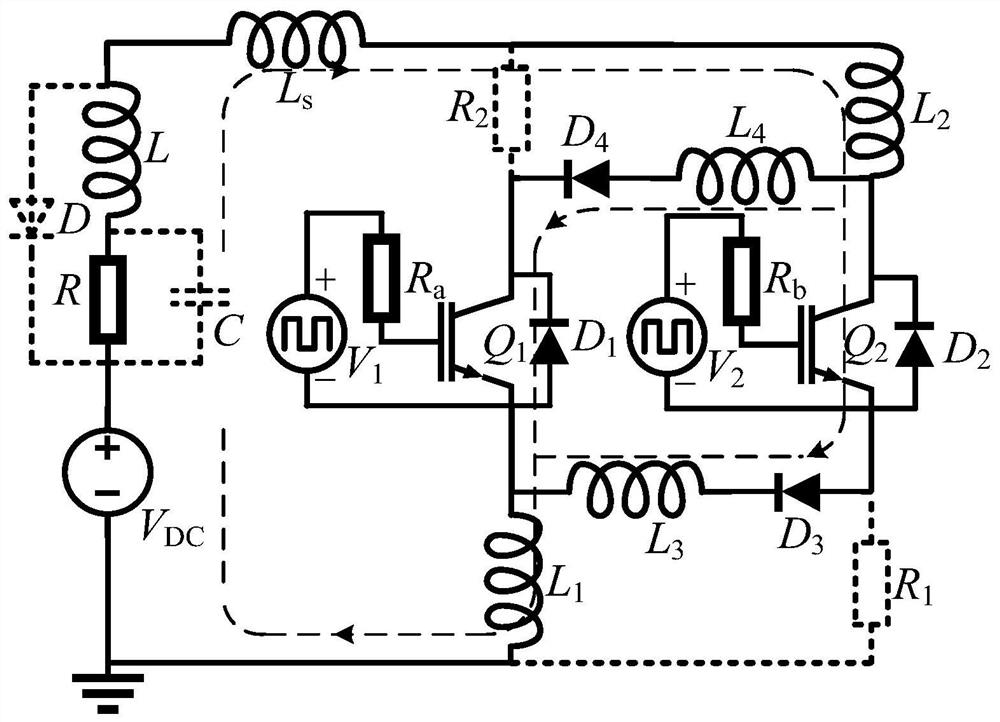

Parallel IGBT dynamic current sharing buffer circuit

ActiveCN113437863APrevent overcurrentTo achieve the purpose of equal flowPower conversion systemsHemt circuitsInductor

The invention discloses a parallel IGBT dynamic current sharing buffer circuit, which comprises two IGBT tubes Q1 and Q2 and a buffer circuit part, and is characterized in that the buffer circuit part comprises buffer inductors L1 and L2, buffer resistors R1 and R2, interconnection diodes D3 and D4 and interconnection inductors L3 and L4. According to the dynamic current sharing buffer circuit, an upper buffer circuit and a lower buffer circuit which are composed of R2, D4, L4, L2, L1, L3, D3 and R1 are organically matched, the dynamic current sharing function of parallel IGBTs can be automatically achieved, safe and stable operation of each IGBT is guaranteed, meanwhile, the current trailing time can be shortened, the problems of transient opening oscillation and gate pole ring current can be avoided, and the circuit is simple in structure, and the software and hardware cost is low.

Owner:CENT SOUTH UNIV

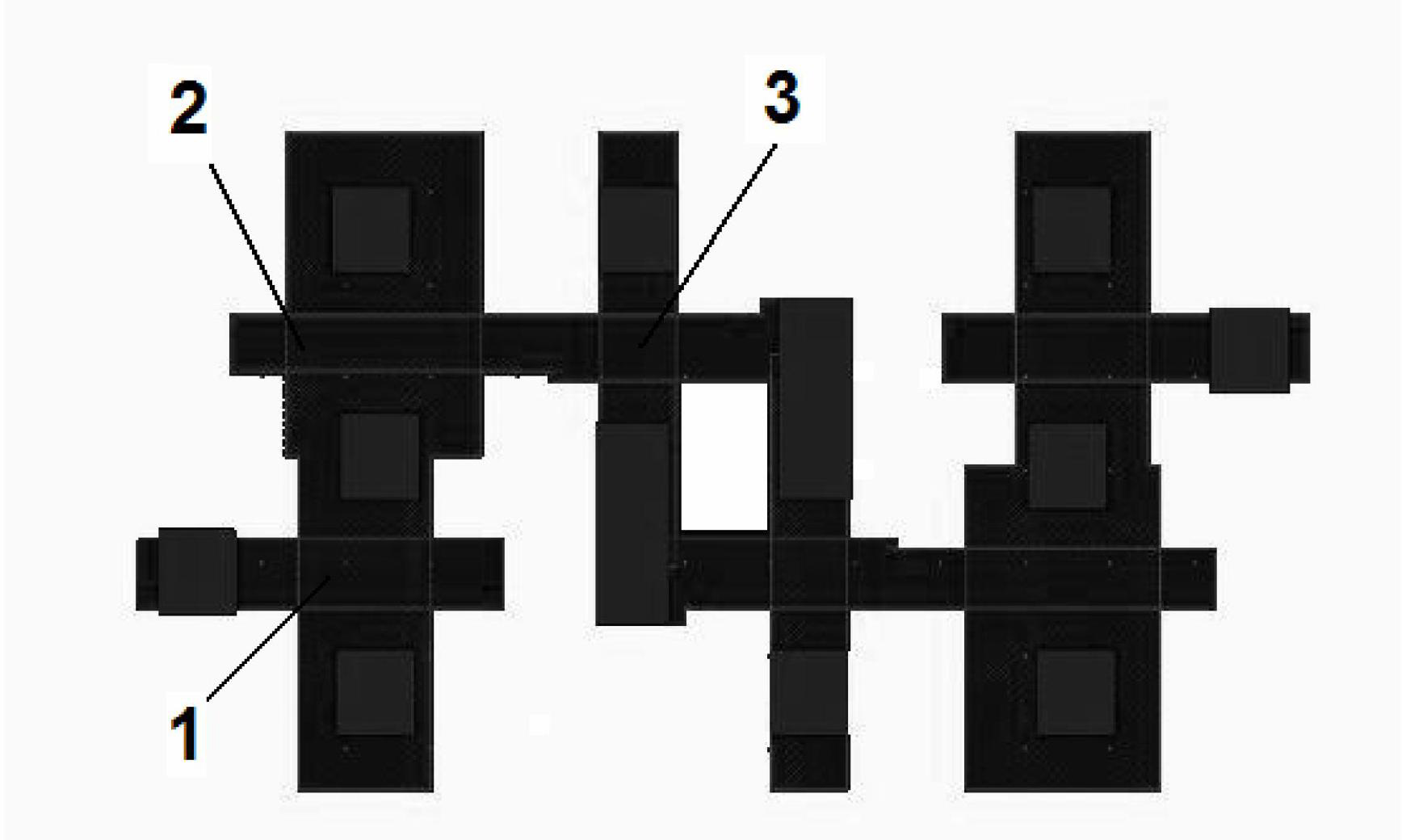

Radio frequency coplanar waveguide element based on silicon base on insulator and preparation method thereof

ActiveCN105914445ASmall equivalent capacitanceIncrease the equivalent resistanceWaveguidesRadio frequencyEtching

The present invention provides a radio frequency coplanar waveguide element based on a silicon base on an insulator and a preparation method thereof. The method comprises: 1) preparing the silicon base on an insulator, wherein the silicon base on the insulator includes a ground floor silicon, an insulating layer and a top silicon which are stacked in order, and the lower portion of the insulating layer is provided with at least one groove of the ground floor silicon corresponding to the position of the preparation of the radio frequency coplanar waveguide element; 2) defining a device area, removing the top chain of the device area, and exposing the upper surface of the insulating layer at the lower portion of the device area; and 3) preparing the radio frequency coplanar waveguide element. Based on the silicon base on the graphical insulator, the radio frequency coplanar waveguide element based on the silicon base on the insulator and the preparation method thereof obtain the coplanar waveguide with a substrate cavity through later period etching, the air medium in the cavity structure allows the equivalent capacitance of the substrate to be reduced and allow the equivalent resistance to be increased so as to eliminate fixed charge and movable charge in the SiO2 and the unfavorable factors, influencing microwave transmission, such as Si / SiO2 system interface state, trap charge and the like, and therefore the medium loss is reduced, and the transmission performance of the coplanar waveguide is improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Method of improving write-in redundancy of static random access memory

InactiveCN102664167AIncrease the equivalent resistanceRaise the threshold voltageSemiconductor/solid-state device manufacturingStatic random-access memoryRandom access memory

The invention provides a method of improving write-in redundancy of a static random access memory. The static random access memory comprises an input / output device and a core device, wherein the core device comprises a pull-up pipe device, the input / output device is used for inputting and outputting signals of a chip and a peripheral circuit, and the thickness of a grid electrode oxide layer of the input / output device is larger than that of the grid electrode oxide layer of the core device. The method of improving write-in redundancy of static random access memory comprises the step of: enabling the thickness of the grid electrode oxide layer of the pull-up pipe device to be larger than that of the grid electrode oxide layer of the core device, and enabling the thickness of the grid electrode oxide layer of the pull-up pipe device to be equal to that of the grid electrode oxide layer of the core device. For example, when the grid electrode oxide layer of the pull-up pipe device is prepared, the formerly generated grid electrode oxide layer for the input / output device is not moved so as to enable the grid electrode oxide layer of the input / output device to serve as the grid electrode oxide layer of the pull-up pipe device.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

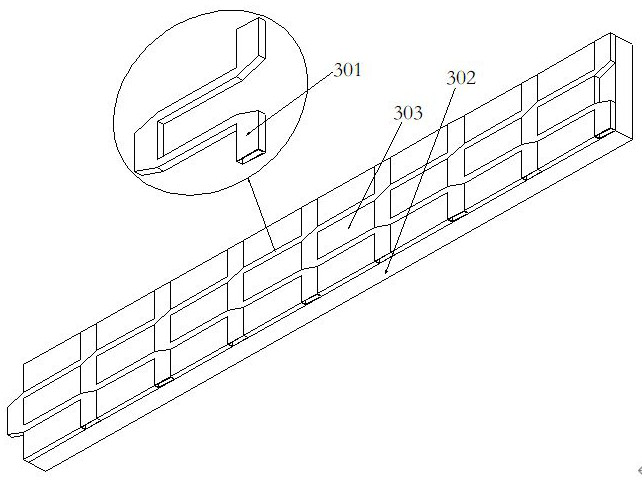

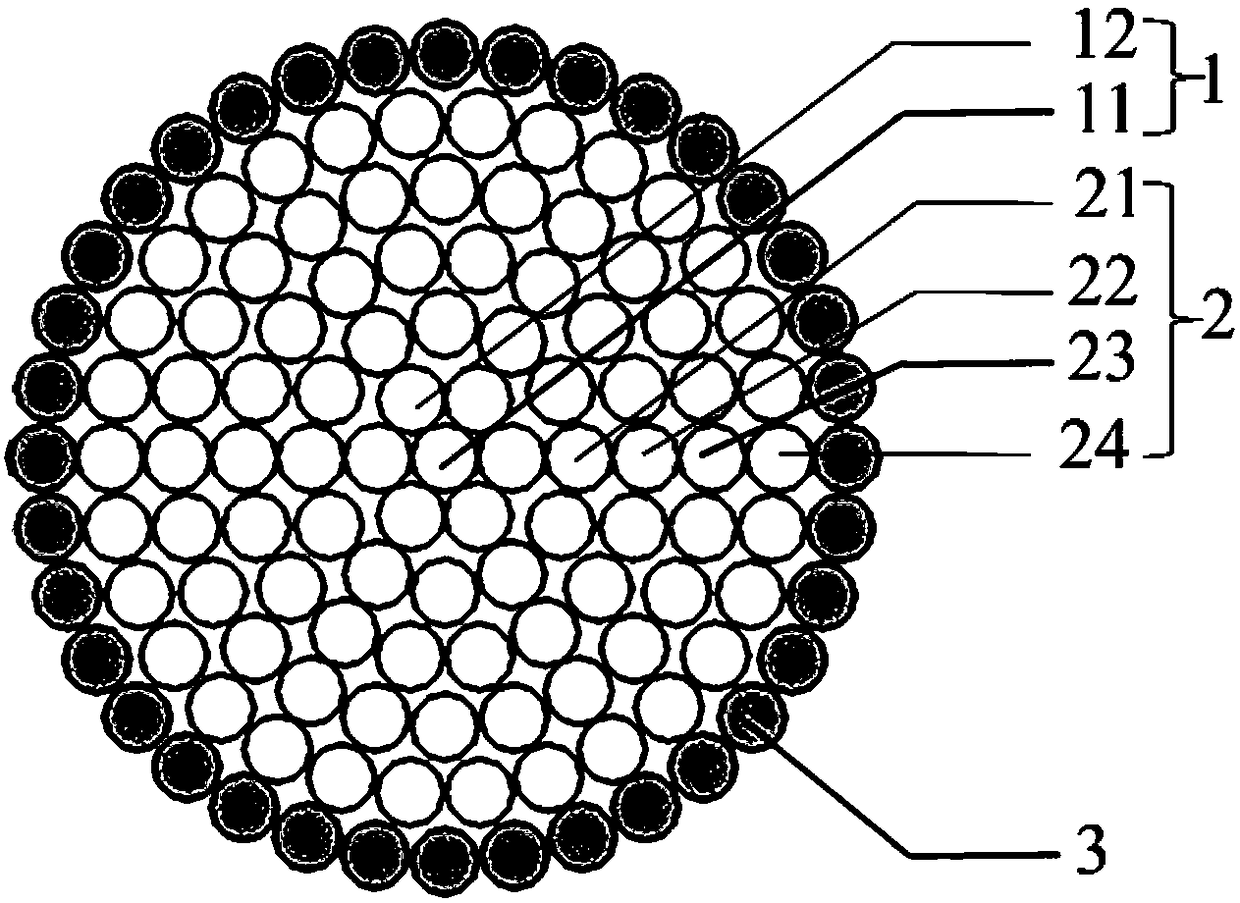

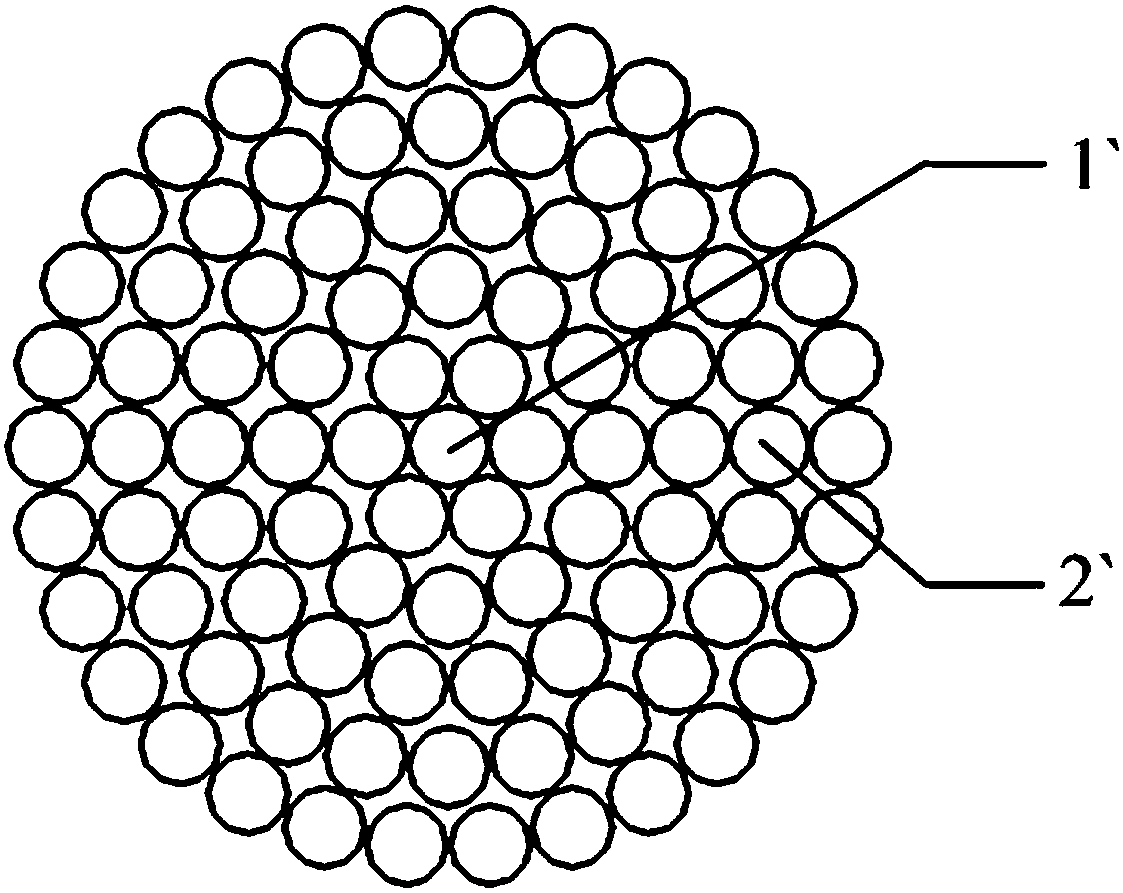

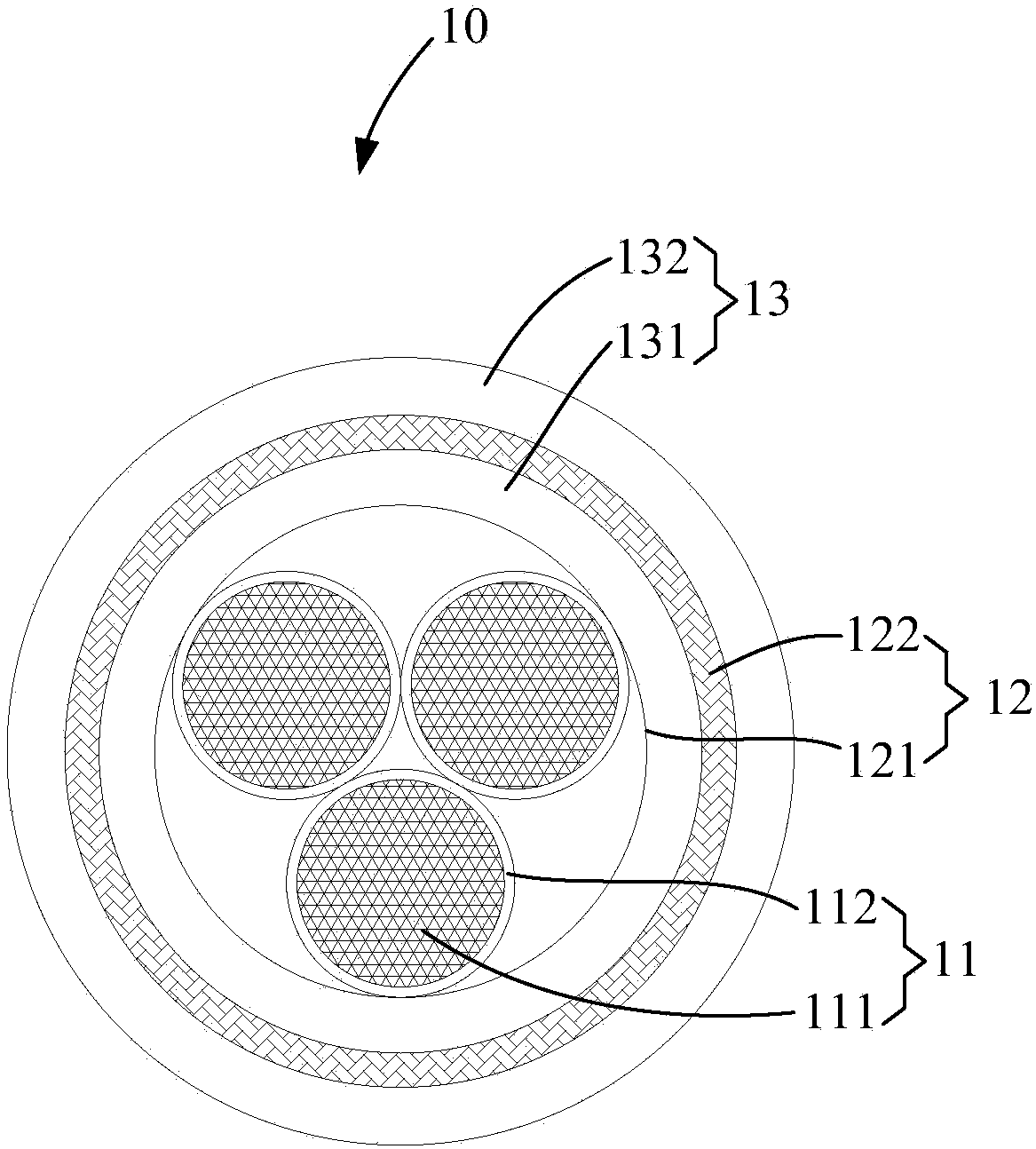

High-voltage direct current transmission conductor

PendingCN108565062AThe effective cross-sectional area is reducedIncrease the equivalent resistanceNon-insulated conductorsPower cables for overhead applicationEngineeringHigh pressure

The present invention discloses a high-voltage direct current transmission conductor. The conductor comprises a strengthening core, an inner current carrying layer twisted at the outer surface of thestrengthening core and an outer current carrying layer twisted at the outer surface of the inner current carrying layer; the strengthening core is made by twisting one or more than one mongline, the inner current carrying layer is made by twisting a plurality of conductor monglines, the outer current carrying layer is made by twisting a plurality of metal monglines, and the skin depth of the metalmonglines is smaller than the skin depth of the conductor monglines. The high-voltage direct current transmission conductor can effectively inhibit the harmonic current, can improve the current carrying amount of the transmission conductor and can facilitate remote transmission.

Owner:CHINA SOUTH POWER GRID ELECTRIC POWER RES INST +1

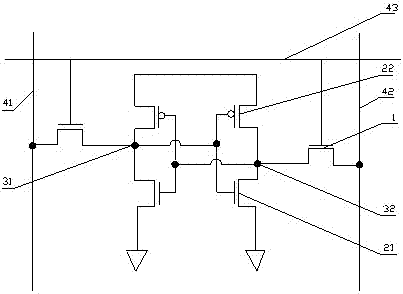

Method for improving reading redundancy of static random access memory

ActiveCN102655123AReduced carrier mobilityIncrease the equivalent resistanceSemiconductor/solid-state device manufacturingStatic random-access memoryEtching

The invention discloses a method for improving the reading redundancy of a static random access memory. The method comprises the following steps of: providing a semiconductor substrate comprising an NMOS (N-channel metal oxide semiconductor) transistor, a PMOS (P-channel metal oxide semiconductor) transistor and a control tube; respectively carrying out selective etching on the source electrodes and the drain electrodes of a PMOS region and a control tube region so as to remove silicon of the source electrode and the drain electrode; forming a first sinking region on the source electrode and the drain electrode of the PMOS region, and forming a second sinking region on the source electrode and the drain electrode of the control tube; and respectively depositing silicon germanium in the first sinking region and the second sinking region. According to the invention, the carrier mobility of a control tube device is reduced while the existing process steps are not added, thereby increasing the equivalent resistance of the control tube and then reducing the potential of a node in the reading process so as to improve the reading redundancy of the random access memory.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method for improving write redundancy of high SRAM (static random access memory)

ActiveCN102738084BIncrease the tensile stressIncrease the equivalent resistanceSemiconductor/solid-state device manufacturingStatic random-access memoryRandom access memory

The invention discloses a method for improving the writing redundancy of static random access memory, which includes an NMOS device with a covering layer, a PMOS device and a pull-up tube. First, the covering layer on the NMOS device and the pull-up tube is simultaneously Remove, and then perform carbon implantation on the NMOS device, the PMOS device with the overlay and the pull-up tube, so that the source and drain ends of the NMOS device and the source and drain ends of the pull-up tube form a lattice structure , to increase the tensile stress in the channel direction. Using a method of improving the write redundancy of static random access memory according to the present invention, by adopting a carbon injection process for the source and drain of the pull-up tube, the tensile stress of the pull-up tube in the channel direction is enhanced, and the pull-up tube device is effectively reduced The carrier mobility increases, the equivalent resistance of the pull-up tube is increased, and at the same time, the random memory writing redundancy is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

SRAM and its method for improving write redundancy

ActiveCN103579244BIncrease compressive stressReduce compressive stressSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryRandom access memory

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Static Random Access Memory and Write Redundancy Improvement Method in Embedded SiGe Process

ActiveCN103579243BIncrease compressive stressReduce compressive stressSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryCharge carrier mobility

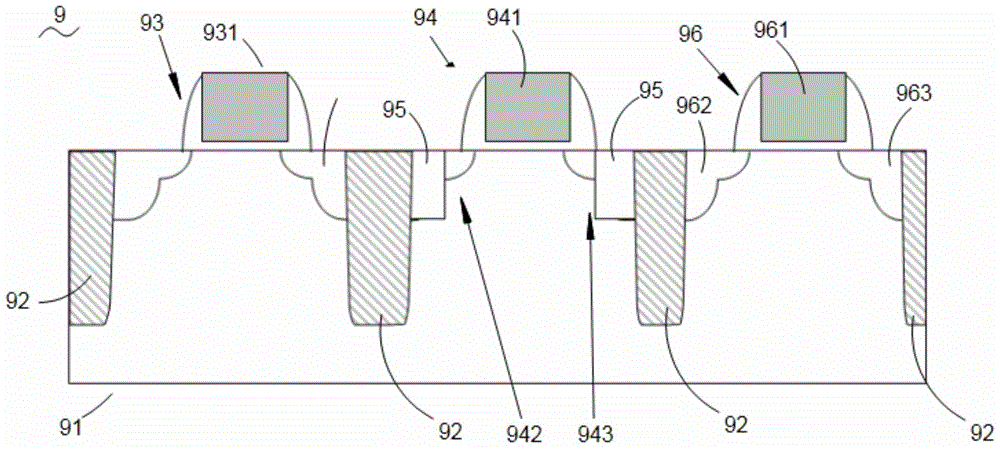

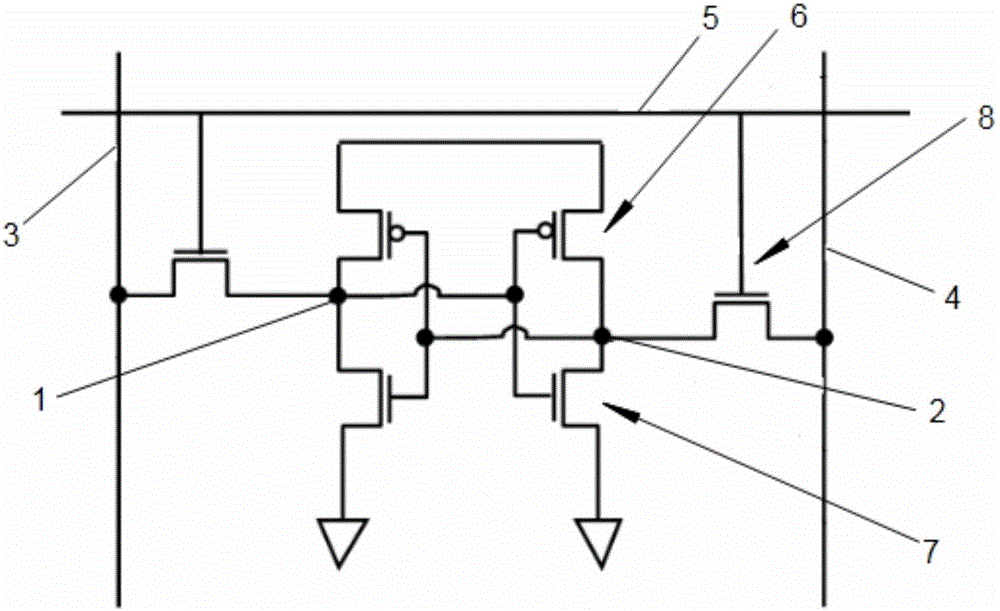

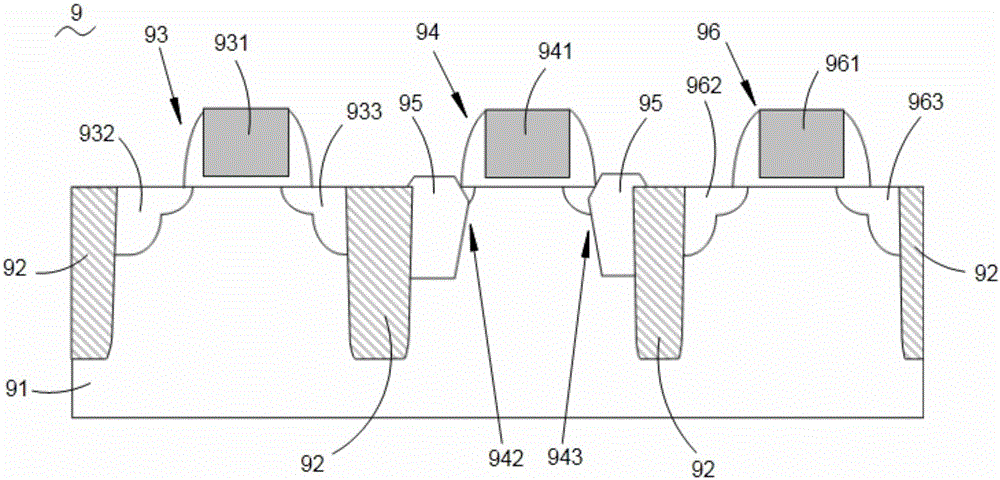

A static random access memory in an embedded silicon germanium process, comprising: a silicon-based substrate; an NMOS device; a PMOS device, the gate of the PMOS device is arranged on the silicon-based substrate, and the source region and the drain region of the PMOS device are respectively arranged In the silicon-based substrate on both sides of the gate, embedded silicon germanium is arranged in the source region and the drain region; the pull-up transistor is a PMOS semiconductor, and the gate of the pull-up transistor is arranged on the silicon-based substrate. The source region and the drain region of the pull-up transistor are respectively arranged in the silicon base substrate on both sides of the gate. The present invention increases the compressive stress in the channel of the PMOS device by arranging embedded silicon germanium in the source region and the drain region of the PMOS device, thereby improving the hole mobility; There is no embedded silicon germanium in the drain region, so that the compressive stress of the pull-up transistor in the channel direction is reduced, the carrier mobility is reduced, and the equivalent resistance of the pull-up transistor is increased, thereby improving the static randomness. Memory write redundancy.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

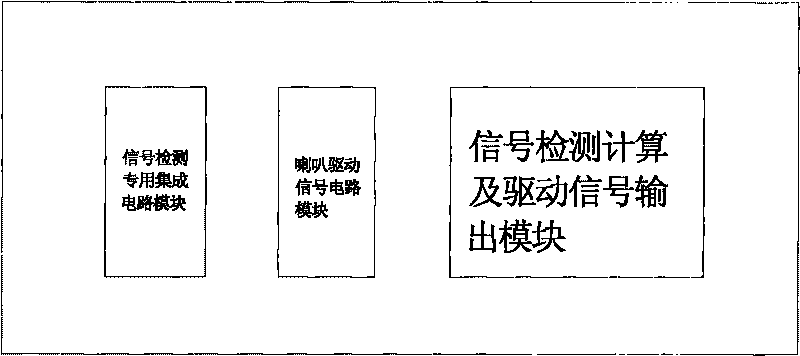

Induction type self-adapting electronic loudspeaker

InactiveCN101754076AResolve interferenceSolve complexityTransducer circuitsHigh volume manufacturingEngineering

The invention relates to an electronic loudspeaker and discloses an induction type self-adapting electronic loudspeaker. The structure of the induction type self-adapting electronic loudspeaker comprises a loudspeaker shell, wherein a frequency acquisition sensor is arranged at the internal bottom of the loudspeaker shell; a moveable stem is arranged above the frequency acquisition sensor; the moveable stem is connected with a loudspeaker sound board; a sounding part is arranged above the loudspeaker sound board; and the frequency acquisition sensor is connected with an electronic main board through a working inductance driving circuit. Compared with the prior art, the induction type self-adapting electronic loudspeaker of the invention has the characteristics of rational design, simple structure, convenient installation, precise detection, high working efficiency, convenient modulation and suitability for mass production.

Owner:胡典兵

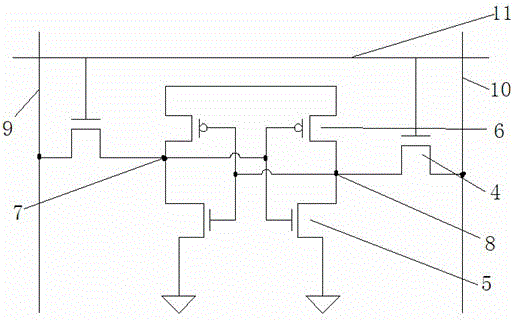

Method for improving static random access memory reading redundancy

ActiveCN102832174BRaise the threshold voltageReduce doping concentrationSemiconductor/solid-state device manufacturingElectrical resistance and conductanceStatic random-access memory

The present invention is a method for improving the read redundancy of static random access memory, which includes the following process. By removing the polysilicon pre-injection process of the control tube, the polysilicon doping concentration of the control tube is reduced, and the polysilicon doping concentration of the control tube is increased. The equivalent resistance improves the read redundancy of the random access memory. Through the method of improving the read redundancy of static random access memory according to the present invention, the doping concentration of the polysilicon gate of the control transistor can be effectively reduced by no longer pre-injection into the control transistor area, thereby increasing the polysilicon gate doping concentration. The parasitic resistance and polysilicon gate depletion phenomenon cause the threshold voltage of the control tube to increase, the turn-on current to decrease, and the equivalent resistance of the control tube to increase. During the reading process, the potential of node 8 is reduced, thereby improving the randomness. Memory readout redundancy.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Depletion mode MOS transistor and method of forming the same

ActiveCN103208427BReduce power consumptionHigh switching current ratioSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowTransistor

The invention discloses a depleted MOS transistor and a forming method thereof. Part of a grid between a source and a drain covers well regions, and the other part of the grid covers doping regions, so that the equivalent resistance of a transistor channel is increased, and on-state and off-state currents of the depleted MOS transistor is reduced. Through adjustment of thicknesses and doping concentrations of the doping regions as well as the ratio of the sum of widths of all doping regions covered by the grid between the source and the drain to the width of the source or the drain in the transistor, the increasing quantity of the equivalent resistance of the transistor channel of the depleted MOS transistor can be kept moderate, therefore the reduction amplitude of the off-state current of the depleted MOS transistor is larger than that of the on-state current, and the on-off current ration of the depleted MOS transistor is improved while the power consumption of the transistor is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Cable

InactiveCN108346489AImprove temperature riseReduce temperature risePower cables with screens/conductive layersInsulated cablesSkin effectAlternating current

The invention discloses a cable, which comprises an insulation sheath and at least two wire groups coated by the insulation sheath, wherein each wire group comprises at least two wires, and each two wires is arranged in a mutual insulation mode. In the technical scheme of the invention, through arranging the at least two wires in each wire group in a mutual insulation mode, problems of large powerloss and high temperature rise and the like caused by skin effects in transmission of high frequency alternating current in the traditional cable can be well solved, and the cable thus has low temperature rise and good transmission effects.

Owner:ZTEV +1