Method for improving static random access memory reading redundancy

A static random and memory technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of low readout performance of random access memory, and achieve improved readout redundancy, reduced turn-on current, increased The effect of large parasitic resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the technical means, creative features, objectives and effects of the invention easy to understand, the present invention will be further elaborated below in conjunction with specific diagrams.

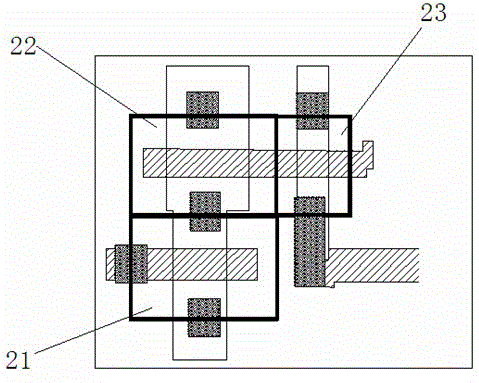

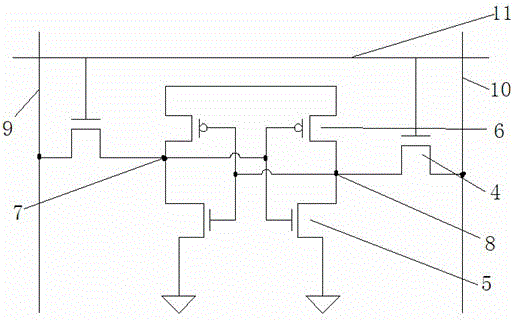

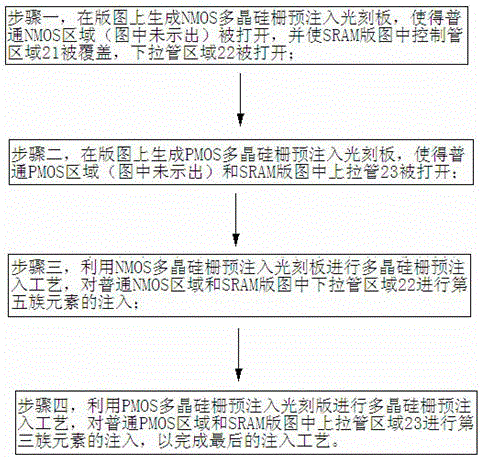

[0023] Such as figure 1 , 2 , Shown in 3, a kind of method for improving SRAM readout redundancy, wherein, comprise following process steps:

[0024] Step 1, generate an NMOS polysilicon gate pre-implantation photoresist on the layout, so that the common NMOS area (not shown in the figure) is opened, and the control tube area 21 in the SRAM layout is covered, and the pull-down tube area 22 is opened;

[0025] Step 2, generate a PMOS polysilicon gate pre-implantation photolithography plate on the layout, so that the pull-up transistor 23 in the common PMOS area (not shown in the figure) and the SRAM layout is turned on;

[0026] Step 3, using the NMOS polysilicon gate pre-implantation photolithography plate to perform the polysilicon gate pre-implantation proc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More