Static discharge clamping circuit with bias circuit in 90 nanometer CMOS (complementary metal-oxide-semiconductor transistor) process

A technology of electrostatic discharge and bias circuit, which is applied in the field of electrostatic discharge clamping circuit and electrostatic discharge protection, can solve the problems of large static leakage of RC network, and achieve the reduction of static leakage, reduction of capacitor area, increase, etc. The effect of effective resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described below with reference to the accompanying drawings and the embodiments thereof.

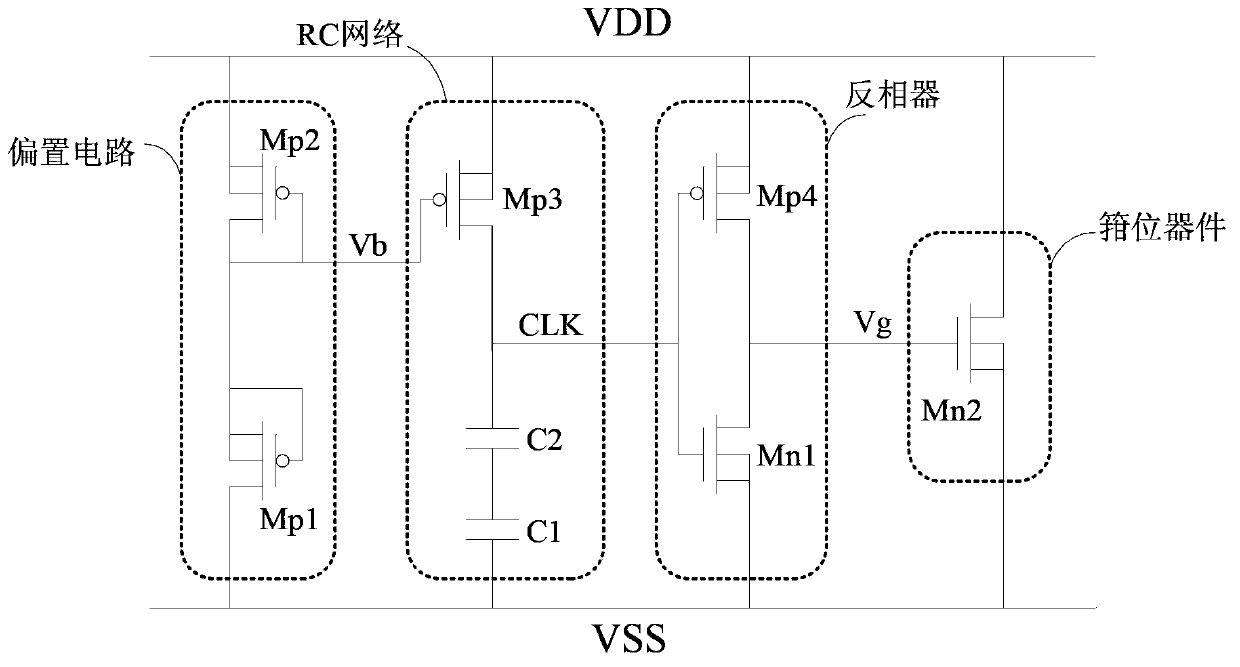

[0022] refer to figure 2 , the present invention includes: RC network, inverter, clamping device and bias circuit; Wherein:

[0023] The RC network includes: a first capacitor C1, a second capacitor C2 and a third PMOS transistor Mp3; one end of the first capacitor C1 is connected to one end of the second capacitor C2, and the other end of the first capacitor C1 is connected to the ground voltage VSS , the other end of the second capacitor C2 is connected to the drain of the third PMOS transistor Mp3; the third PMOS transistor Mp3 is used as a resistor, its source is connected to the power supply voltage VDD, its gate is connected to the bias voltage Vb, and its drain The pole is connected to the second capacitor C2, and the detection voltage CLK is input to the inverter for detecting electrostatic discharge.

[0024] The inverter includes:...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More