Method of improving write-in redundancy of static random access memory

A static random, write redundant technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem that the static random memory write redundancy is not particularly ideal, and achieve threshold voltage rise, increase The effect of large equivalent resistance and reduced turn-on current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

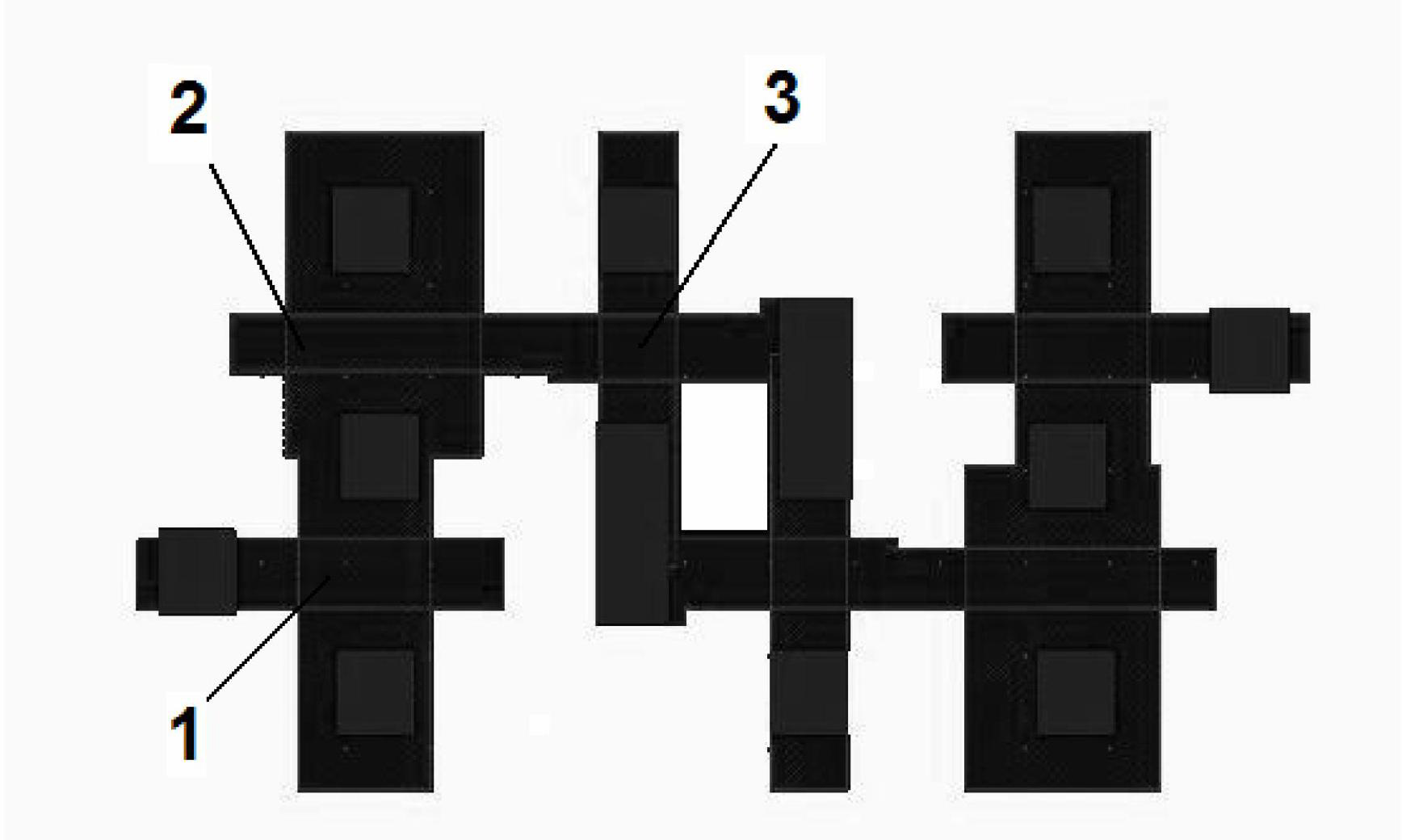

Image

Examples

Embodiment Construction

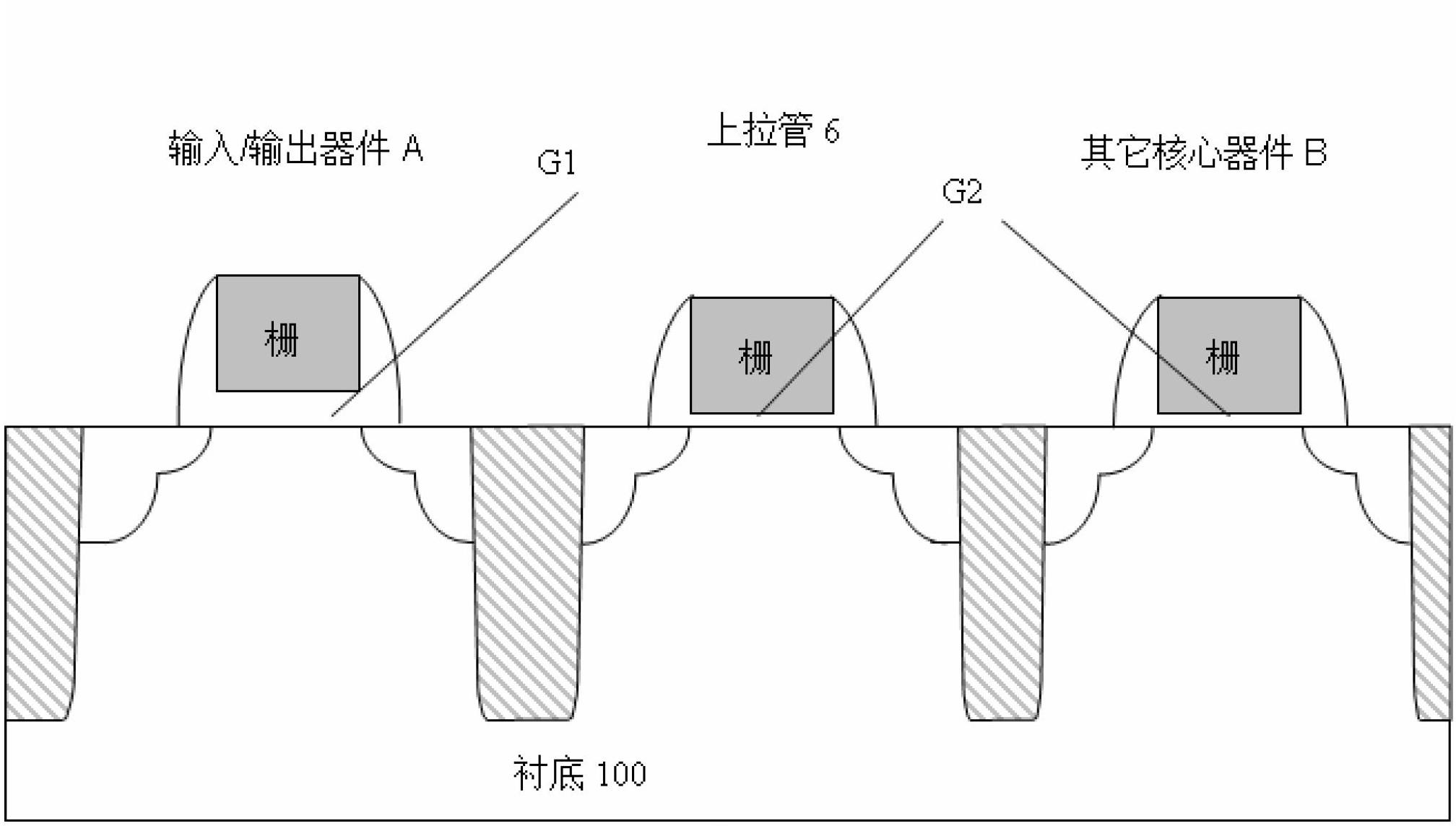

[0020] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

[0021] In the CMOS logic device process, there are usually two main devices, the input / output device (I / O device) and the core device (Core device). The input / output device is mainly used for signal input and output of the chip and peripheral circuits; due to the input I / O devices need to withstand higher voltages, so the gate oxide layer of I / O devices is usually thicker. The core device is mainly used for logic operations inside the chip, etc., and because it needs to be faster, the gate oxide layer of the core device is usually thinner. That is, the gate oxide of the I / O device is typically thicker relative to the core device.

[0022] Likewise, SRAM includes I / O devices as well as core devices.

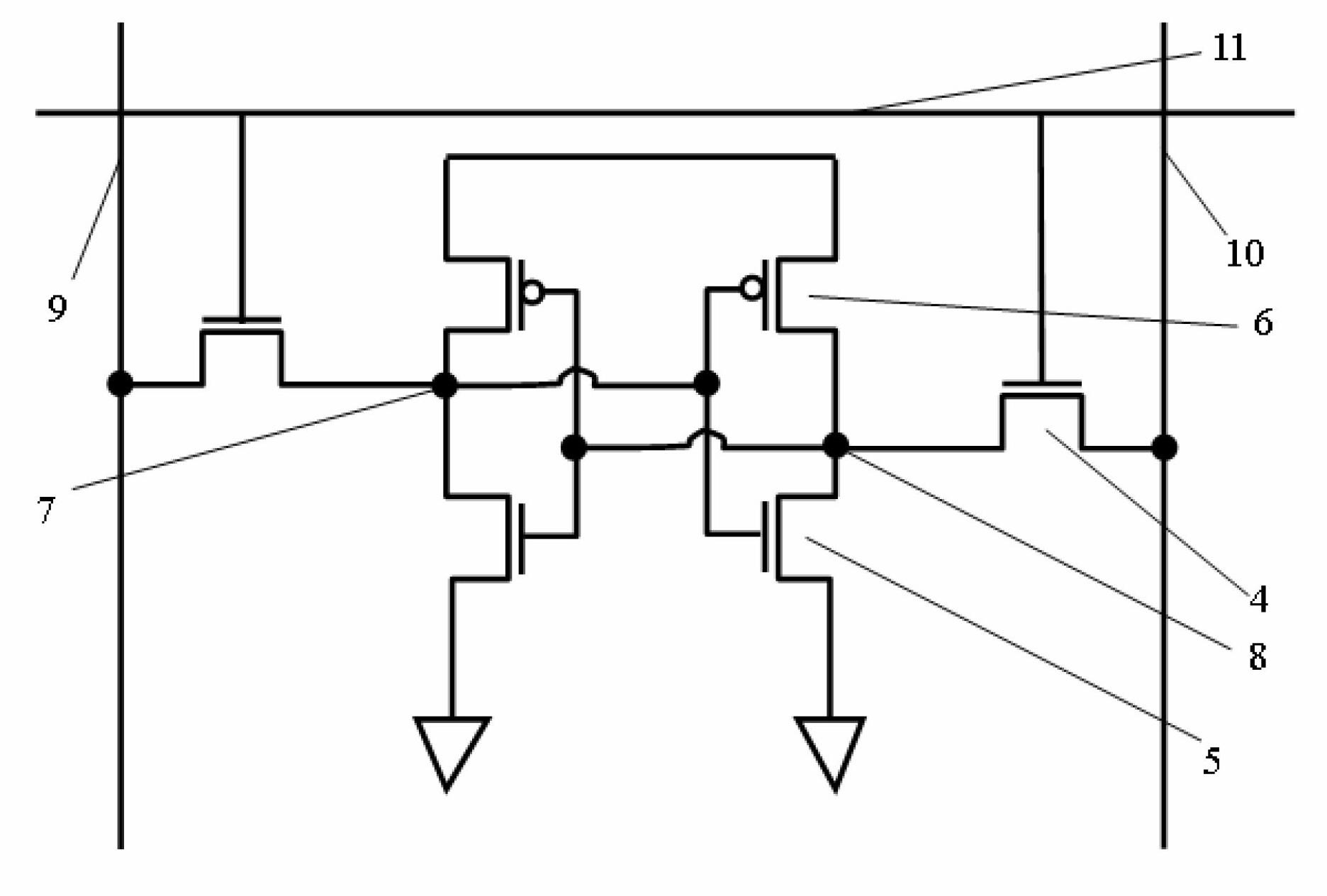

[0023] In particular, for the pull-up trans...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More