Depletion mode MOS transistor and method of forming the same

A MOS transistor, depletion-mode technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc. On-state current and off-state current, the effect of increasing the equivalent resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

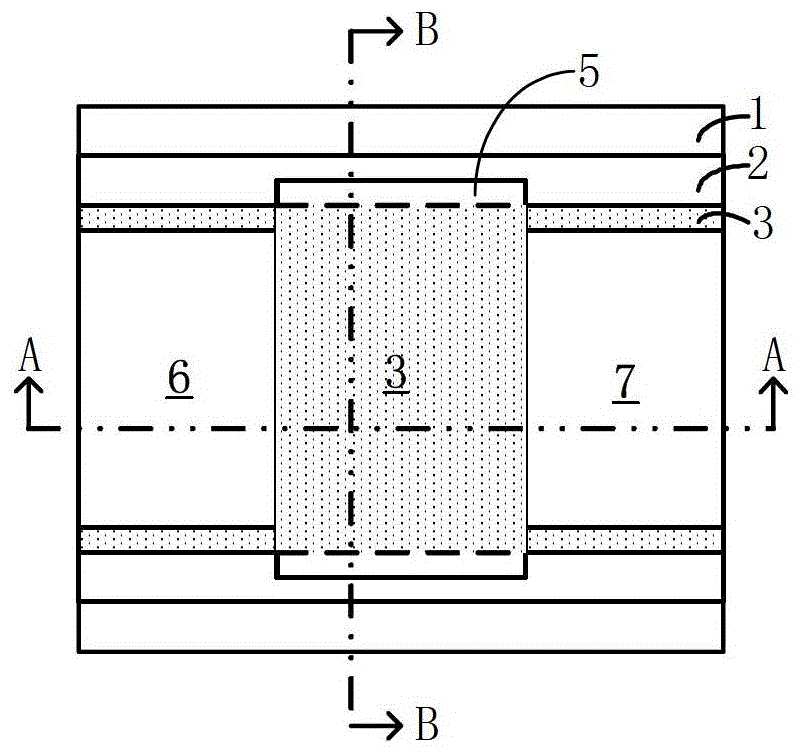

Image

Examples

Embodiment approach 1

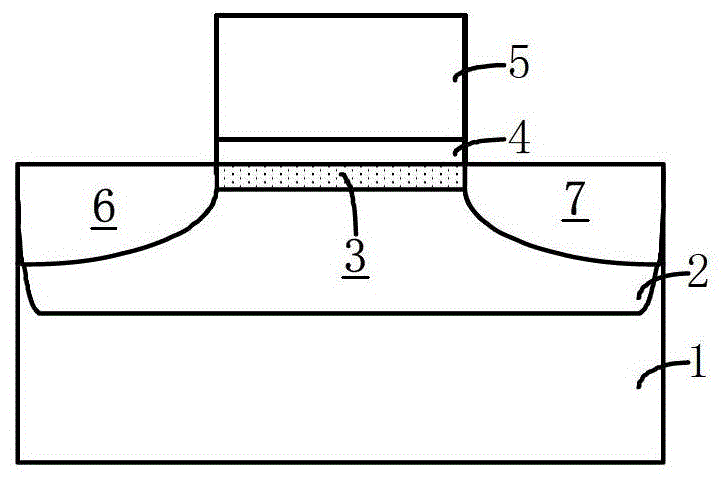

[0042] Such as Figure 4 As shown, step S1 is firstly performed: providing a semiconductor substrate 100 with a well region 110 inside the substrate 100 .

[0043] The semiconductor substrate 100 may be a common substrate such as a bulk silicon substrate (bulk silicon), a silicon-on-insulator (SOI) substrate, or the like. The semiconductor substrate 100 has a well region 110 inside. In this embodiment, a depletion NMOS transistor is taken as an example, so the doping type of the well region 110 is P type.

[0044] In this embodiment, the method for forming the well region 110 includes: forming a patterned photoresist layer (not shown) on the semiconductor substrate 100, and performing ion implantation using the patterned photoresist layer as a mask to A well region 110 is formed in the substrate 100 . Wherein, in a specific embodiment, the process parameters of ion implantation to form the well region 110 include: the dopant ion is boron, and the implanted ion dose is 1E12 / c...

Embodiment approach 2

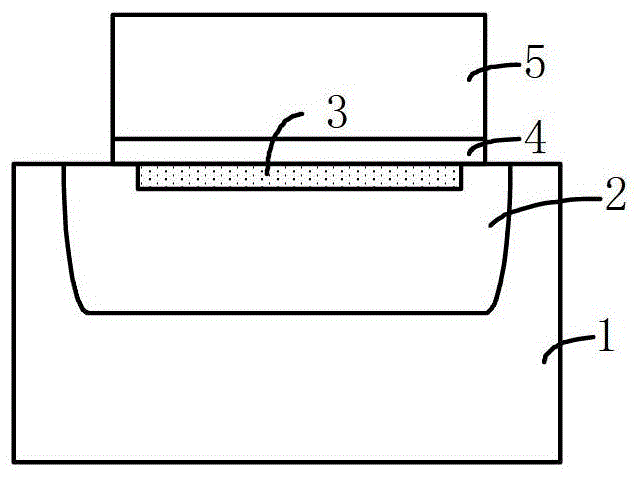

[0074] The shape of the doped region and the specific distribution of the doped region in the well region in the first embodiment are not limited to the above-mentioned embodiments, for example, in one example of the first embodiment, two doped regions are formed in the well region, In an example of the second embodiment, such as Figure 15 As shown, only one doped region 130 is formed on the surface of the well region. For another example, in another embodiment of the second embodiment, such as Figure 16 As shown, three doped regions 130 distributed at intervals are formed on the surface of the well region.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More