Electron static discharge (ESD) clamping circuit and integrated circuit

A clamping circuit and circuit technology, applied in the direction of circuits, electrical components, electric solid devices, etc., can solve the problem of occupying a large layout area, and achieve the effect of increasing the equivalent resistance, reducing the capacitance C, and reducing the layout area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

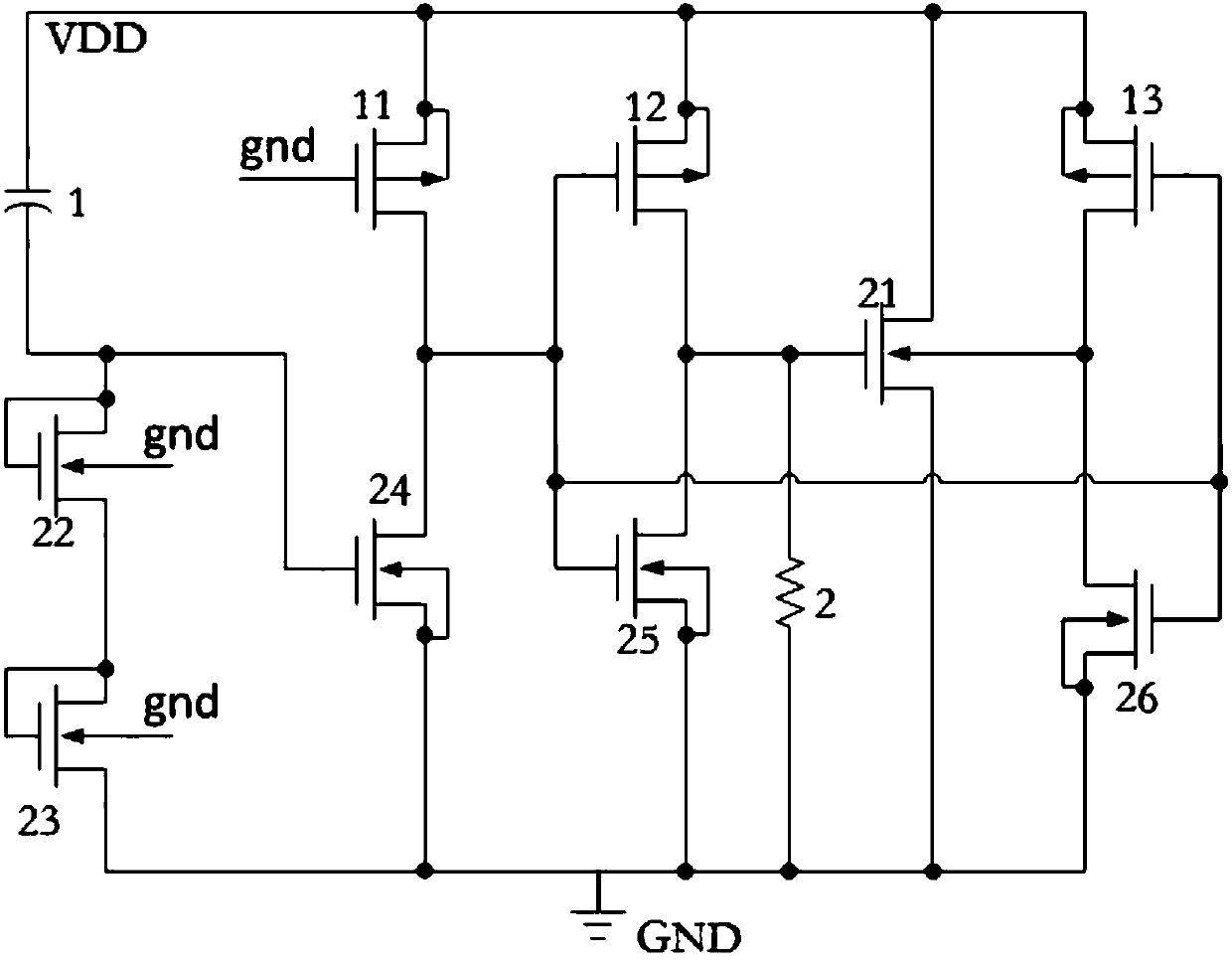

[0039] In this embodiment, an ESD clamping circuit is provided, such as figure 2 Shown include:

[0040] Capacitor 1, resistor 2, first P-type transistor 11, second P-type transistor 12, third P-type transistor 13, first N-type transistor 21, second N-type transistor 22, third N-type transistor 23, fourth N-type transistor 24, fifth N-type transistor 25 and sixth N-type transistor 26;

[0041] Wherein, the source of the first P-type transistor 11 is connected to the power supply VDD, the drain of the first P-type transistor 11 is connected to the gate of the second P-type transistor 12, and the first P-type transistor 11 The gate of the second P-type transistor 12 is connected to the power supply, and the drain of the second P-type transistor 12 is connected to the gate of the first N-type transistor 21; the third P The source of the third P-type transistor 13 is connected to the power supply, the drain of the third P-type transistor 13 is connected to the drain of the sixt...

Embodiment 2

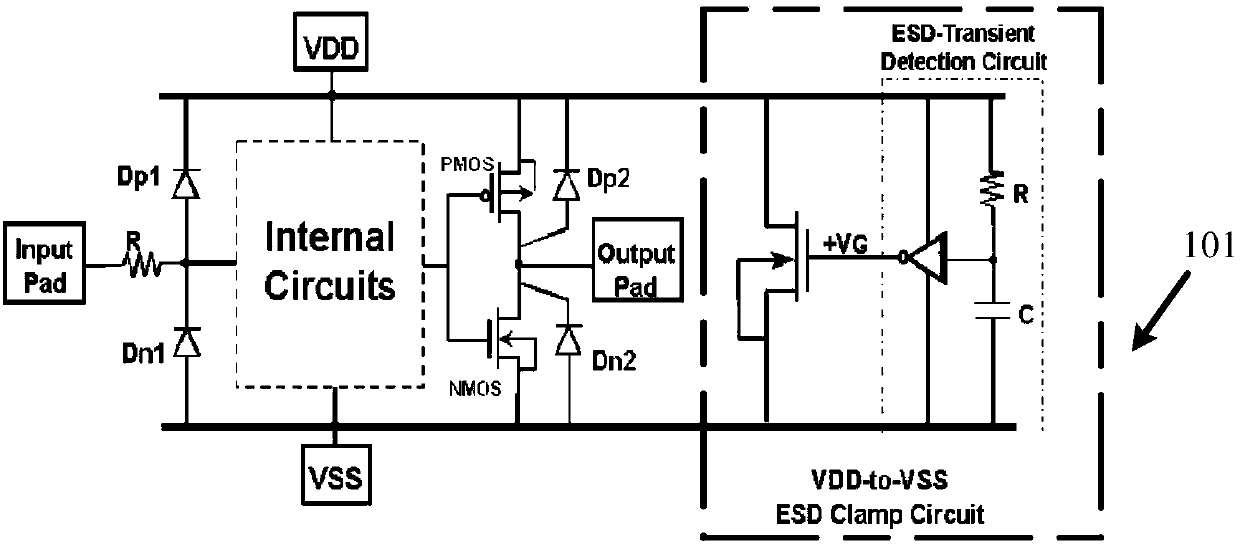

[0054] This embodiment provides an integrated circuit, such as Figure 5 shown, including:

[0055] A functional circuit 501 and a clamping circuit 502 connected to the functional circuit 501;

[0056] The clamping circuit 502 includes: a capacitor, a resistor, a first P-type transistor, a second P-type transistor, a third P-type transistor, a first N-type transistor, a second N-type transistor, a third N-type transistor, a fourth N-type transistors, fifth N-type transistors and sixth N-type transistors;

[0057] Wherein, the source of the first P-type transistor is connected to a power supply, the drain of the first P-type transistor is connected to the gate of the second P-type transistor, and the gate of the first P-type transistor is grounded; The source of the second P-type transistor is connected to the power supply, and the drain of the second P-type transistor is connected to the gate of the first N-type transistor; the source of the third P-type transistor is connec...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Capacitance | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More