Method for improving write margin of static random access memory

A static random and write redundancy technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem that the write redundancy of static random access memory is not particularly ideal, and improve the write redundancy. , the effect of reducing hole mobility and increasing equivalent resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

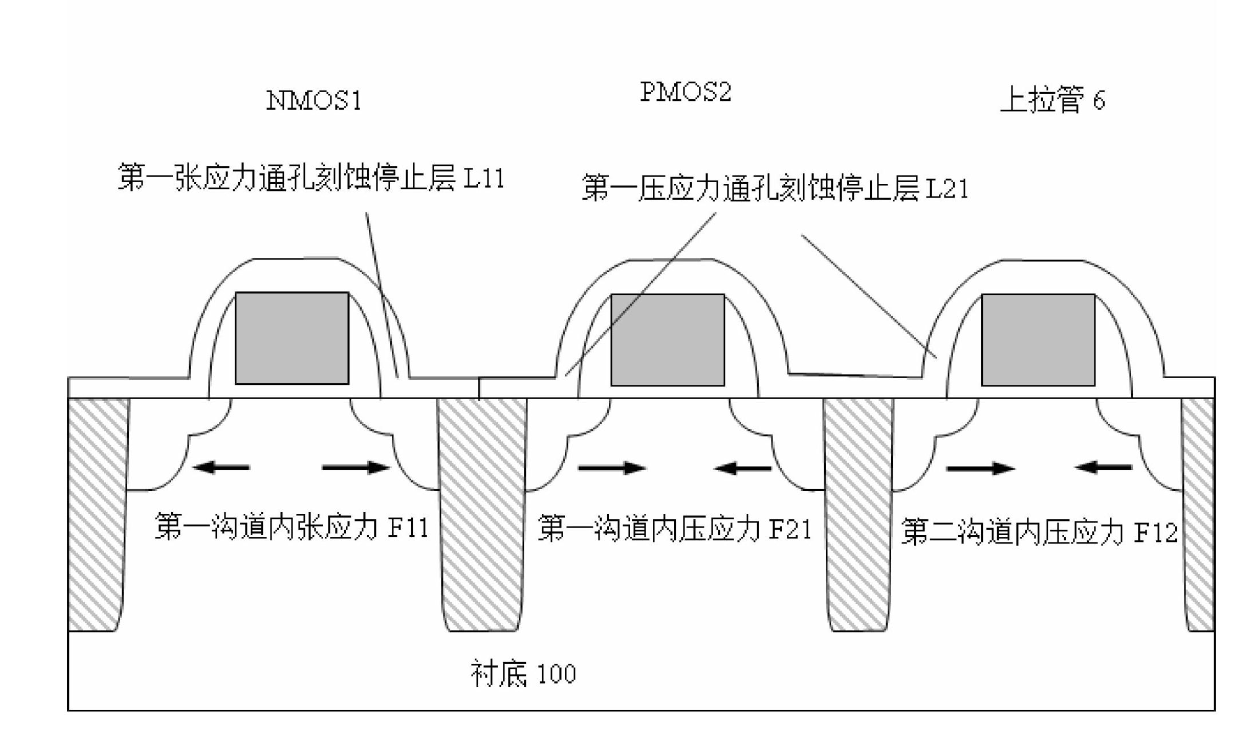

[0020] Specifically, refer to image 3 Let's first describe the prior art. image 3 It is a schematic diagram used in the process of the prior art. After the stress engineering treatment of the double stress via etch stop layer, the area NMOS1 of all NMOS devices covers the first stress via etch stop layer L11, and the area of the pull-up tube 6 The region PMOS2 of all other PMOS devices (hereinafter referred to as “all other PMOS devices”) and the region of the pull-up tube 6 cover the first compressive via etch stop layer L21 .

[0021] Such as image 3 As shown, the NMOS device area is covered with a via etch stop layer (the first tensile stress via etch stop layer L11) that generates tensile stress, and the stress generated in the channe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More