Method and apparatus for diagnosing a fault of a memory

A fault diagnosis device and fault diagnosis technology, applied in the direction of static memory, instrument, etc., can solve the problem of increased fault diagnosis time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

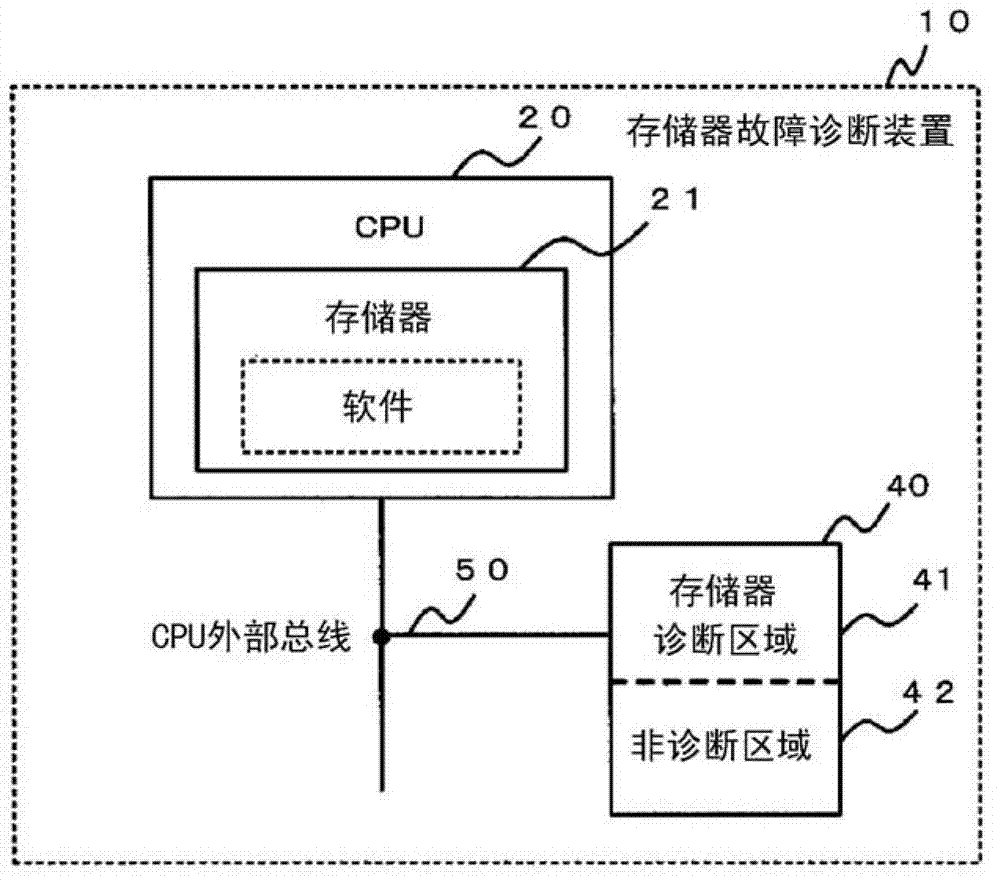

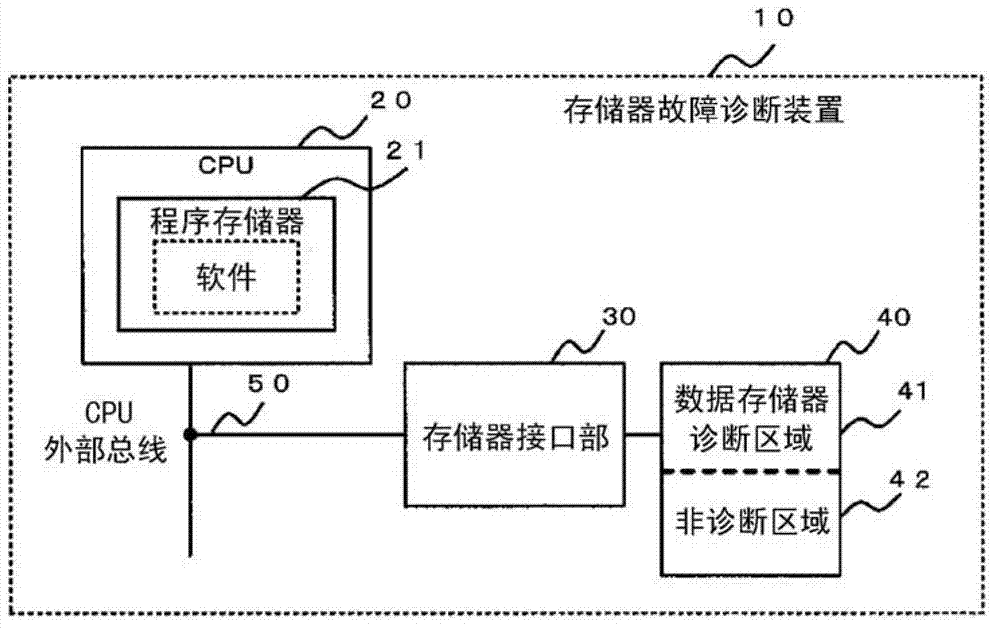

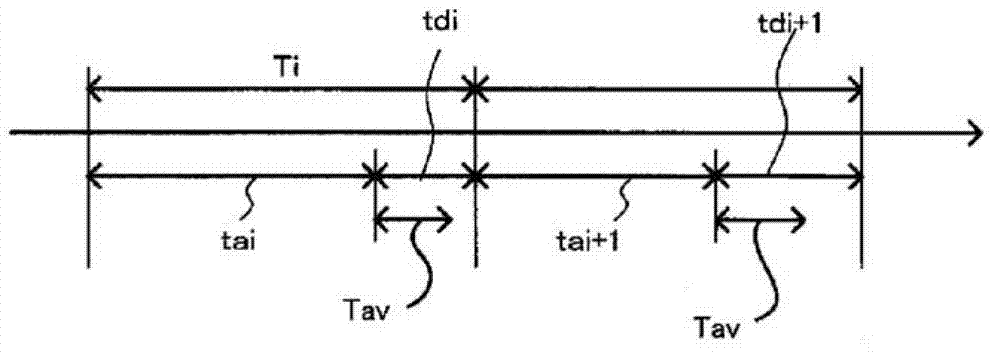

[0047] refer to Figure 1 to Figure 10 , and the first embodiment will be described. figure 1 and figure 2 It is a structural block diagram explaining the first embodiment. The memory fault diagnosis device 10 includes a CPU 20 and a memory 40 connected by a CPU external bus 50 .

[0048] The CPU 20 is provided with a memory 21 storing software including application software (hereinafter referred to as application) for executing applications and memory fault diagnosis software (hereinafter referred to as memory fault diagnosis) for diagnosing a fault in the memory 40 .

[0049] Also, the memory 40 includes a preset diagnostic area 41 to be targeted for memory fault diagnosis and a non-diagnostic area 42 not to be targeted for diagnosis and to be a temporary storage area for fault diagnosis of the diagnostic target area 41 .

[0050] The memory fault diagnosis device 10 may include a CPU core (not shown) and an internal memory, and the CPU core and the internal memory may b...

no. 2 approach

[0151] Below, refer to Figure 11 , the second embodiment of the memory failure detection device according to the present invention will be described. For each part of the second embodiment, the same parts as those of the first embodiment are denoted by the same symbols, and description thereof will be omitted.

[0152] The difference between the second embodiment and the first embodiment is that, regarding the size of the row area, in the first embodiment, the entire column width is taken as the area in the column direction of the memory, but in the second embodiment, for For each row address in the physical address of the memory, only one cell area of the first cell area in the column direction is used as an area, so that the access in the row direction is reduced by the row area size / cell area size in the inter-row area diagnosis quantity.

[0153] In this embodiment, the diagnosis range of the read / write diagnosis in the inter-row area diagnosis is narrowed. However, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More