Transverse power device with super junction structure and manufacturing method thereof

A technology for lateral power devices and manufacturing methods, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as substrate auxiliary depletion, avoid charge imbalance, and suppress substrate auxiliary depletion effect of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The specific implementation of the lateral power device with super junction structure and the manufacturing method provided by the present invention will be described in detail below with reference to the accompanying drawings.

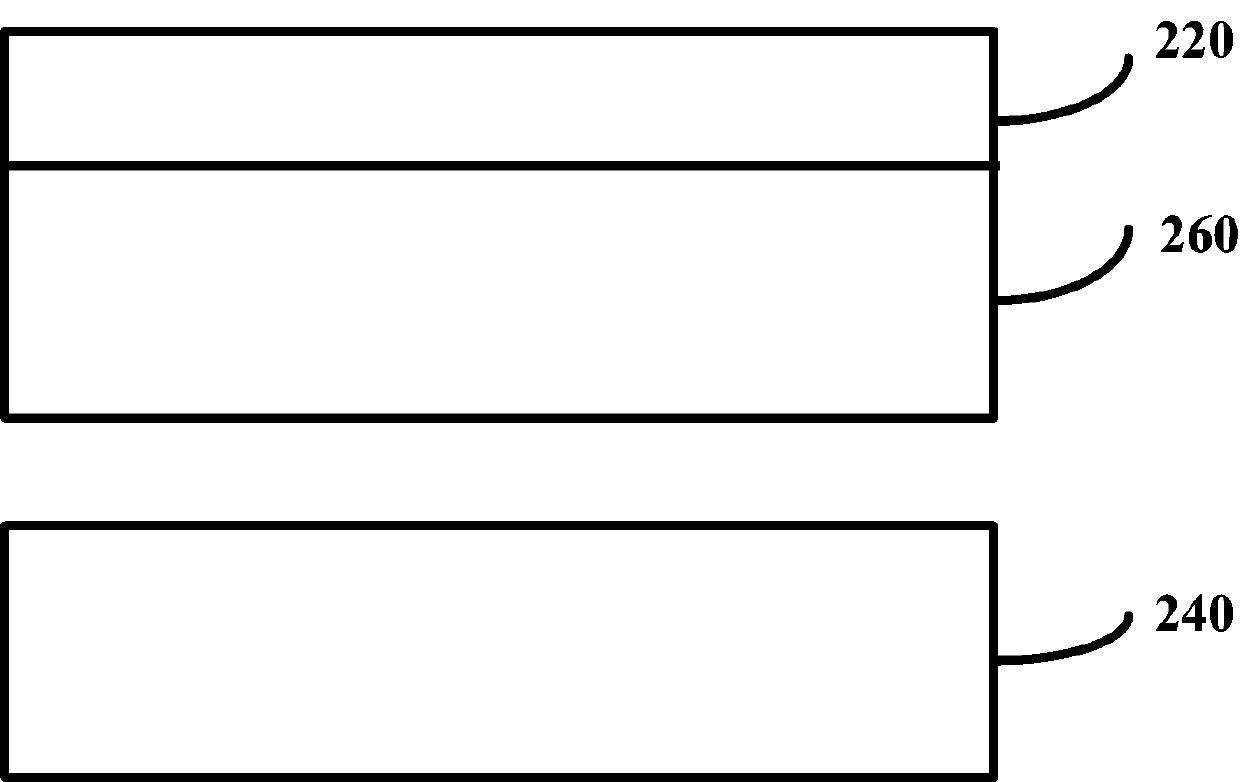

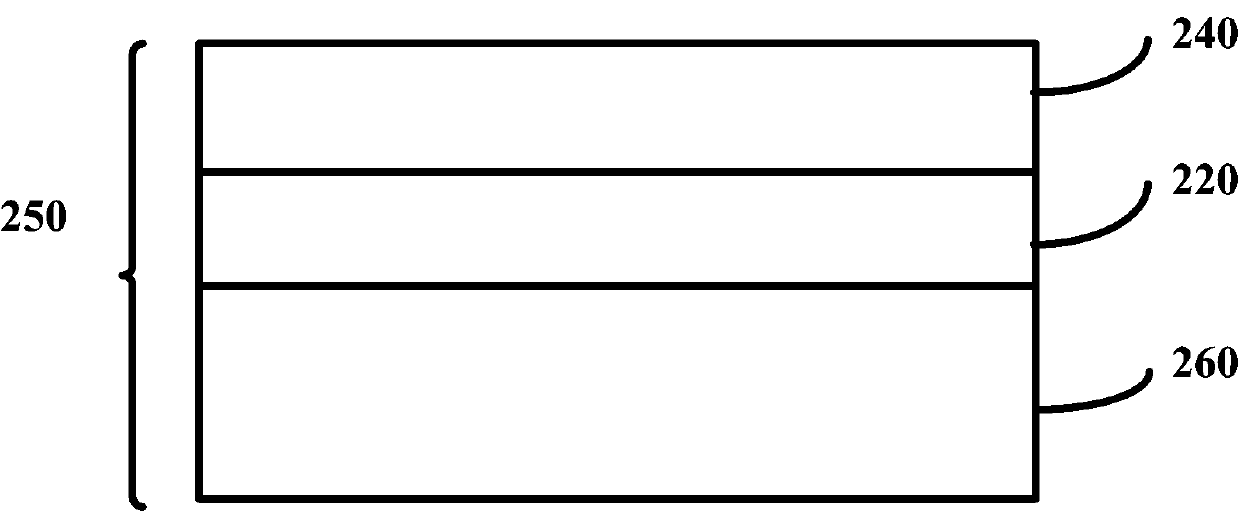

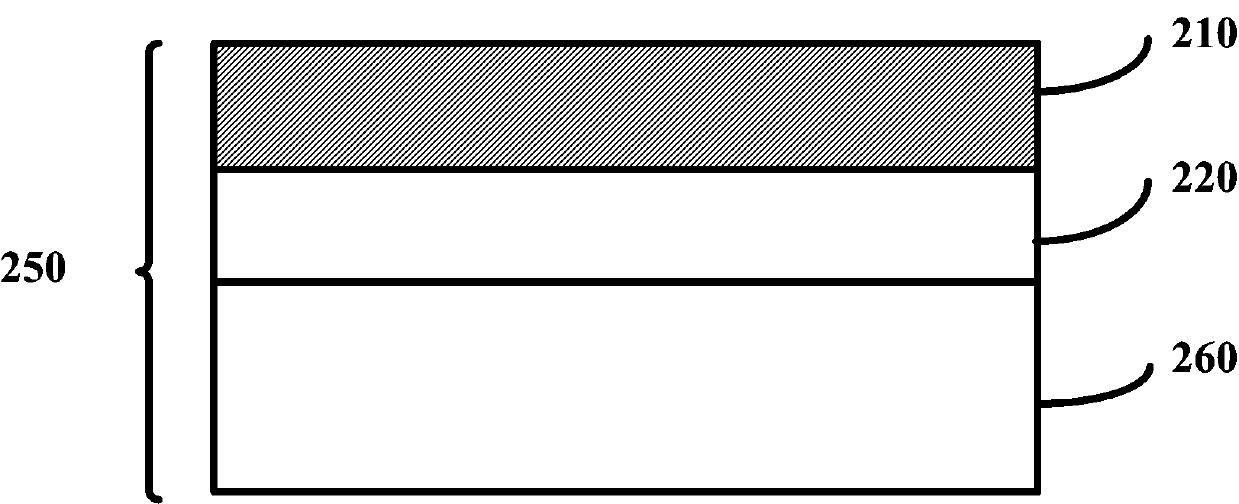

[0022] Reference attached figure 2 Shown is a schematic diagram of a lateral power device with a super junction structure described in this specific embodiment, including a P-type support substrate 200, a silicon germanium layer 210 located on the surface of the support substrate, and a silicon germanium layer located on the surface of the silicon germanium layer. The buried oxide layer 220 and the active layer 230 located on the surface of the buried oxide layer; the active layer includes a gate region 234, a source region 233 and a drain region 237 respectively located on both sides of the gate region 234 and a The drift region between the region 234 and the drain region 237; the source region 233 and the drain region 237 are both N-type dop...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More