Method for replacing FPGA IP programs inside SOC by SOC

A program and chip technology, applied in the field of SOC chip replacing its own internal FPGAIP program, to achieve the effect of reducing cost, simplifying system complexity, and flexible and diverse working modes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

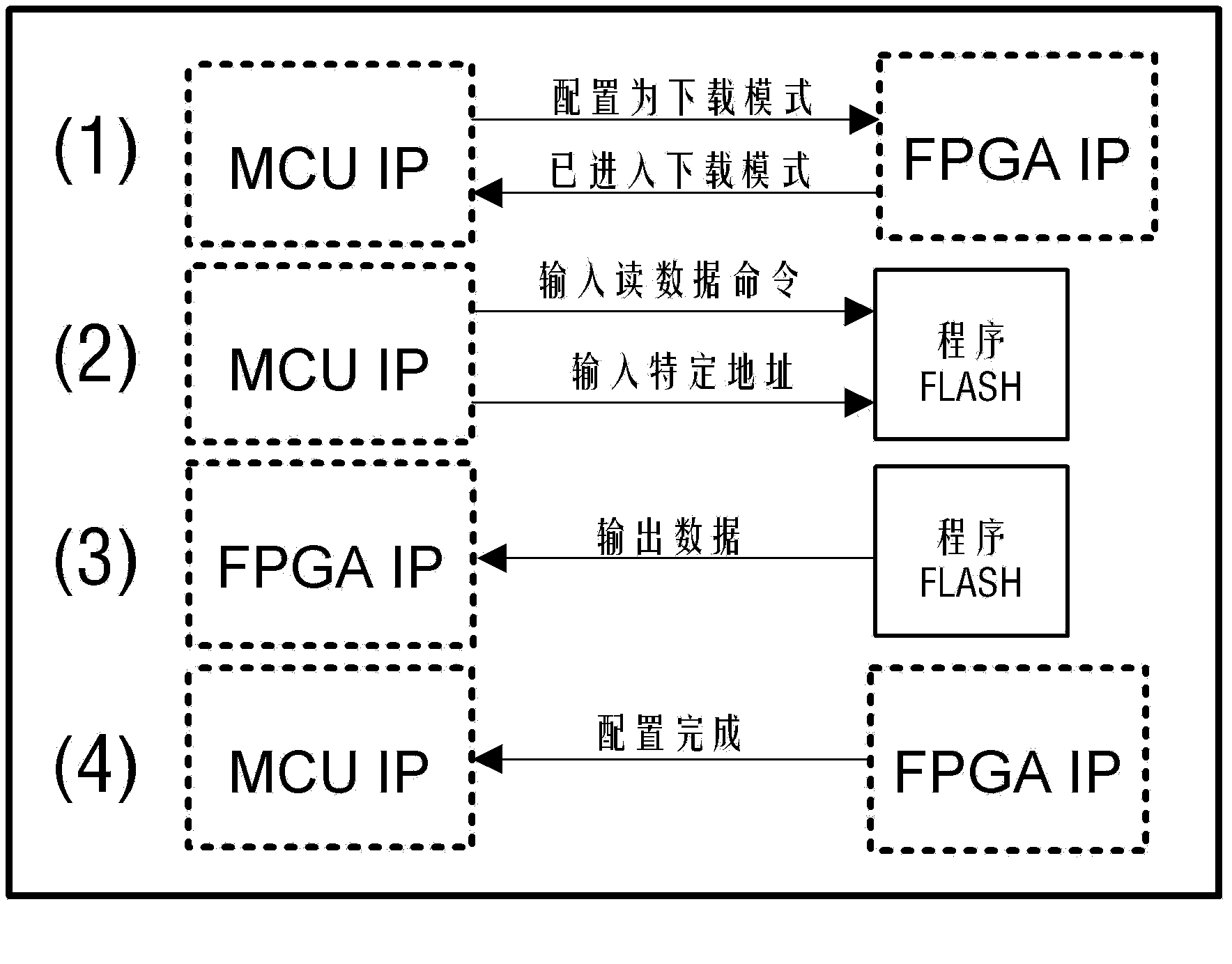

[0029] Such as figure 1 as shown, figure 1 It is a flow chart of the method that the SOC chip provided by the invention replaces its own internal FPGA IP program, and the method may further comprise the steps:

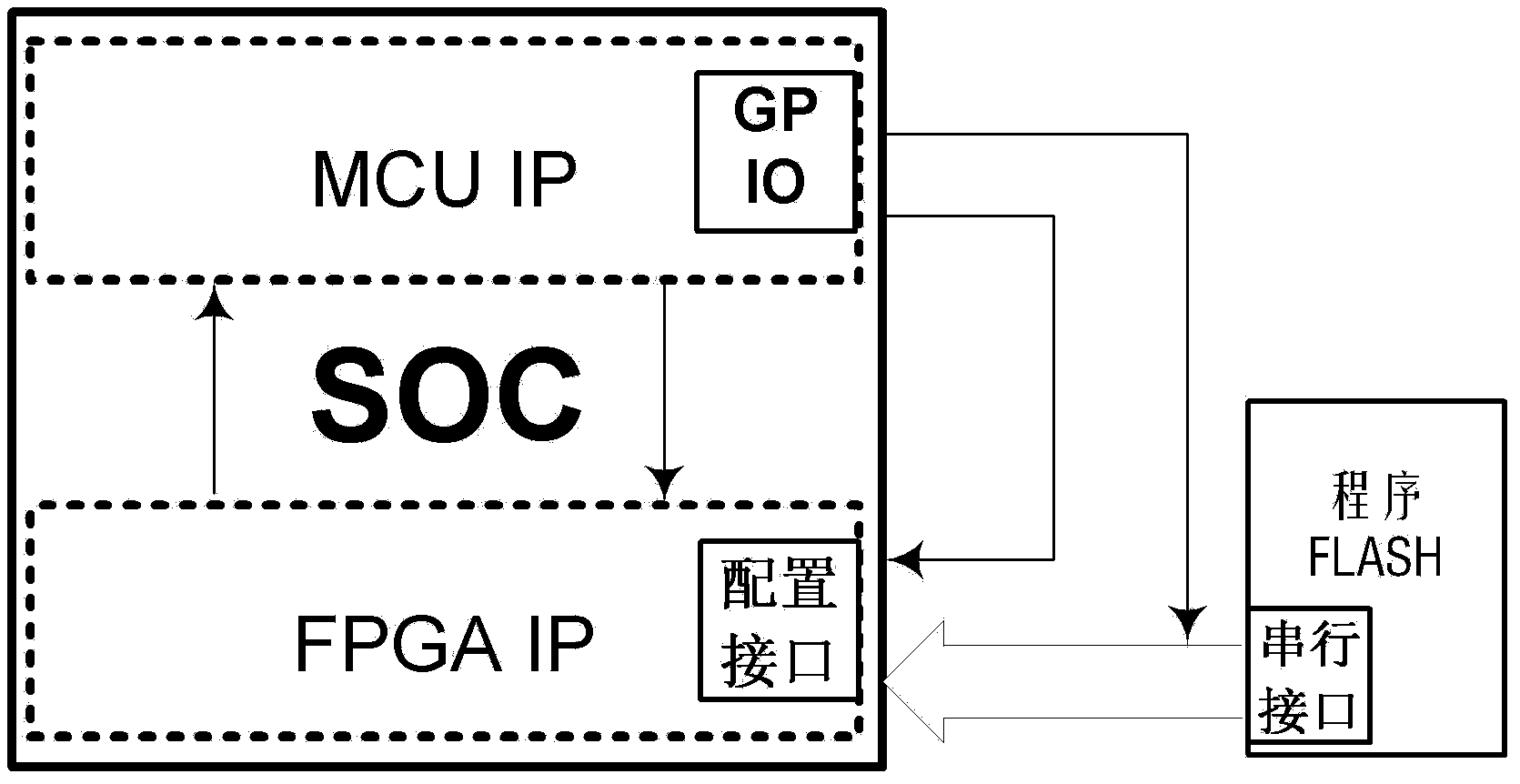

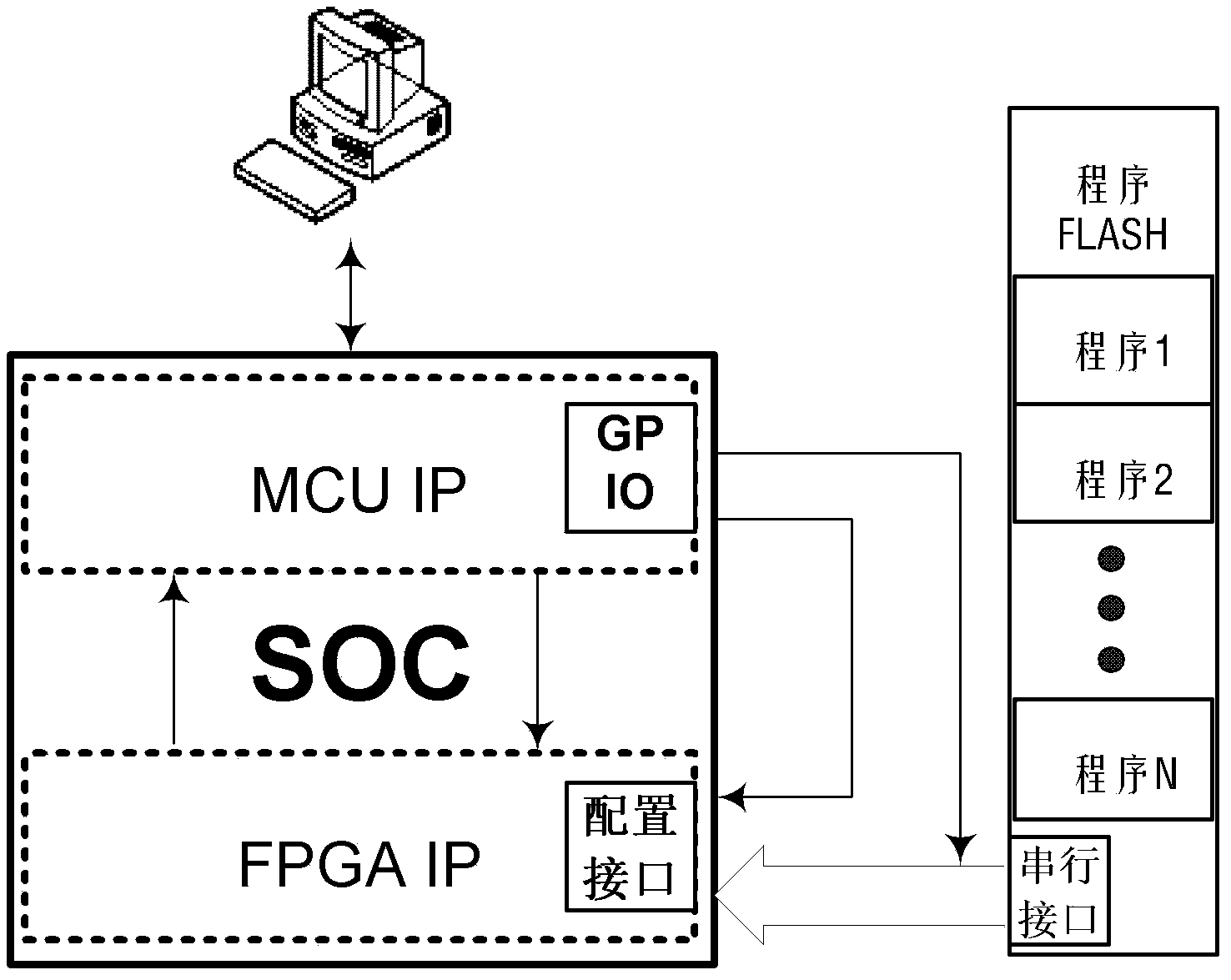

[0030] Step 1: The MCU IP configures the configuration interface of the FPGA IP through its general-purpose IO interface, so that the FPGA IP under normal working conditions enters the program download mode;

[0031] Step 2: MCU IP inputs specific command bytes for reading data to the serial FLASH memory through its general-purpose IO interface, and then inputs the start address where the program code to be configured is located, so that the serial FLASH memory sends FPGA IP from the start address Start outputti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More