Semiconductor device

A semiconductor and transistor technology, applied in the field of semiconductor devices, can solve the problem of increasing the area of semiconductor devices, achieve the effect of reducing the area and suppressing the latch-up effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

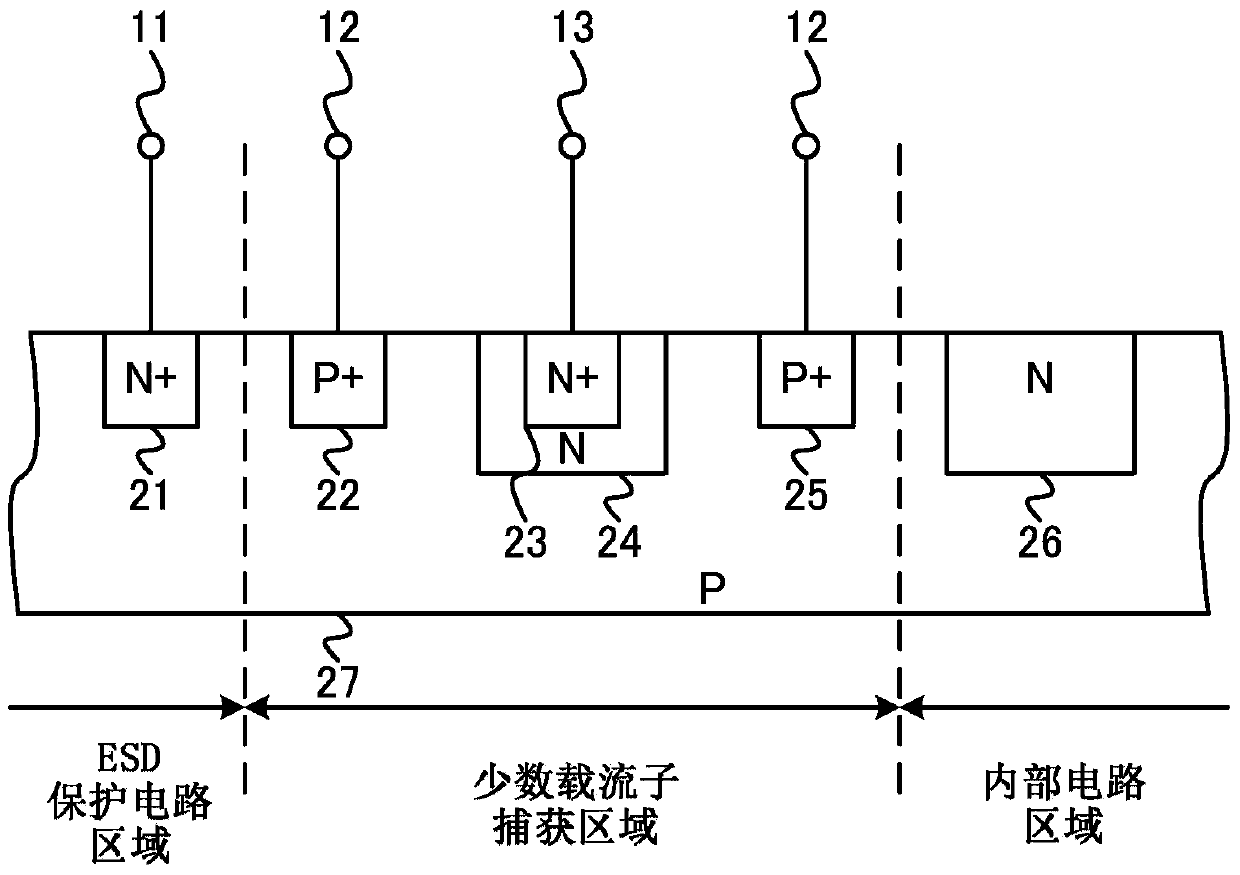

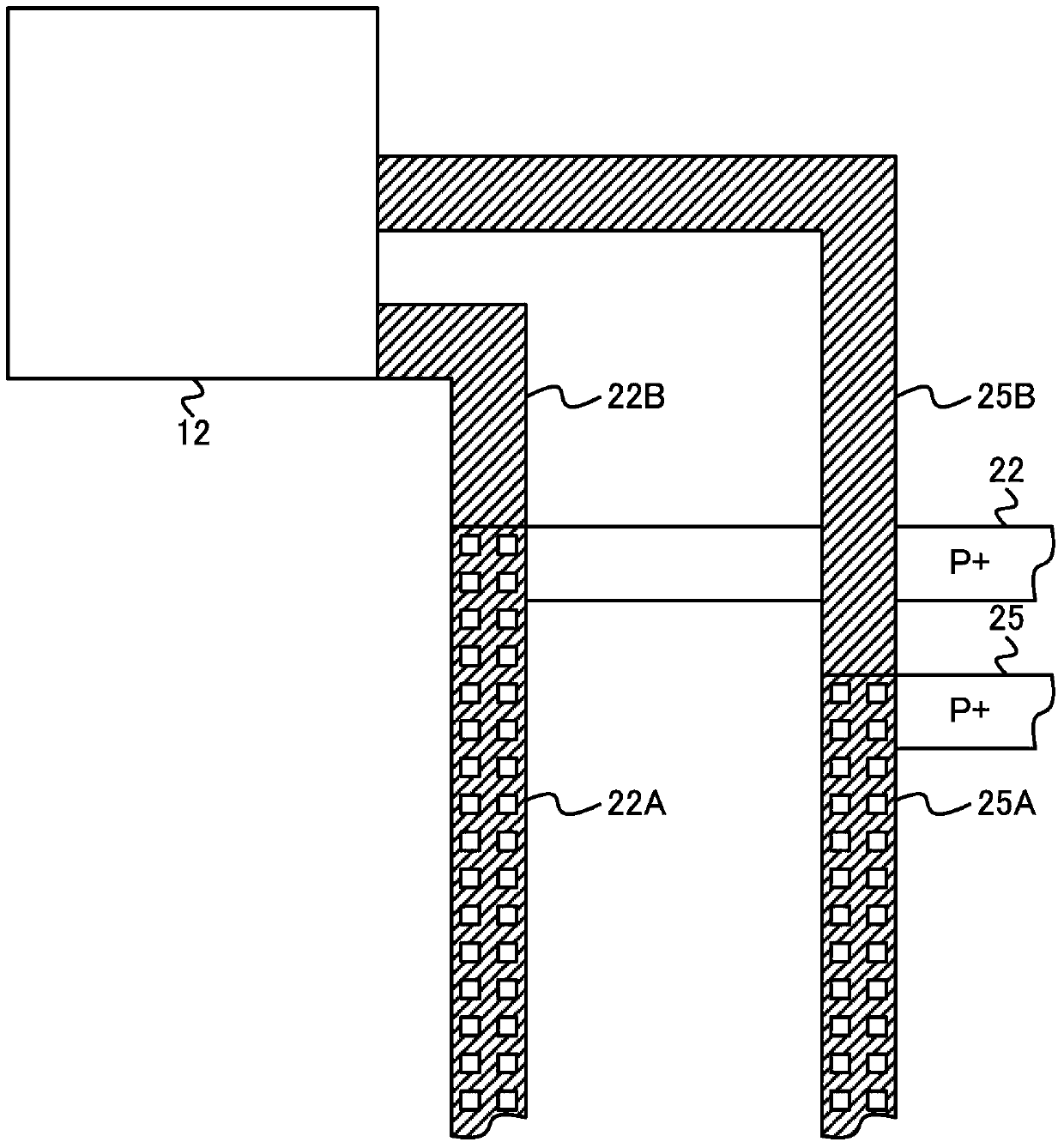

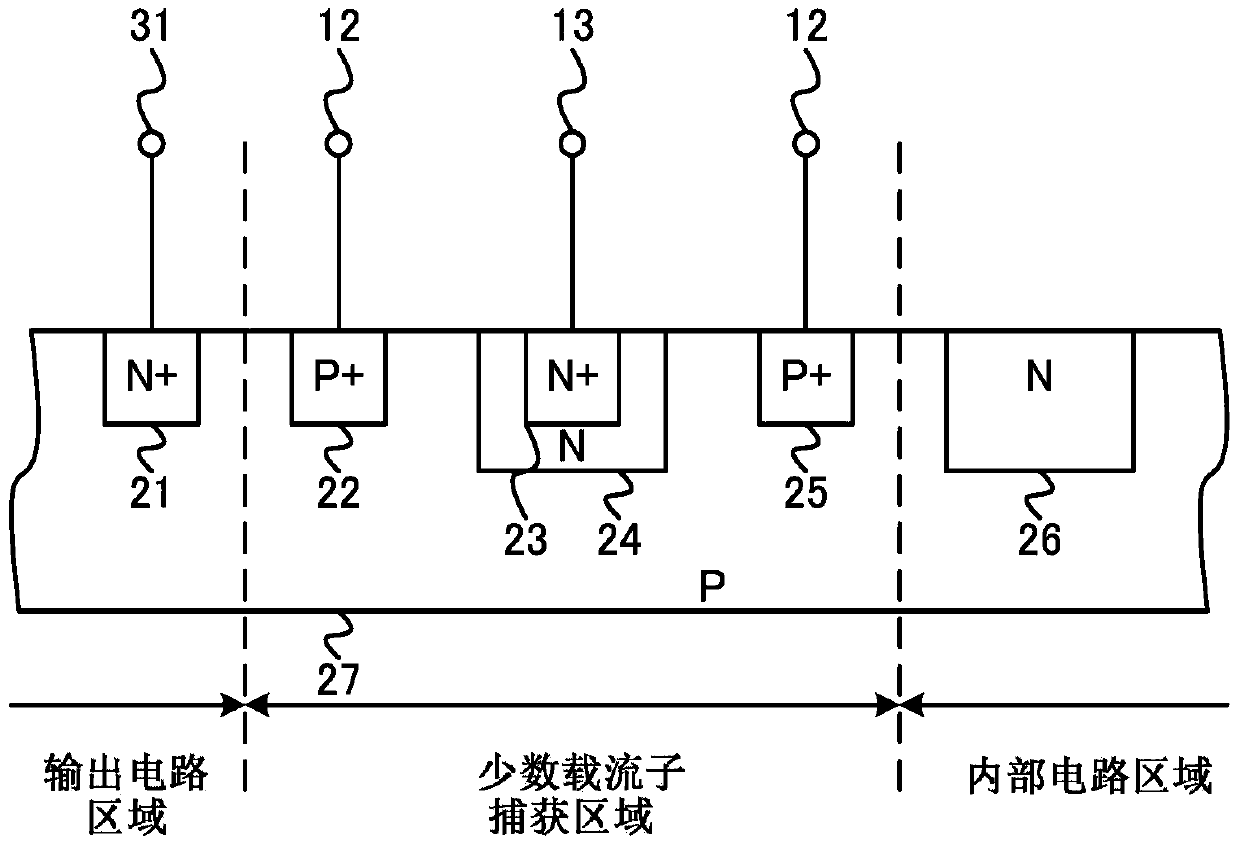

[0025] Hereinafter, embodiments of the present invention will be described with reference to the drawings. First, the structure of the semiconductor device will be described. figure 1 is a cross-sectional view showing a semiconductor device, figure 2 It is a top view showing a semiconductor device.

[0026] Such as figure 1 As shown, the semiconductor substrate 27 is composed of three regions, the ESD protection circuit region, the internal circuit region and the minority carrier trapping region. The ESD protection circuit region is used to protect the semiconductor device from the influence of ESD, and the minority carrier The carrier trapping region traps minority carriers generated in the semiconductor substrate 27 due to a surge having a negative voltage applied to the pad 11 of the input or output, the minority carrier trapping region surrounds the internal circuit area, usually forming a protective ring. The input or output pad 11, the ground pad 12, the power pad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More