Adjustable Duty Cycle Circuit

A duty cycle, adjustable technology, applied in the field of signal circuits, can solve problems such as inaccurate performance and degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In accordance with the present disclosure, techniques for adjusting the pulse width and / or duty cycle of a signal generated by a circuit are disclosed.

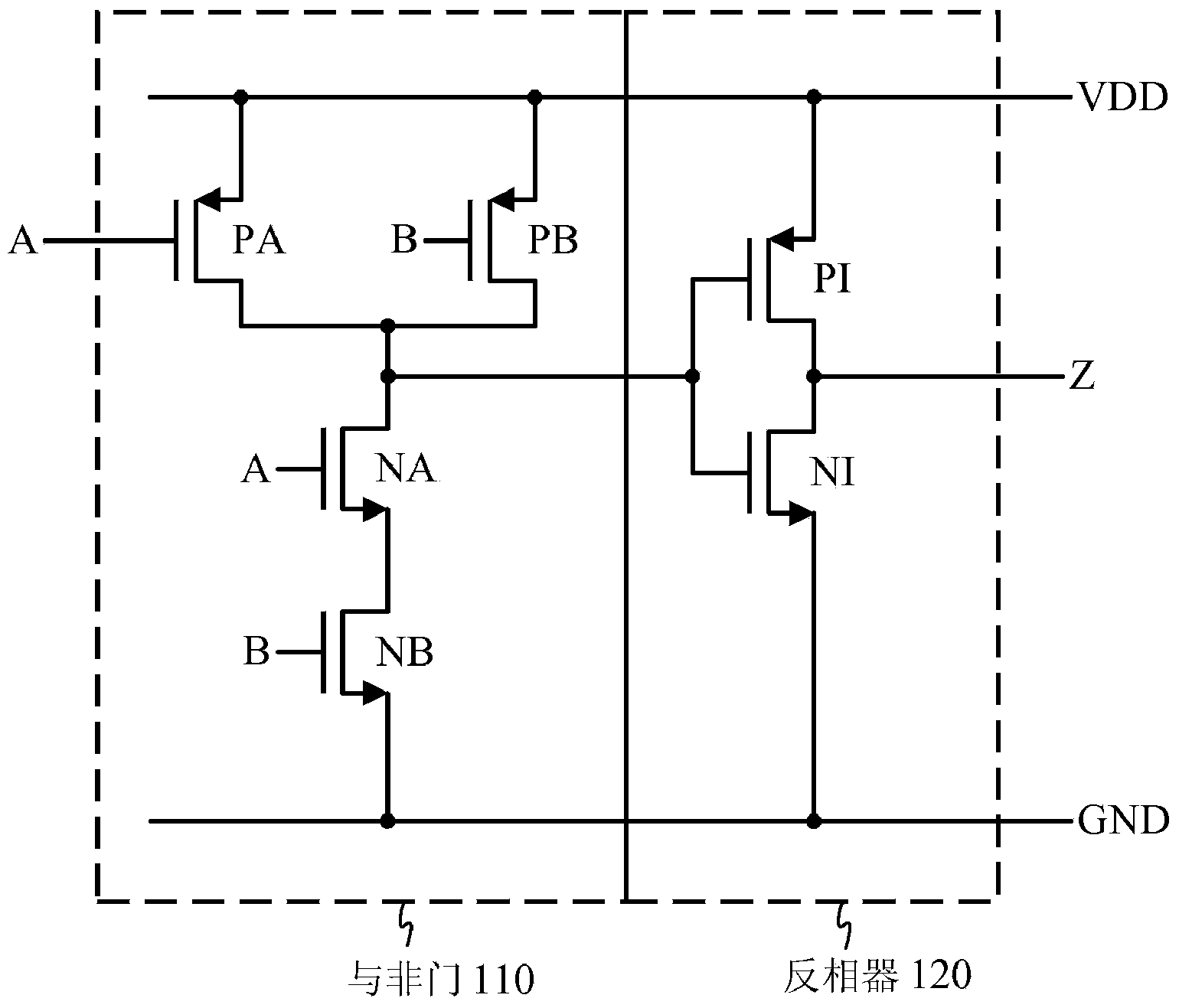

[0024] figure 1 Depicted is a circuit for generating a signal with a 25% duty cycle from an in-phase signal (A) and a quadrature-phase signal (B), each having a 50% duty cycle. exist figure 1 , PMOS transistors PA, PB and NMOS transistors NA, NB are configured as a standard two-input NAND gate 110 . Signal A and signal B are input to the NAND gate, and the output of the NAND gate is coupled to an inverter 120 to generate an output signal Z. Signal Z corresponds to the output of applying an "AND" operation to signal A and signal B.

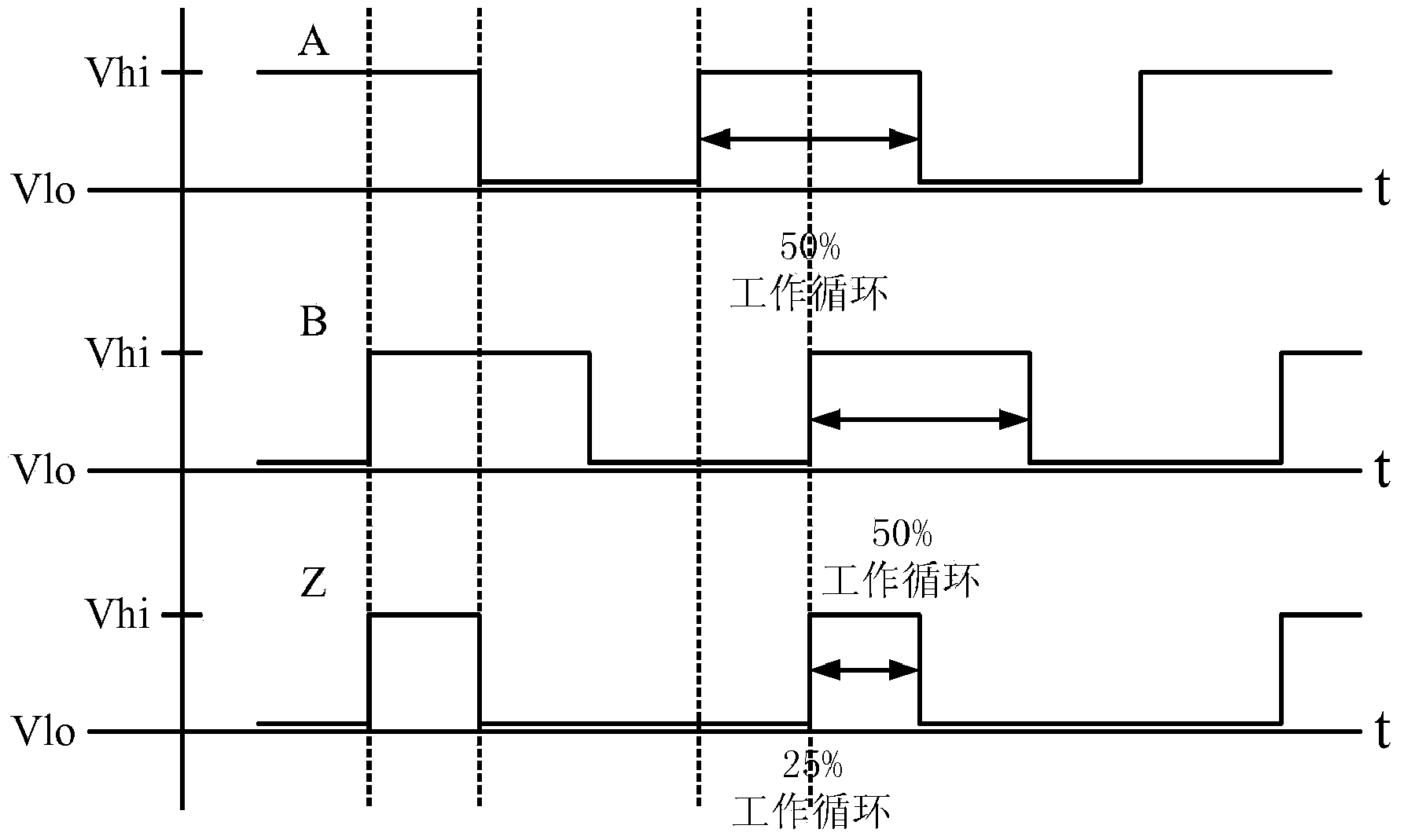

[0025] figure 2 Plot the relationship between Signal A, Signal B, and Signal Z. exist figure 2 , Signal A and Signal B each have a 50% duty cycle and have a quadrature phase relationship with each other. Signal Z, produced by applying an "AND" operation to signal A and signal B, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More