A method for calculating the testability index of a board-level circuit

A technology of index calculation and board-level circuit, applied in the direction of calculation, electrical digital data processing, special data processing application, etc., can solve the problem of not reflecting the relationship between the test and the fault location, and the inability to calculate the testability index.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Specific embodiments of the present invention will be described below in conjunction with the accompanying drawings, so that those skilled in the art can better understand the present invention. It should be noted that in the following description, when detailed descriptions of known functions and designs may dilute the main content of the present invention, these descriptions will be omitted here.

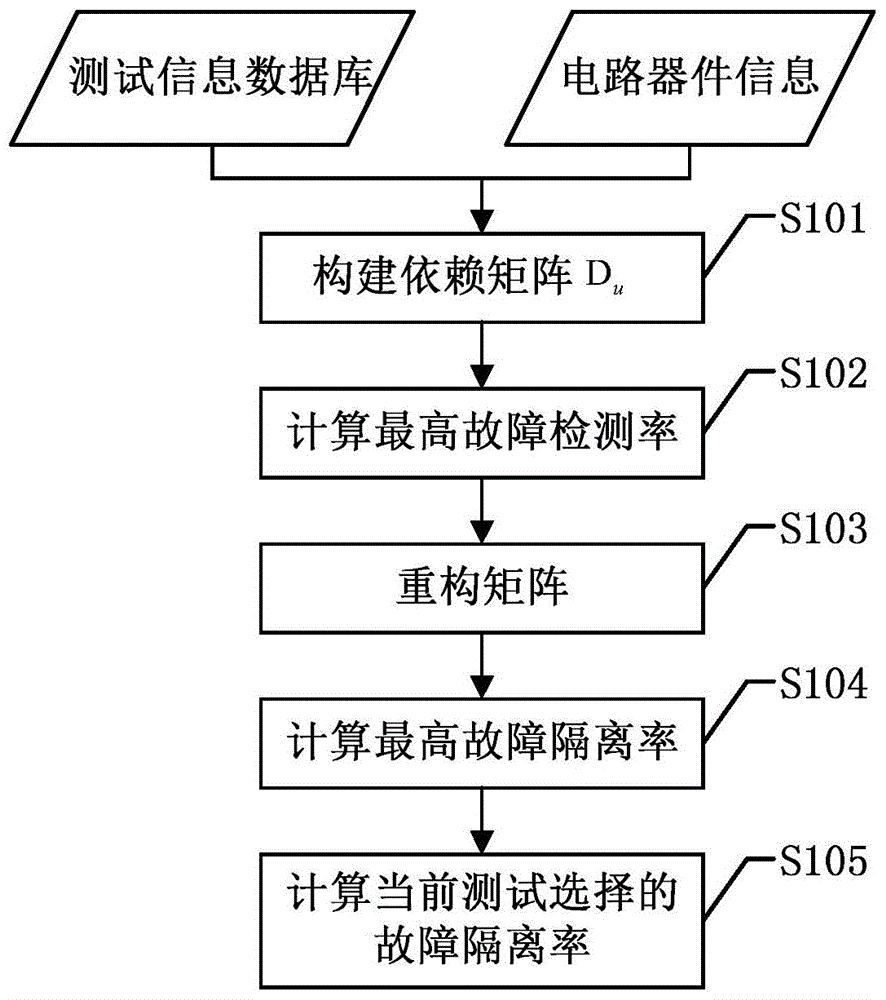

[0032] figure 1 It is a schematic flow chart of the specific implementation of the board-level circuit testability index calculation method of the present invention. Such as figure 1 As shown, the method for calculating the testability index of the board-level circuit of the present invention includes the following steps:

[0033] S101: Construct a dependency matrix D independent of signal flow u :

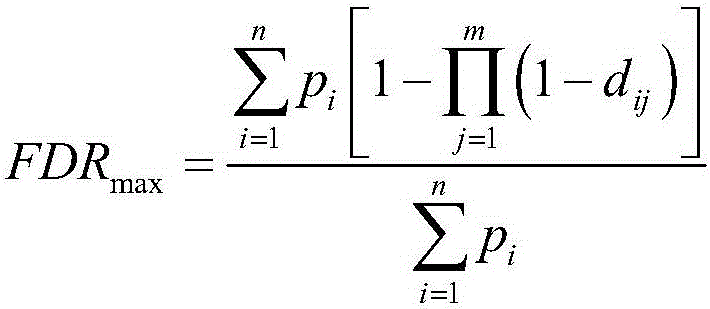

[0034] According to the test information database, including device types, failure probability of various devices, failure modes, probability of each failure mode, test ite...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More