A three-dimensional integrated circuit on-chip network routing method and system thereof

An integrated circuit and on-chip network technology, which is applied in the field of 3D integrated circuit on-chip network routing, can solve the problems of on-chip network communication performance, low system overhead of steering restrictions, etc., and achieves the effect of avoiding additional overhead, improving fairness, and loosening 3D steering restrictions.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

[0049] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

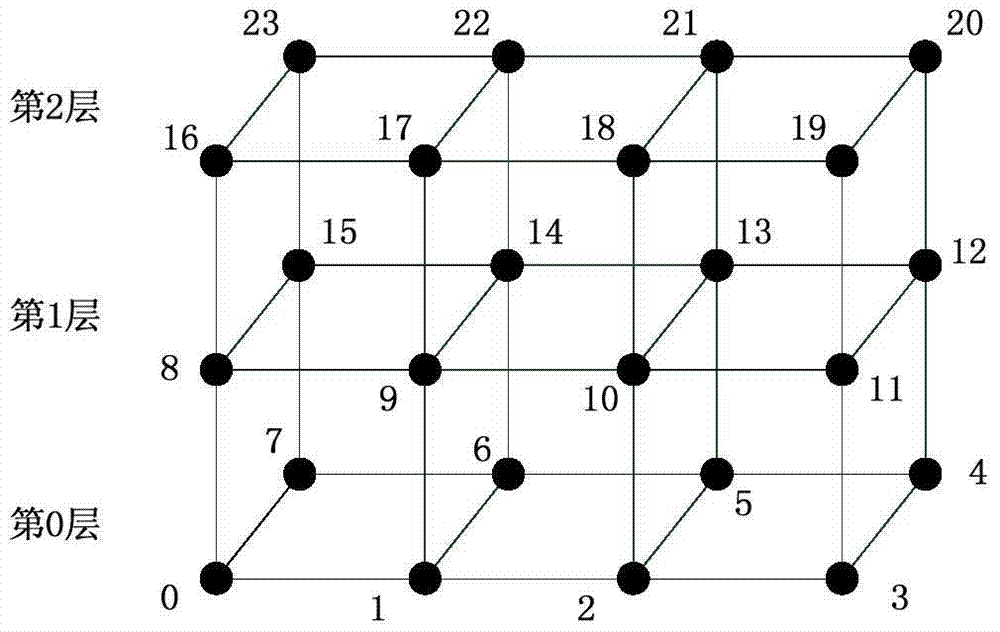

[0050] The object of the present invention is to provide a routing method for a three-dimensional integrated circuit on-chip network guided by a fair steering model. It can balance high communication performance and low system overhead on a three-dimensional integrated circuit on-chip network.

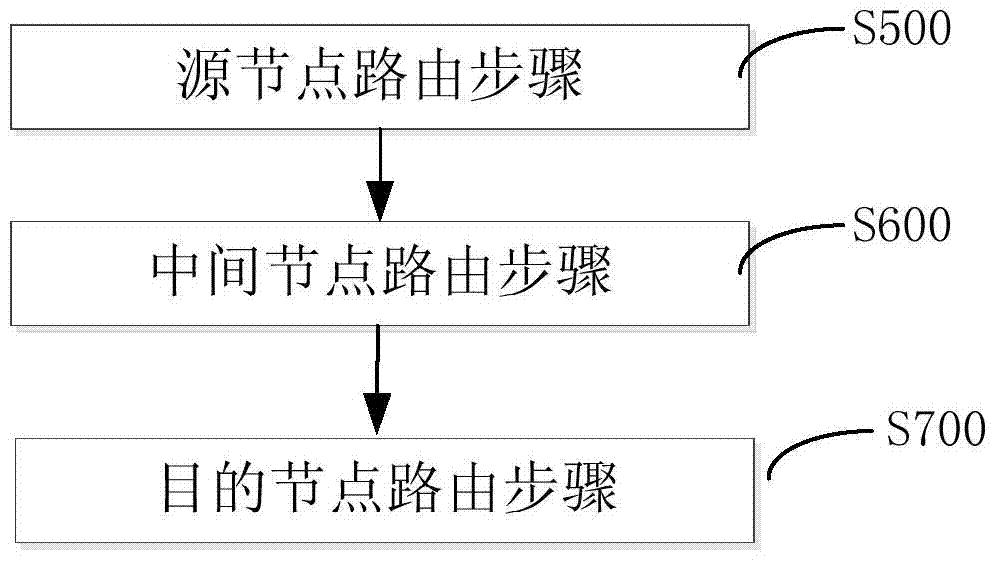

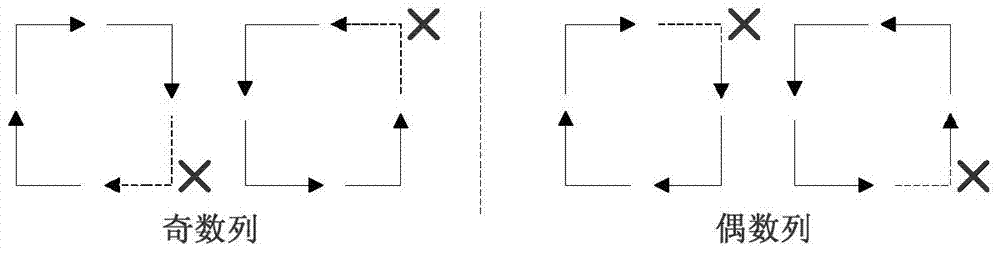

[0051] The invention provides a routing method of a three-dimensional integrated circuit on-chip network guided by a fair steering model, generally speaking, a one-way communication process in which a source node routes data packets to a destination node. Define the source node as S (Source) node, and the destination node as D (Destination) node. Key points of the pre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More