A fpga-based irig‑b code decoder and its decoding method

A decoder and B code technology, applied in FPGA-based IRIG-B code decoder and its decoding field, can solve the problems of taking up a large processing time and affecting the response of micro processing, so as to reduce noise, improve efficiency and pertinence, Effect of improving precision of judgment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

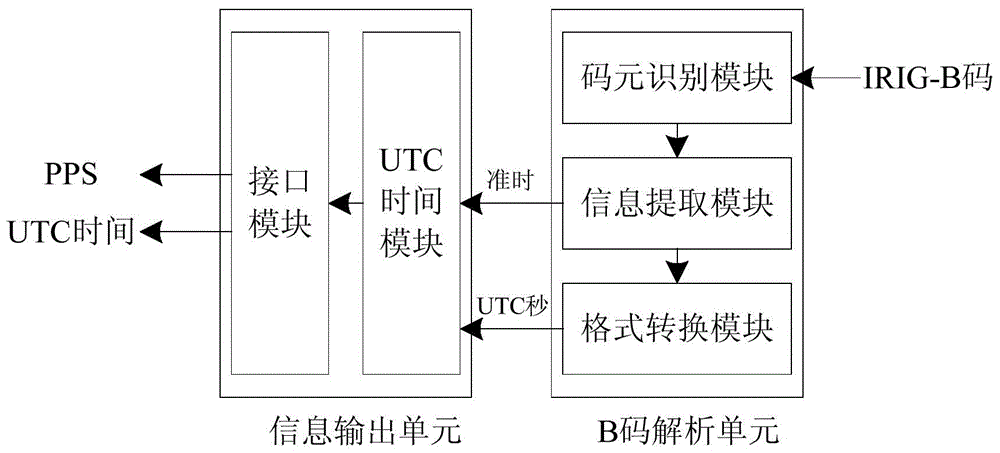

[0030] A kind of FPGA-based IRIG-B code decoder of the present invention, as figure 1 As shown, it includes a B code analysis unit and an information output unit arranged in the FPGA; the B code analysis unit includes a symbol identification module, an information extraction module and a format conversion module connected in sequence, and the information output unit includes a UTC time module connected in sequence and interface module; the symbol identification module is used to process the IRIG-B code signal input from the outside; the information extraction module is used to receive the symbol type output by the symbol identification module, and provides the punctual reference point signal to the UTC time module; the format conversion module It is used to provide the UTC second signal to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More