FPGA configuration file upgrading method and system

A technology for configuring files and upgrading files, which is applied in the direction of program control devices, program loading/starting, etc., and can solve problems such as increasing hardware costs and adding third-party devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

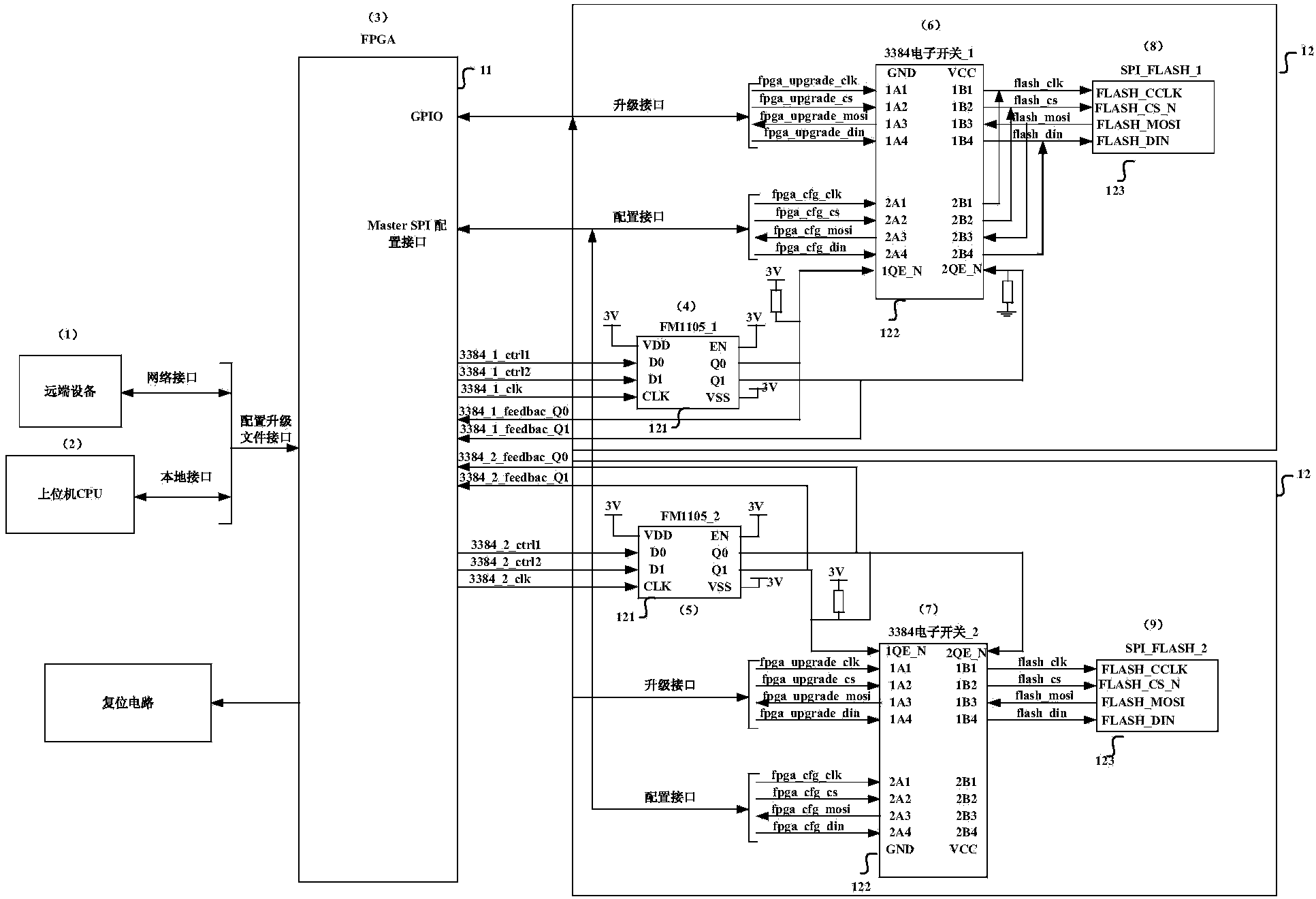

Embodiment Construction

[0051] Ferroelectric memory is a non-volatile memory with a special process, which uses artificially synthesized lead-zirconium-titanium (PZT) materials to form memory crystals. When an electric field is applied to the ferrotransistor, the central atom follows the field and stops at the low-energy state I. Conversely, when an electric field reversal is applied to the same ferrotransistor, the central atom moves in the crystal along the direction of the electric field and stops. In another low energy state II position. A large number of central atoms move and couple in the crystal unit cell to form ferroelectric domains, and the ferroelectric domains form polarized charges under the action of an electric field. The polarization charge formed by the ferroelectric domain reversal under the electric field is higher, and the polarization charge formed by the ferroelectric domain without reversal under the electric field is lower. The binary stable state of this ferroelectric materi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More