Virtualization electrical characteristic optimization test (VTRIM) method

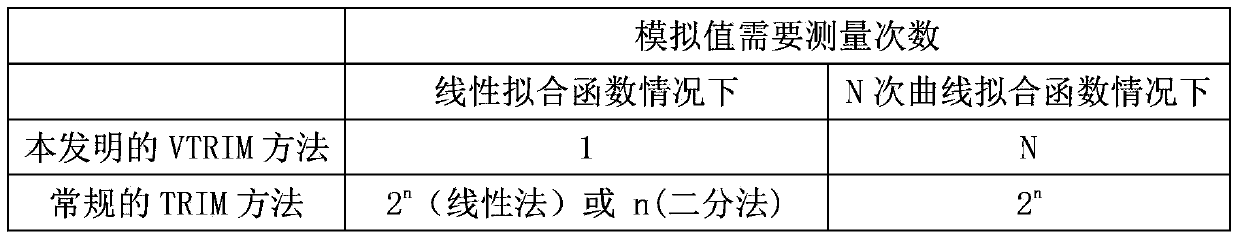

A test method and technology of electrical characteristics, applied in the field of virtualized electrical characteristics optimization test, can solve problems such as long test time, and achieve the effect of solving many limitations of test equipment and solving low test efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

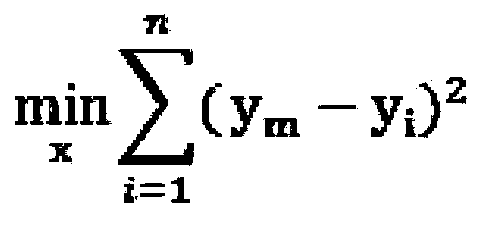

[0010] The process of the virtualized electrical characteristic optimization test (VTRIM) method of the present invention is as follows:

[0011] 1. Historical data modeling

[0012] Taking the case of the linear fitting function as an example, firstly, the measured analog values (electrical optimization parameters such as voltage value, current value, frequency value, etc., including at least one of the parameters) measured by all debug sample chips are fitted into the linear function of each chip y=ax+b, where x represents a digital parameter (DAC) value and y represents a measured value of an electrical optimization parameter. Then, based on the slope data (a 1 ,...a q ) Calculate the standard deviation σ of the sample, and estimate the process float Δ according to the data of the process characteristic parameter (PCM) (generally, the device resistance, capacitance, and leakage current value that affects the electrical parameters), and complete the distribution verifica...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More