Management method for instruction cache and processor

An instruction cache and processor technology, applied in the computer field, can solve problems such as no improvement, frequent occurrence, insufficient shared I-Cache resources, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

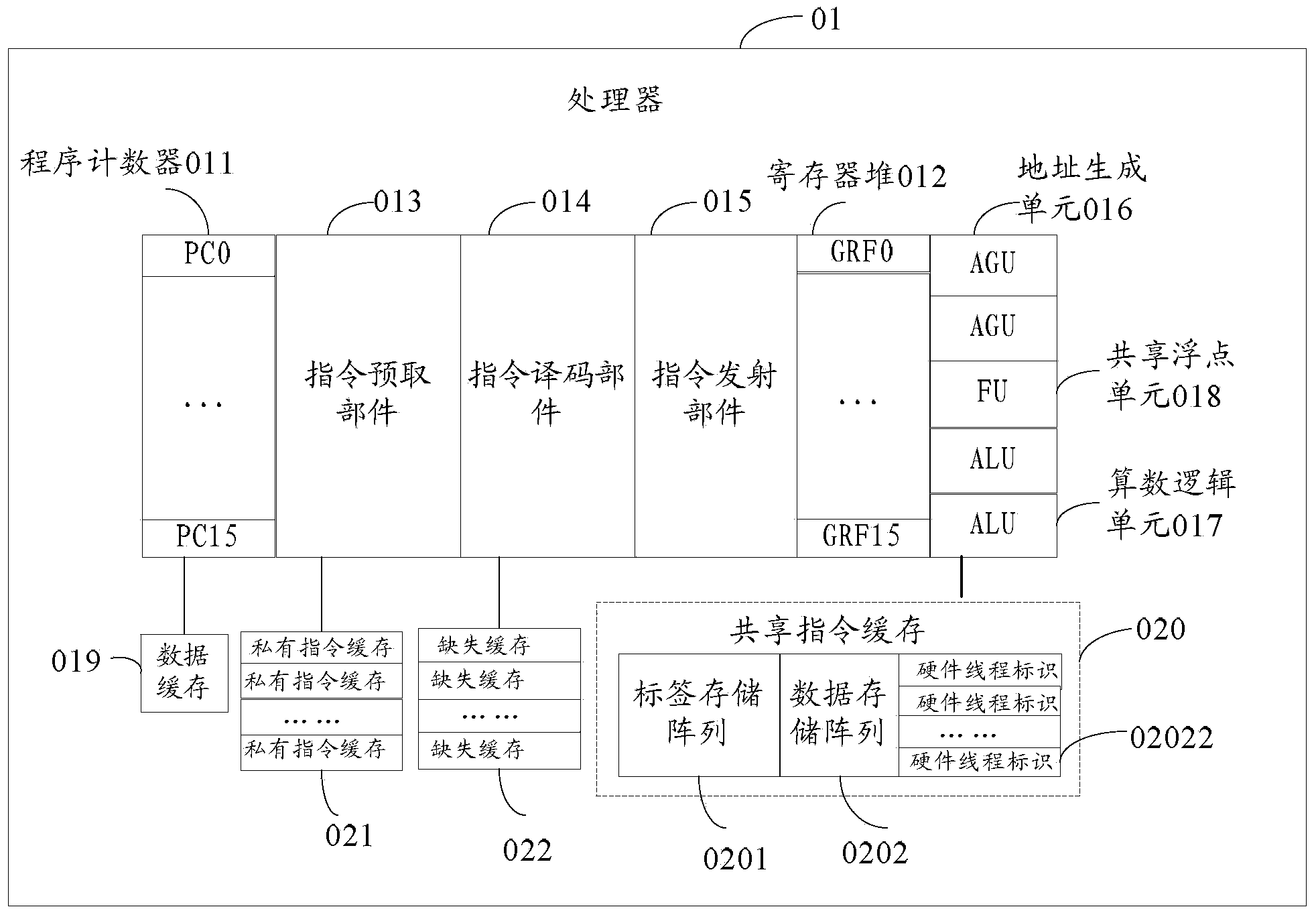

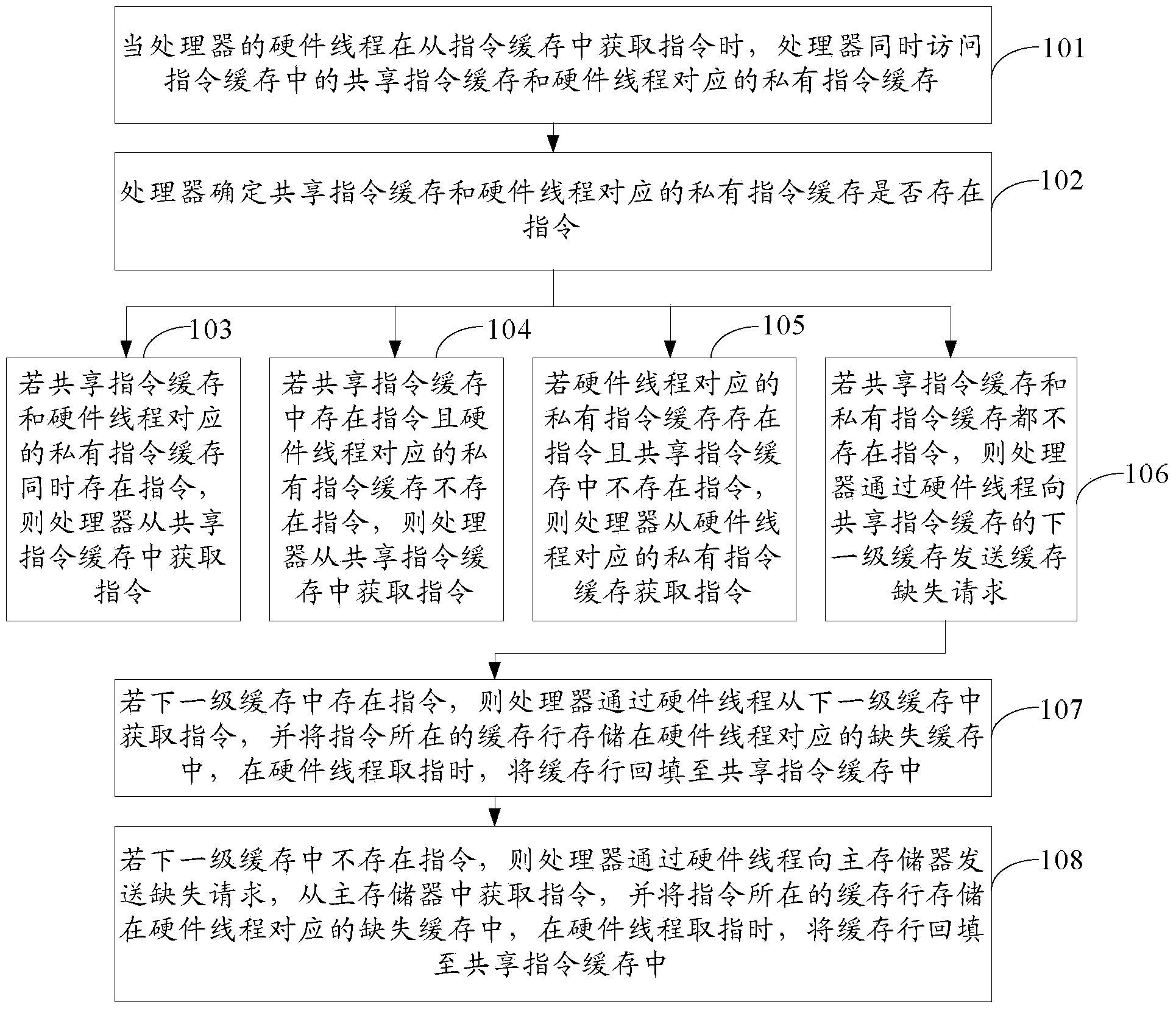

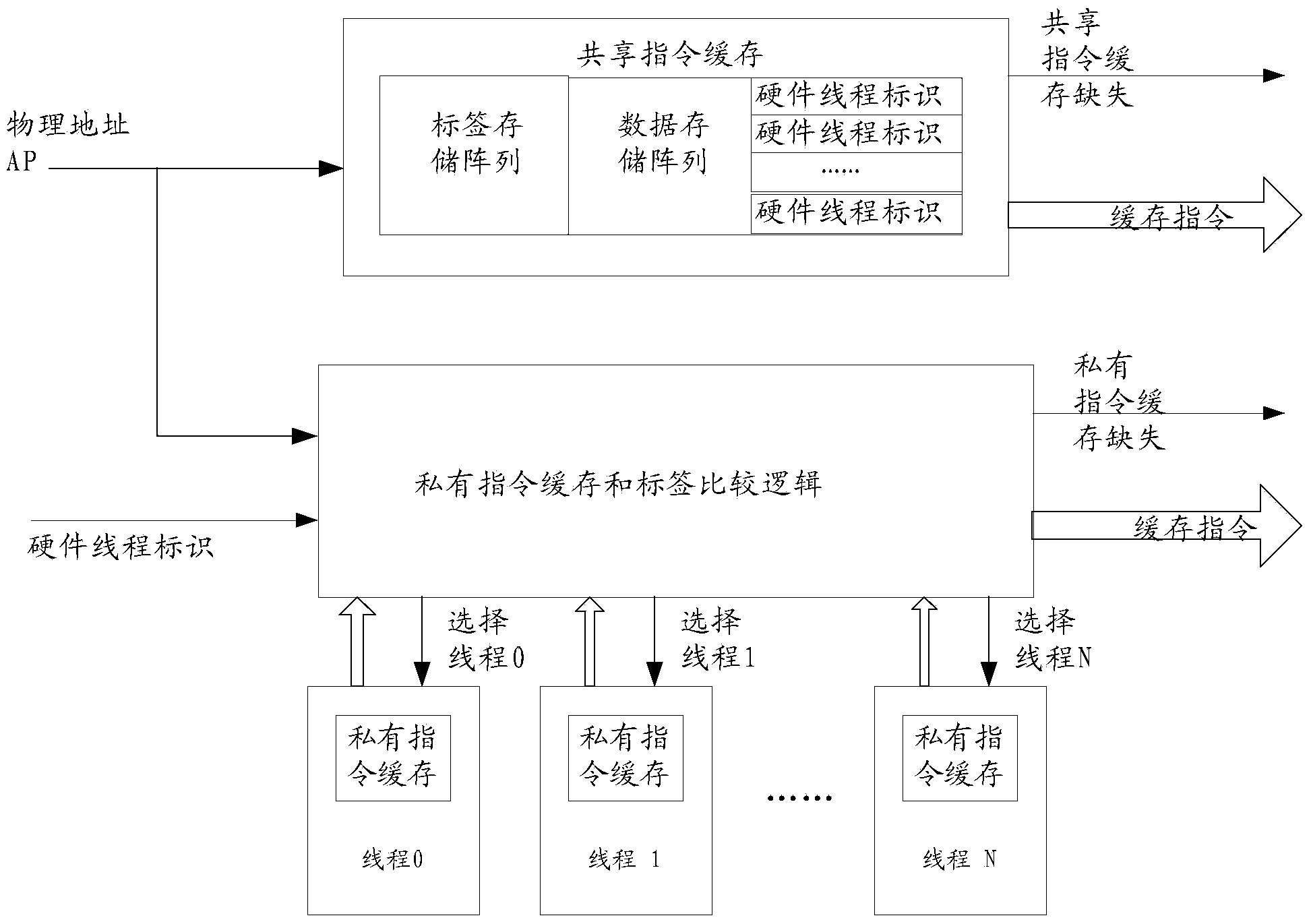

[0039] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0040] In the design of modern multi-threaded processors, as the number of hardware threads increases, there will be insufficient shared resources for each hardware thread. For example, for the important shared resource of L1 (Level 1) Cache in Cache Even more so with resources. The instruction cache capacity of the L1Cache assigned to each hardware thread is too small, there will be misses in the L1, and the L1 miss rate will increase, resulting in increased ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More