A clock source for serializer/deserializer based on clock manager and fpga

A manager and deserializer technology, applied in the field of remote sensing camera video processors, can solve problems affecting image quality, clock instability, high bit error rate, etc., to avoid negative impacts, ensure phase consistency, and reduce signal delays Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

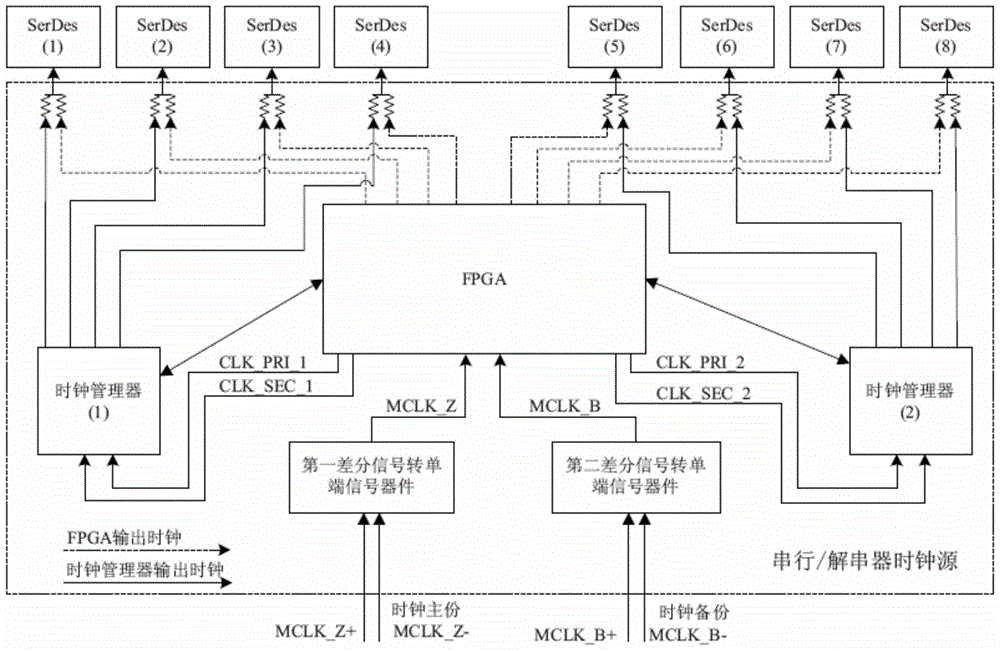

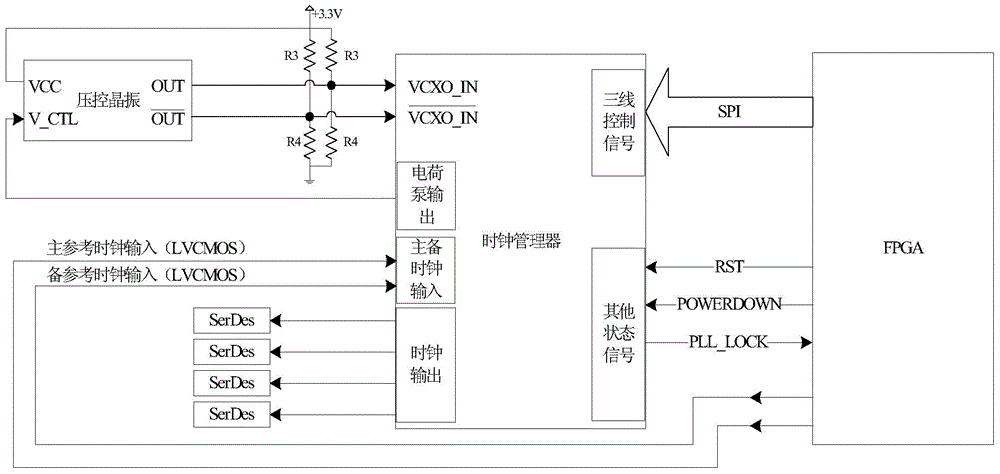

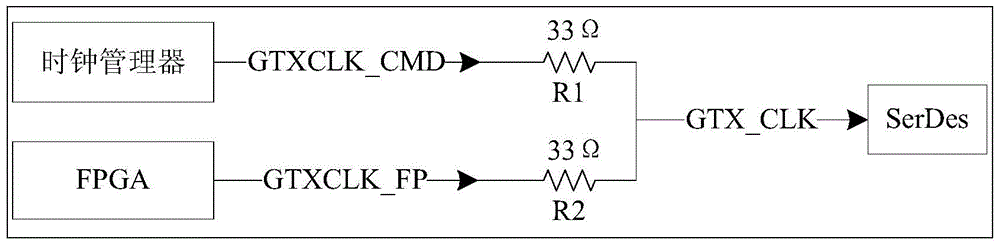

[0022] Due to the high-speed data transmission requirements of the system, and at the same time, in order to reduce the size of the system and the number of external cables, the use of SerDes devices has become a better data transmission method, because the SerDes devices will serialize parallel data. Perform frequency multiplication processing, which has very high requirements on the clock, so the two clock managers and the FPGA provide clock sources that are mutually backup.

[0023] Such as figure 1 Shown is the SerDes device clock source based on the clock manager and FPGA proposed by the present invention. In this embodiment, the clock source is provided by 8 SerDes (SerDes1, SerDes2, SerDes3, SerDes4, SerDes5, SerDes6, SerDes7, SerDes8) clock signal.

[0024] The clock source includes FPGA, a first clock manager, a second clock manager, a first switch group including 8 switches, a second switch group including 8 switches, a first differential signal-to-single-ended sign...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More