Voltage compensation oscillator circuit

A technology of voltage compensation and oscillator, which is applied in the field of voltage compensation oscillator circuit, can solve the problems of faster oscillation frequency, affecting the accuracy of oscillation frequency, and the oscillation frequency is easily affected by the power supply voltage, so as to reduce the increase range and improve The effect of precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

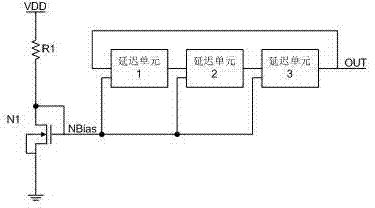

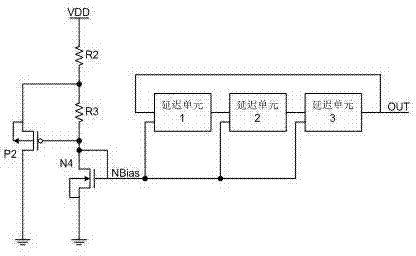

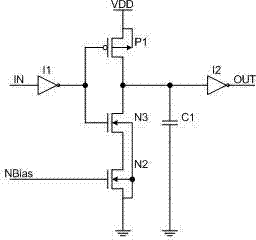

[0011] See figure 2 , image 3 As shown, a voltage compensation oscillator circuit includes a resistor R2, one end of the resistor R2 is connected to the power supply VDD, the other end of the resistor R2 is connected to the source end of the PMOS transistor P2, one end of the resistor R3, the other end of the resistor R3 and the gate end of the PMOS transistor P2 After being connected, connect the drain end of NMOS transistor N4, connect the gate end and drain end of NMOS transistor N4, and then connect multiple delay units, and multiple delay units are connected to form a ring, and the drain end of PMOS transistor P2 and the source end of NMOS transistor N4 are respectively Grounding; the delay unit includes three, respectively the first delay unit, the second delay unit, and the third delay unit, the output of the first delay unit is connected to the input of the second delay unit, and the output of the second delay unit is connected to the second delay unit The input end...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More