ROM read data internal clock pulse generation circuit and method

An internal clock and circuit generation technology, applied in read-only memory, information storage, static memory, etc., can solve the problems of rising ROM power consumption and slow ROM reading speed, reducing load size, reducing ROM power consumption and reducing ROM power consumption. The effect of read time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

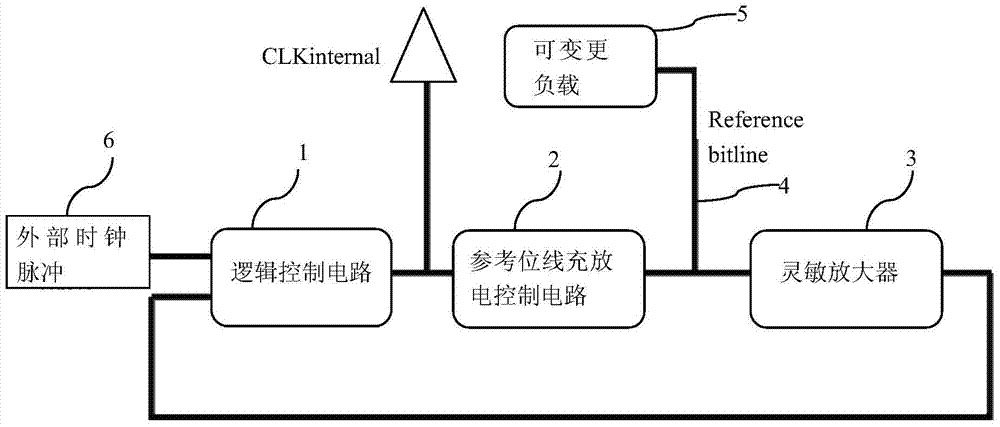

[0031] Such as image 3 The above is a schematic diagram of the internal clock pulse generation circuit for ROM read data in the embodiment of the present invention; the internal clock pulse generation circuit for ROM read data in the embodiment of the present invention includes: a logic control circuit 1, a reference bit line 4 charge and discharge control circuit 2, and a sensitive amplifier circuit 3. The reference bitline is Reference bitline4;

[0032] The load of the reference bit line 4 is a changeable load 5, and the changeable load 5 is adjusted according to the maximum bit line load in the ROM circuit after the ROM data code is written into the ROM circuit.

[0033] The charge and discharge control circuit 2 of the reference bit line 4 is used to charge and discharge the reference bit line 4 and obtain a charge and discharge time, and the charge and discharge time is determined by the variable load 5 .

[0034] The internal clock pulse used to read the ROM circuit i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More