Gate Protection Caps and Method of Forming the Same

A technology of protective cover and gate, applied in electrical components, circuits, semiconductor devices, etc., can solve problems such as reducing the yield of integrated circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

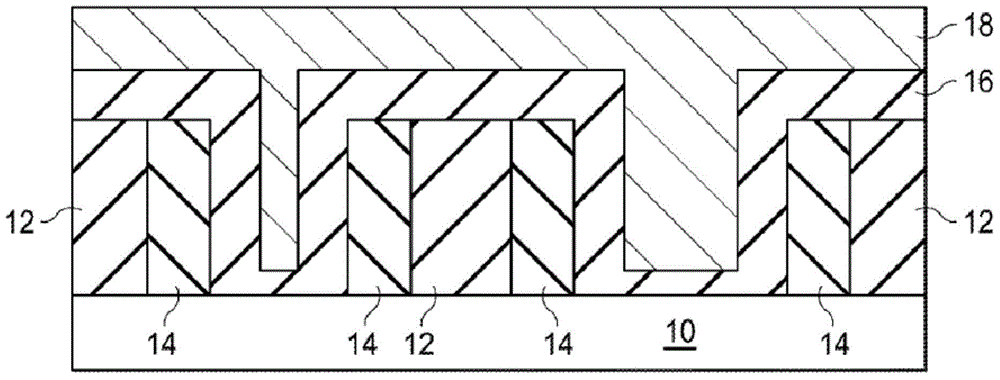

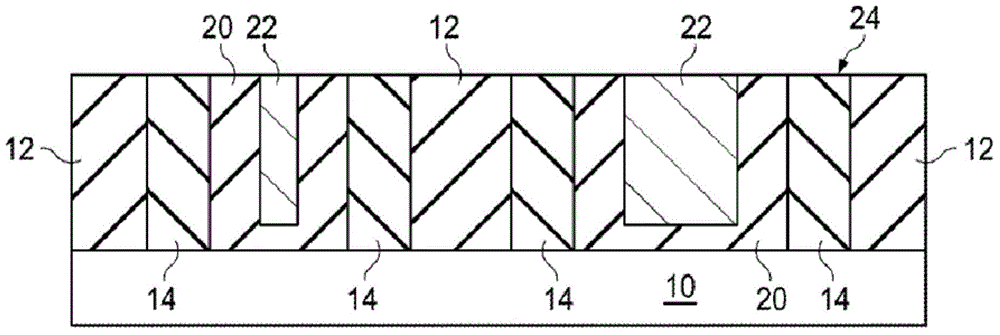

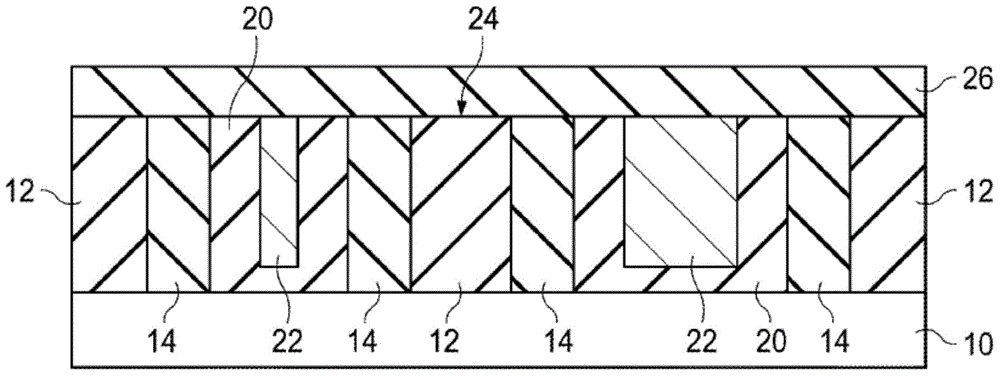

[0048] The making and using of this embodiment are discussed in detail below. It should be appreciated, however, that the present invention provides many applicable concepts that can be embodied in a wide variety of specific contexts. The specific embodiments discussed are merely illustrative of specific ways to make and use the disclosed subject matter, and do not limit the scope of the various embodiments.

[0049] Embodiments will be described with reference to a specific context, namely, a gate-last process for forming transistors, such as fin field effect transistors (FinFETs). However, other embodiments may also apply to other structures and processes. Throughout the drawings and the following discussion, like reference numbers refer to like components. Although the methods discussed herein are described as being performed in a particular order, other method embodiments may be performed in any logical order. Furthermore, it will be apparent to those of ordinary skill ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More