A data processing method and processor

A data processing and processor technology, applied in the computer field, can solve problems such as inability to combine transaction memory, and achieve the effects of improving operating performance and scalability, speeding up execution efficiency, and improving execution efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

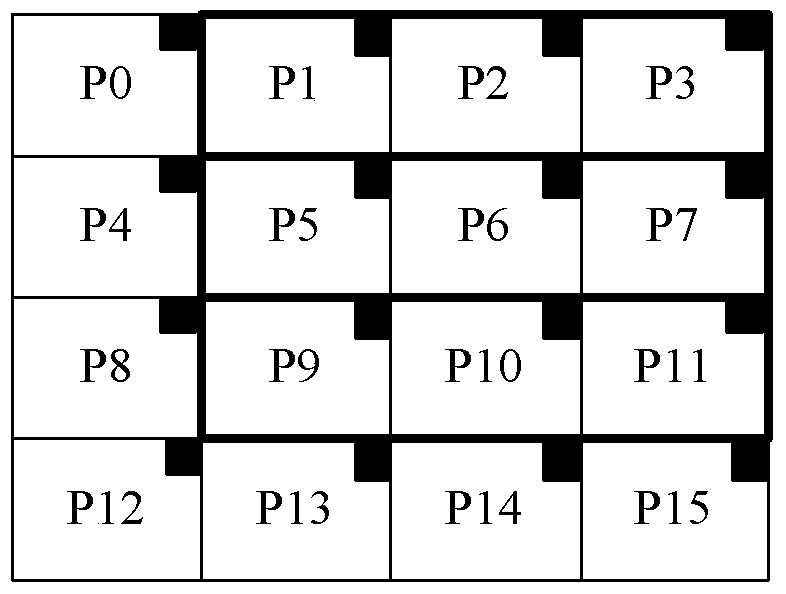

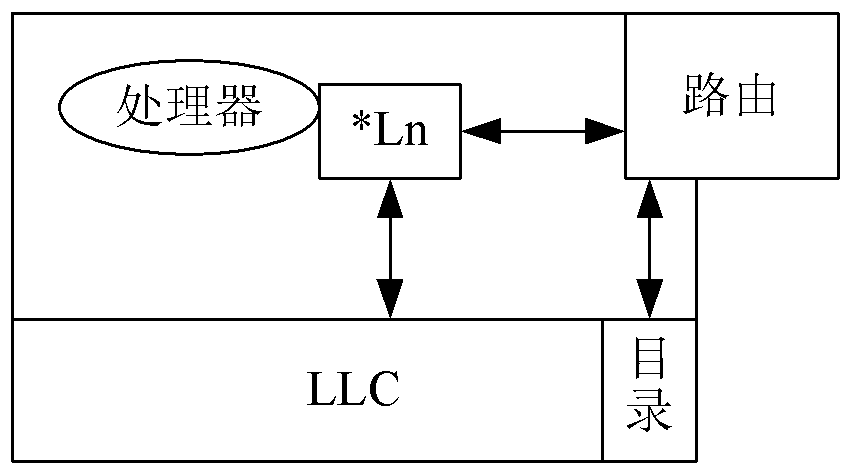

[0064] Embodiment 1. A data processing method, such as image 3 shown, including:

[0065] S1. The first processor starts transaction processing, and reads the first data into the private cache;

[0066] S2. The first processor writes the first data in the private cache, and starts submitting the transaction memory after completion;

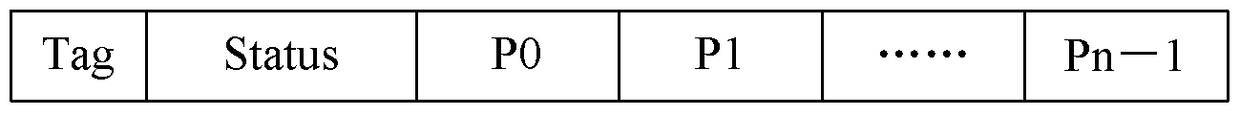

[0067] S3. If the last modification of the first data before being written by the first processor is performed by the second processor, write the first data in the private cache of the first processor to In the LLC, invalidating the first data in the private cache of the first processor;

[0068] S4. The transaction memory is submitted.

[0069] In this embodiment, the processor that updated the first data last before the first processor write operation can be known according to the first status indication string of the cache line of the first data in the LLC directory; if it is the processor, It can be processed according to the existing sch...

Embodiment 2

[0132] Embodiment 2. A processor applied in a multi-core processing device, comprising:

[0133] private cache, submission unit;

[0134] A reading unit, configured to read the first data into the private cache when the processor starts transaction processing;

[0135] A write operation unit, configured to perform a write operation on the first data in the private cache, and instruct the commit unit to start committing the transactional memory after completion;

[0136] The invalidation unit is used for when the commit unit starts committing the transaction memory and before completing the commit of the transaction memory, if the last change of the first data before being written by the processor is performed by other processors, then writing the first data in the private cache to the LLC, and invalidating the first data in the private cache of the processor.

[0137] In an implementation manner of this embodiment, the processor may further include:

[0138] A setting unit,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More