A Method of Instruction Dependency Detection in Superscalar Processor

A processor and superscalar technology, applied in the detection of faulty computer hardware, error detection/correction, electrical digital data processing, etc., can solve the problems of related logic occupying a lot of resources, increasing module area, and high hardware overhead cost , to achieve the effect of reducing hardware overhead and reducing module area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The following describes the implementation of the present invention in detail with reference to the drawings and embodiments.

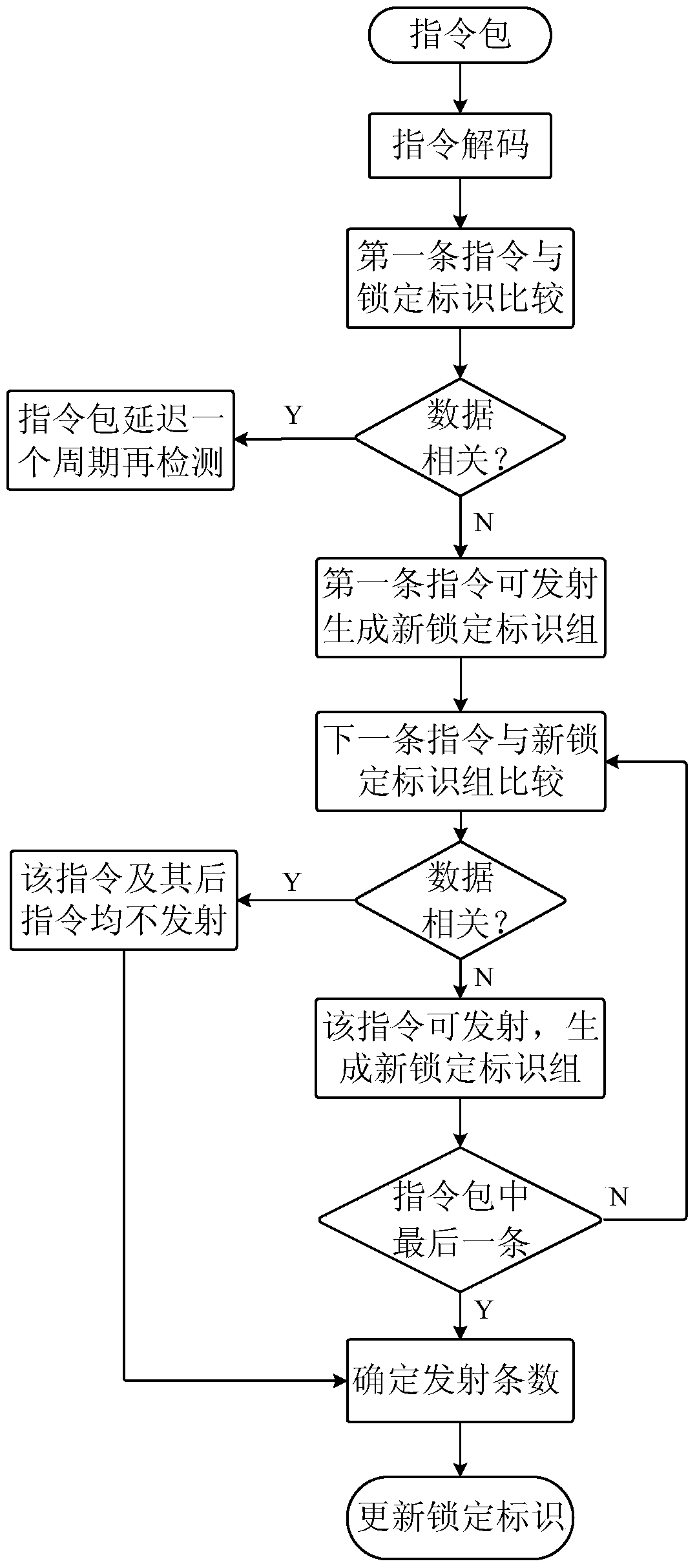

[0021] Such as figure 1 As shown, the method for detecting instruction dependency in a superscalar processor in this embodiment specifically includes the following steps:

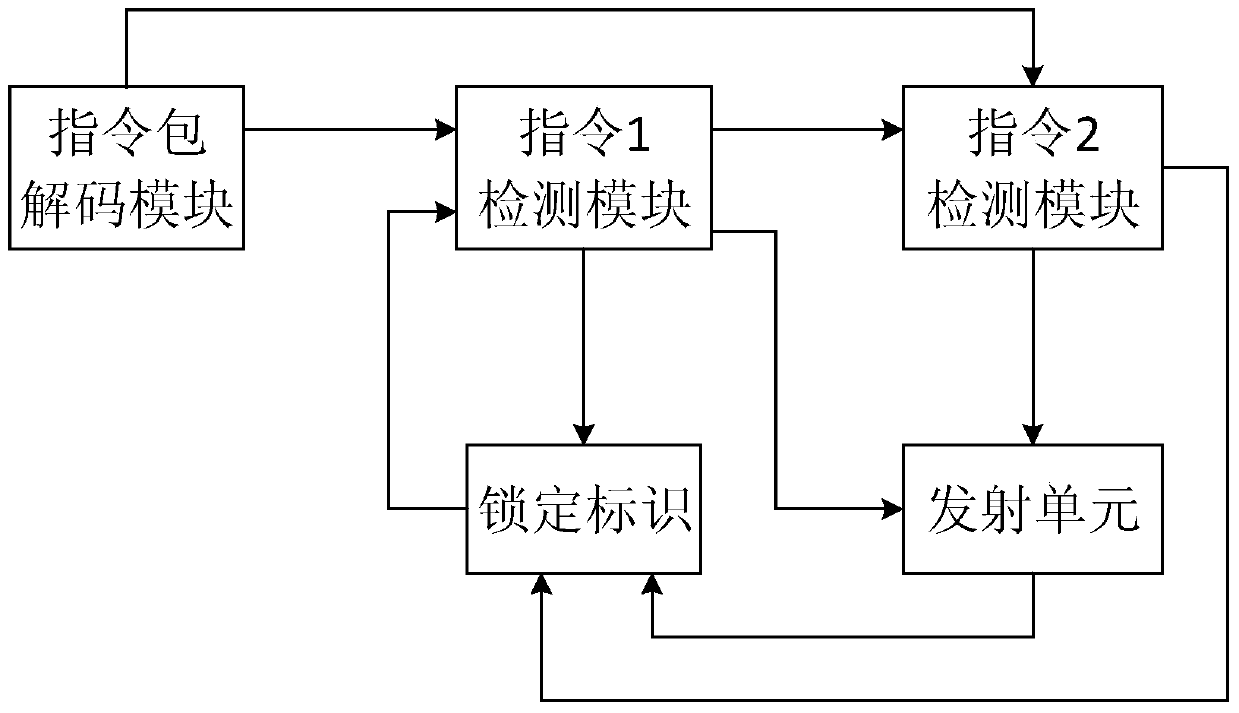

[0022] The specific implementation of this embodiment in the dual emission processor is as follows figure 2 As shown, this embodiment can not only determine whether two instructions in an instruction packet can be transmitted at the same time, but also can detect whether there is data correlation between two sets of instructions in adjacent instruction packets. The specific implementation includes the following steps:

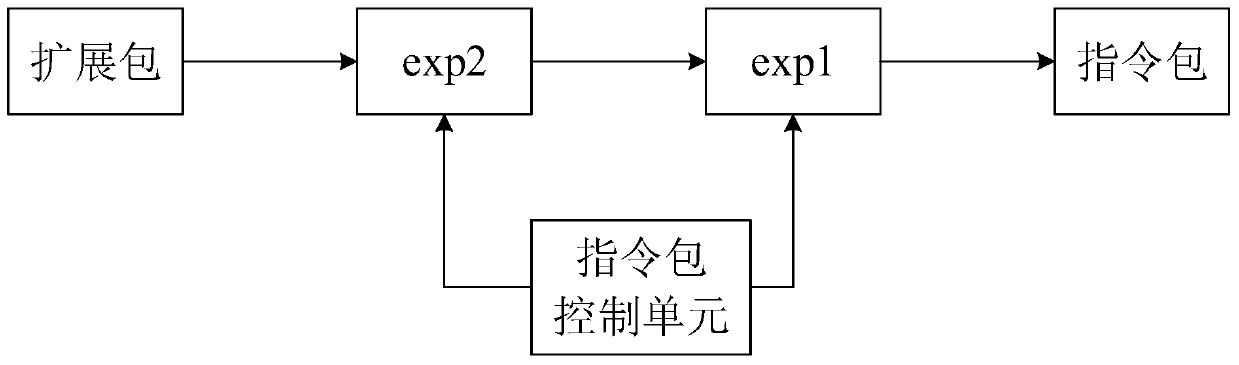

[0023] (1) Get the instruction packet, the method of obtaining the instruction packet is as follows image 3 As shown, the cache packet transfers the instructions to the cache packet 2 and the cache packet 1 level by level, and finally passes to the instruction pac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More