Memory testing method for reducing cache hit rate

A cache hit rate and memory testing technology, applied in the field of memory testing to reduce cache hit rate, can solve problems such as the impact of test effectiveness, and achieve the effects of improving effectiveness, optimizing memory testing methods, and reducing cache hit rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Embodiments of the present invention will be described below with reference to the drawings. Elements and features described in one drawing or one embodiment of the present invention may be combined with elements and features shown in one or more other drawings or embodiments. It should be noted that representation and description of components and processes that are not related to the present invention and known to those of ordinary skill in the art are omitted from the drawings and descriptions for the purpose of clarity.

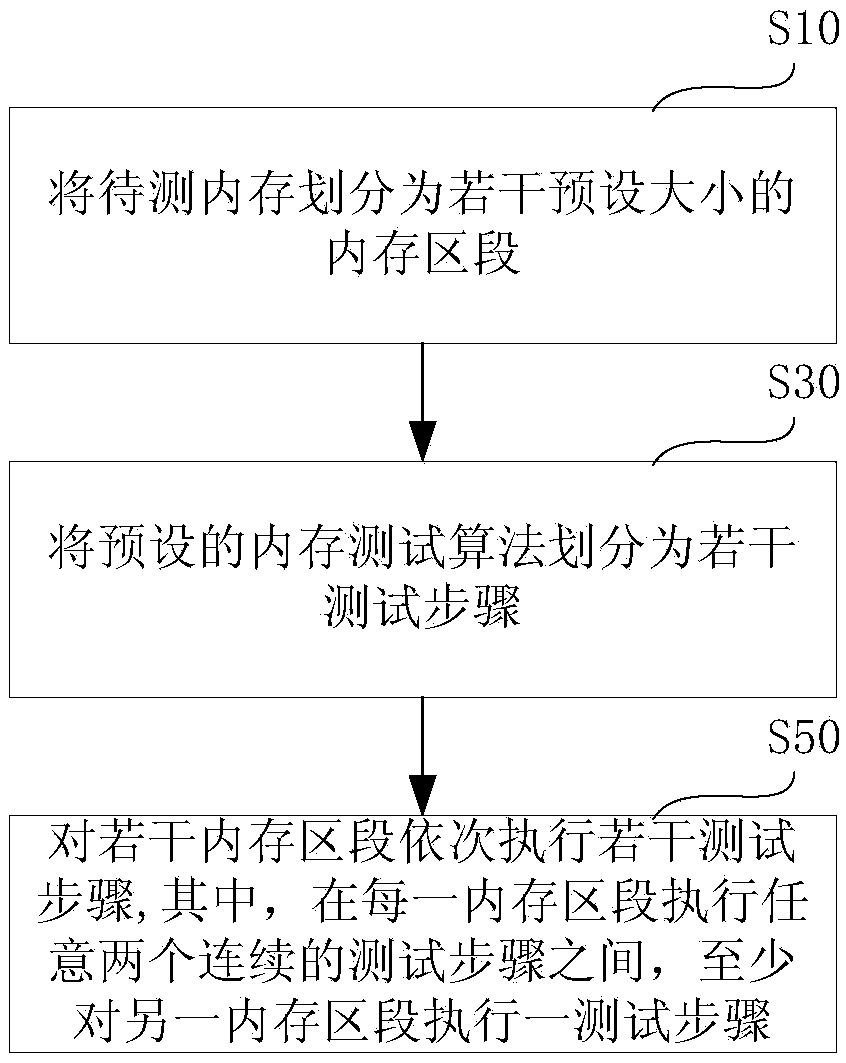

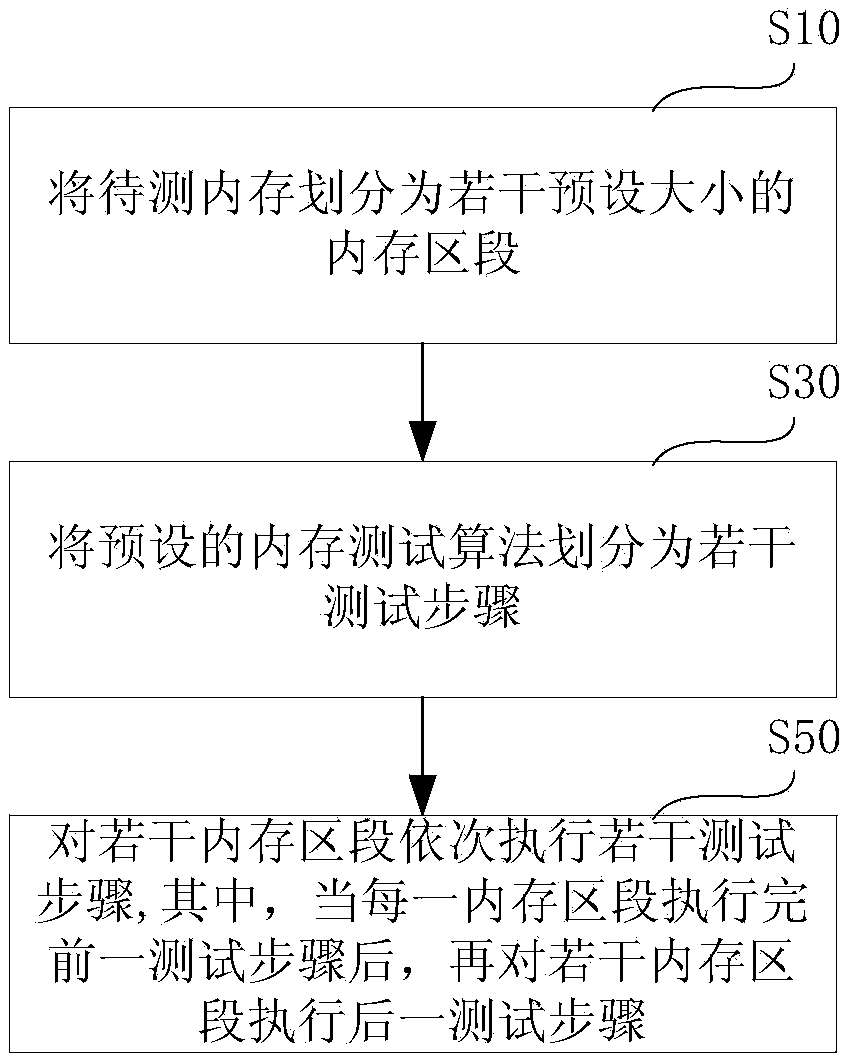

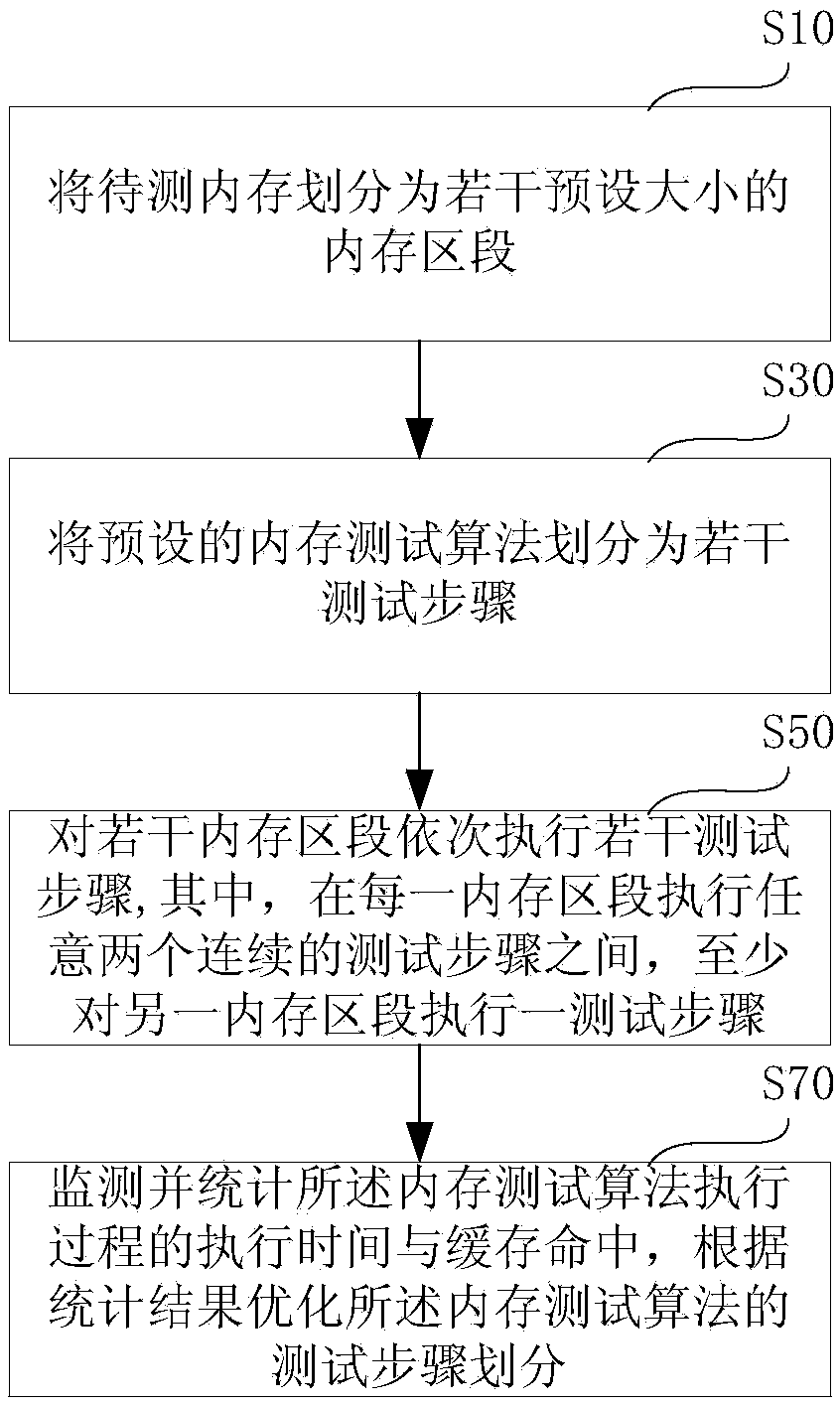

[0018] figure 1 It is a flowchart of a memory testing method for reducing a cache hit rate provided by an embodiment of the present invention.

[0019] Such as figure 1 As shown, in this embodiment, the memory test method for reducing the cache hit rate provided by the present invention includes:

[0020] S10: Divide the memory to be tested into several memory segments with preset sizes;

[0021] S30: Divide the preset memory test algorithm int...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More