CRC verification circuit and verification method suitable for 64-bit bus width

A technology for verifying circuit and bus bit width, which is applied in the fields of electrical digital data processing, generation of response errors, and error detection of redundant codes, etc. Effects of small circuit area, increased speed, and reduced dynamic power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

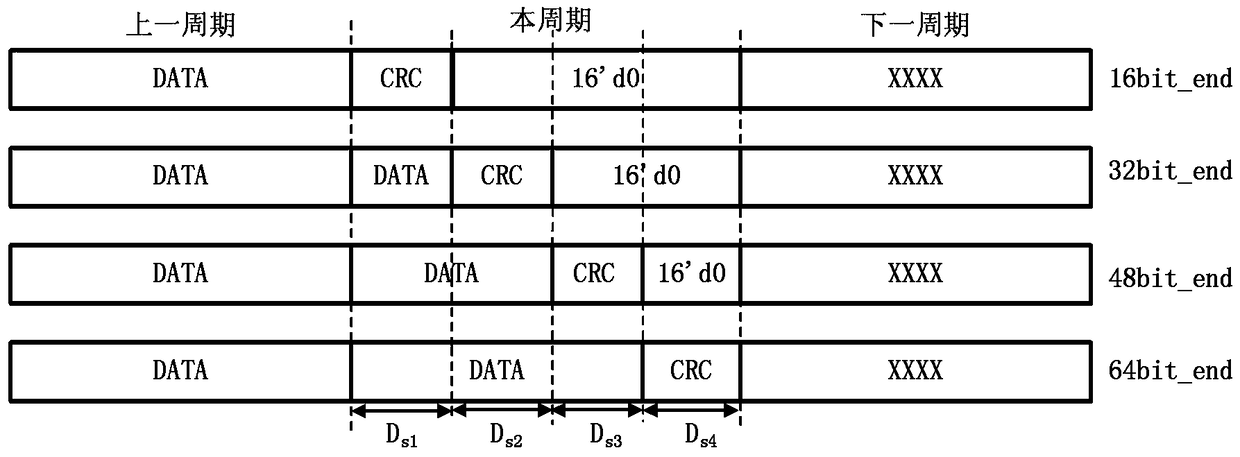

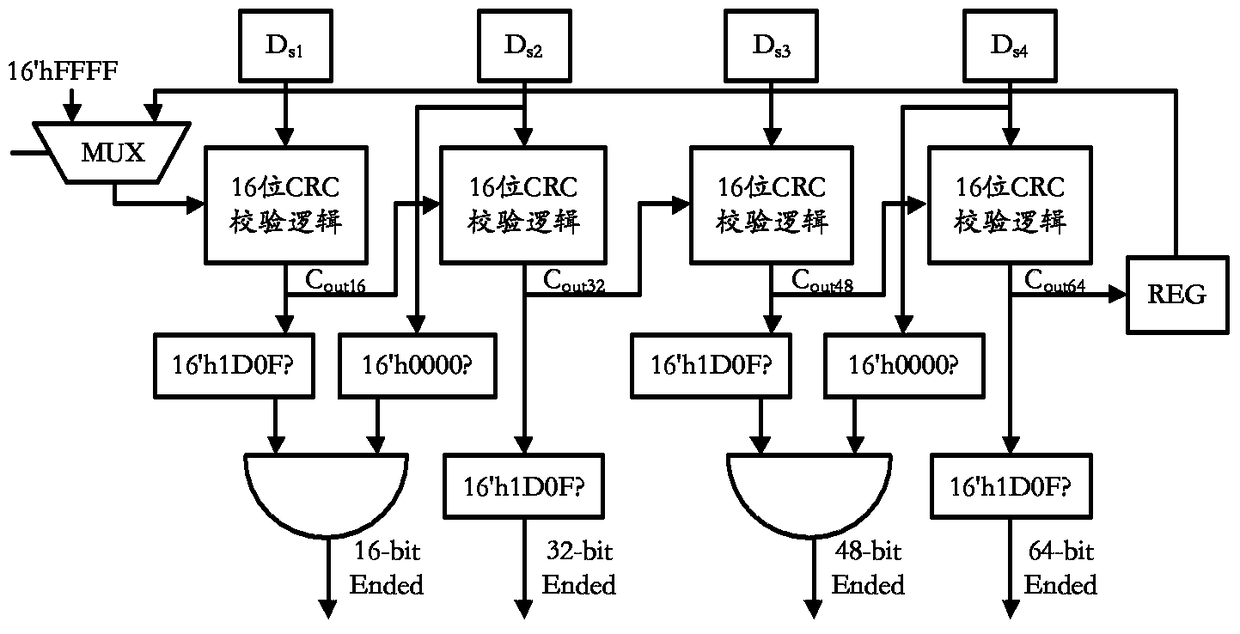

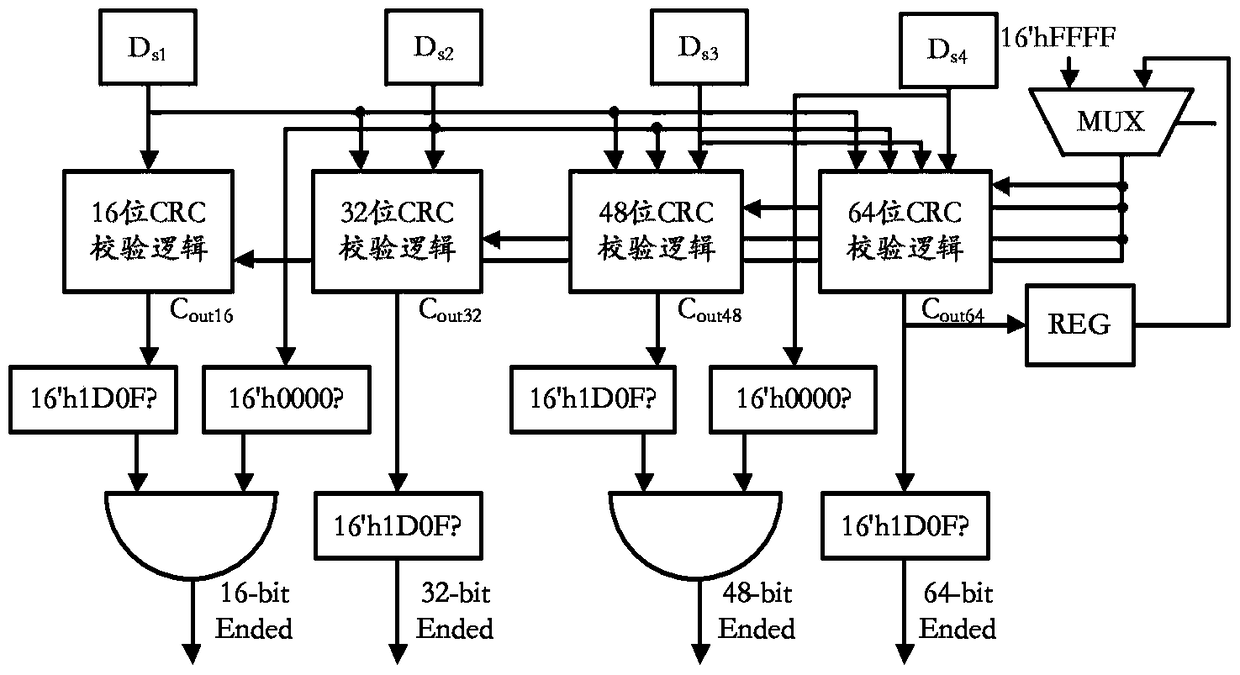

[0026] The basic ideas of the present invention are: ① reduce the number of parallel CRC-16 generators to achieve the purpose of reducing combinational logic and saving resources; ② increase the working speed of the circuit and improve performance through 64-bit parallel CRC-16. Since there are four transaction packet alignment formats of 64-bit bus width: 16-bit, 32-bit, 48-bit and 64-bit, four judgment logics are required to satisfy these four conditions. On the basis of the parallel structure, the 32-bit parallel CRC-16 is replaced by the 16-bit parallel CRC-16 and the equivalent judgment logic of bitwise inversion, so as to realize the verification that the transaction packet is a 32-bit alignment format; through 64 4...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More