FPGA-based device and method for loading and upgrading object codes

A technology of object code and SPI interface, which is applied in the direction of program control device, program loading/starting, generation of response errors, etc., can solve system defects such as long FPGA loading time, low data transmission rate of single-line serial interface, and inability to upgrade FPGA again and other issues to achieve the effect of avoiding the limitation of device selection, optimizing the chip layout space, and optimizing the cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

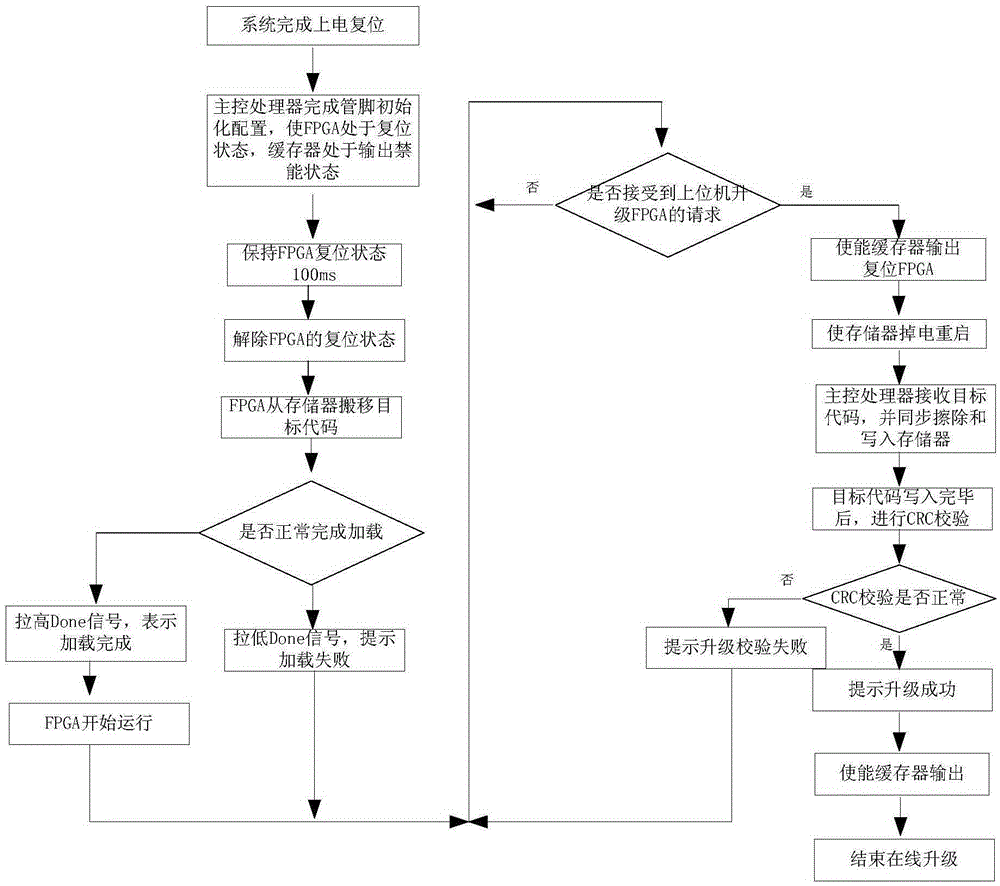

[0028] The present invention will be further described in detail below in conjunction with the embodiments and the accompanying drawings, but the embodiments of the present invention are not limited thereto.

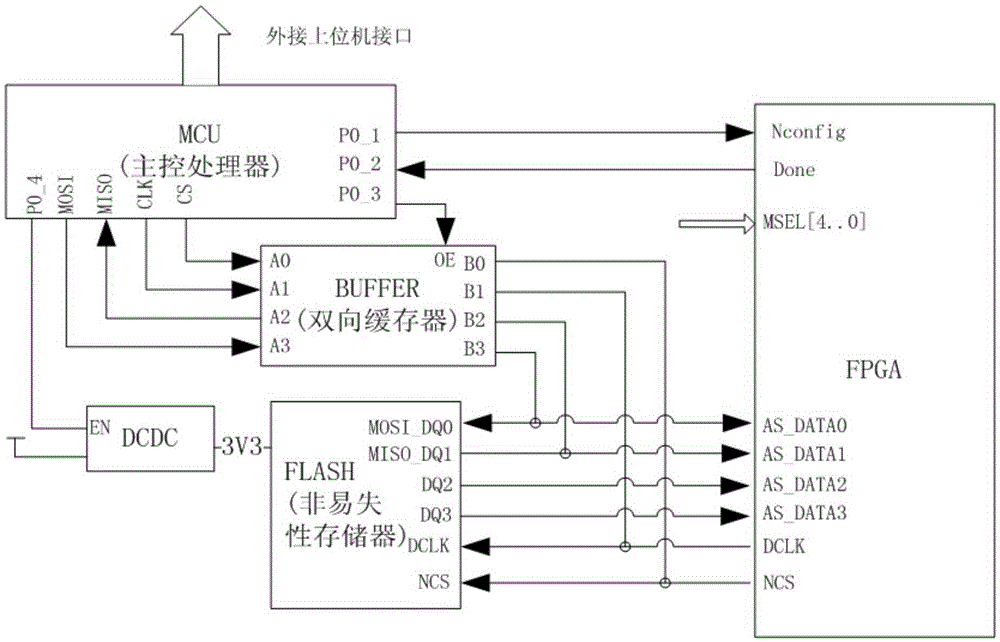

[0029] Such as figure 1 Said, a device for loading and upgrading target code of FPGA includes MCU (MicroControlUnit, micro control unit), FPGA, SPIFLASH (serial interface flash memory), and BUFFER (two-way buffer).

[0030] As the main control processor, the MCU is used to communicate with the host computer, receive instructions and FPGA object code data, write the object code into FLASH, and control the realization of the entire process.

[0031] As a non-volatile memory, FLASH is used to store the target code of the FPGA, and is connected to the loading dedicated pin of the FPGA through the SPI interface mode of four data lines, and connected to the MCU through the SPI interface mode of the single data line. The BUFFER acts as an isolation switch.

[0032] Such as ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More