A decoding circuit of a power instruction set vector coprocessor

A coprocessor and decoding circuit technology, applied in the field of decoding circuits, can solve the problems of waste of resources and power consumption, and achieve the effects of reducing hardware overhead, simple judgment logic, and improving stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

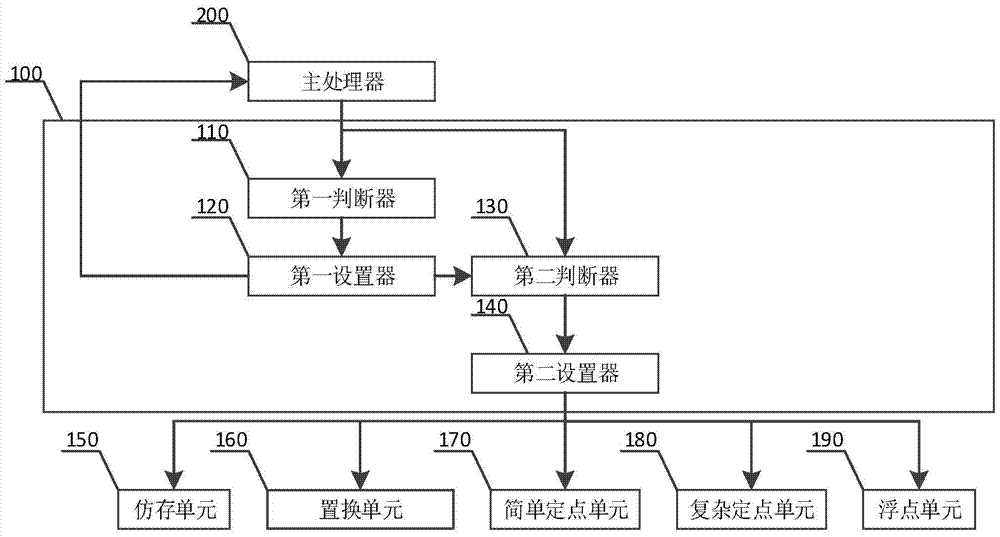

[0025] A decoding circuit of a POWER instruction set vector coprocessor of the present invention will be described in detail below in conjunction with the embodiments and accompanying drawings.

[0026] like figure 1 As shown, a decoding circuit of a POWER instruction set vector coprocessor of the present invention includes a first determiner 110, a first setter 120, a second determiner 130 and a second setter 140 connected in sequence, wherein ,

[0027] The input end of the first judger 110 is connected to the output end of the main processor 200, and is used to receive instructions from the main processor 200, and judge whether the instruction is an effective vector coprocessor instruction, and send the judgment result to the first setter 120;

[0028] The output of the first setter 120 is also connected to the input end of the main processor 200, and is used to feed back to the main processor 200 whether the instruction sent by the main processor 200 is a valid vector co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More