A half-selective interference cancellation structure for sram based on hierarchical bit line structure

A technology of hierarchical bit line and interference elimination, applied in information storage, static memory, digital memory information, etc., can solve the problems affecting the power consumption and robustness of SRAM circuits, and achieve non-ideal effects, eliminate short-circuit discharge paths, reduce Effects of interference and robustness improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

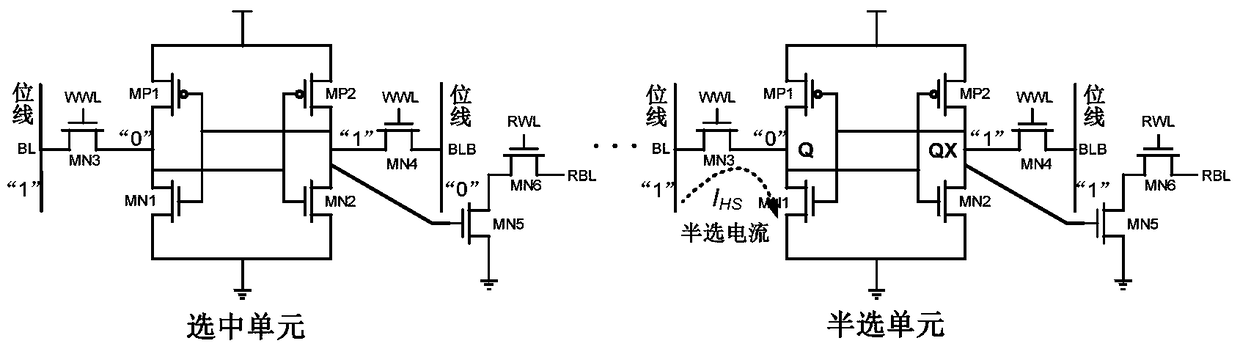

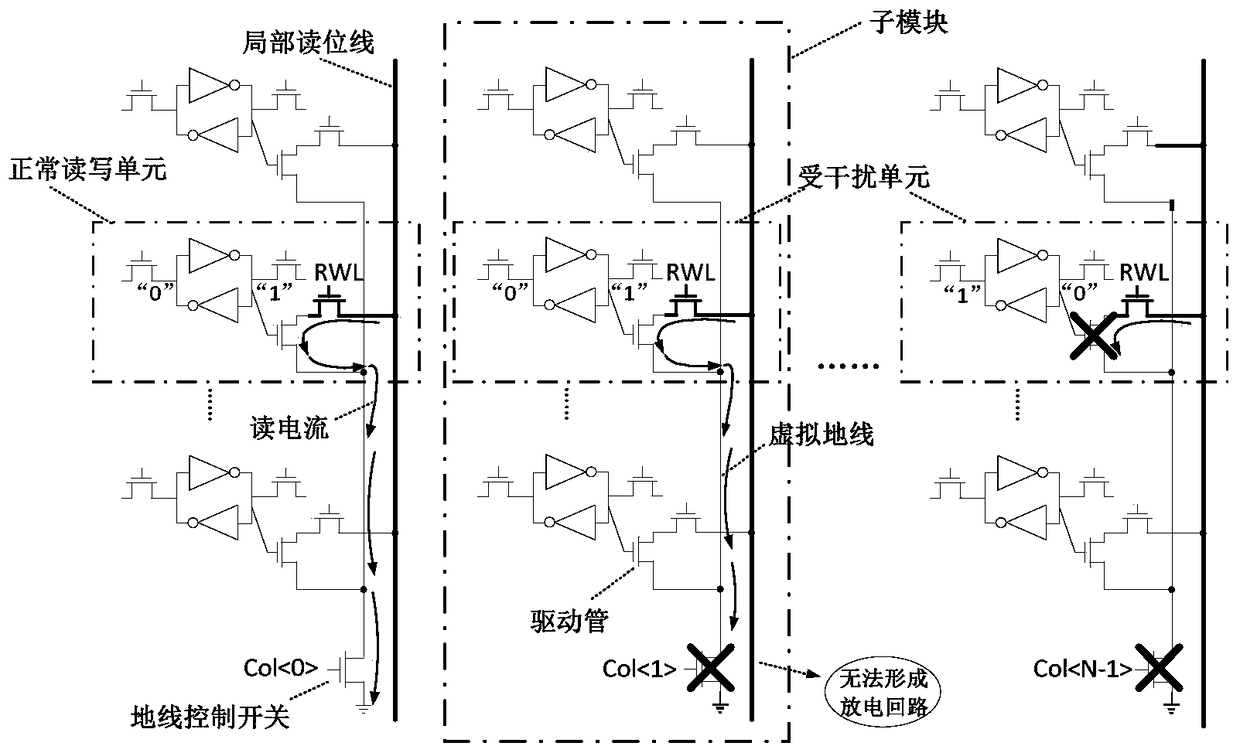

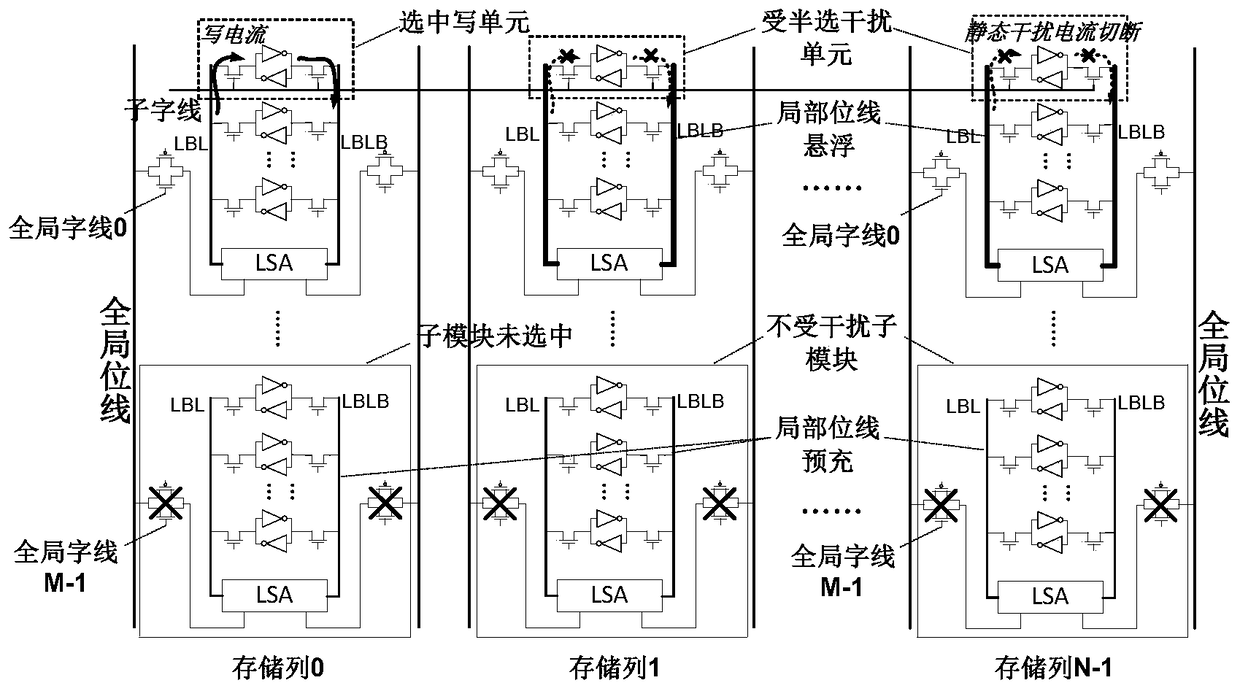

[0029] A kind of SRAM semi-selective elimination structure based on the hierarchical bit line structure of the present invention adopts the combination of local bit line suspension and virtual ground wire control technology; the present invention adopts 8T-SRAM unit, and according to the size of the SRAM array scale, each row of units Reasonable division into several sub-modules (each sub-module includes 8-64 memory cells) to reduce the parasitic capacitance of the bit line, thereby reducing the power consumption during read and write operations. The semi-selection interference phenomenon comes from the existence of the static discharge path of the pre-charged bit line-access transistor-pull-down transistor. For read operations, such as figure 2 As shown, the ground wires of the reading branches of each memory unit in the sub-module are separately led out, and connected to the actual ground wire through the ground wire control switch, and the column selection signal Col of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More