Patents

Literature

32results about How to "Eliminate Static Power Consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

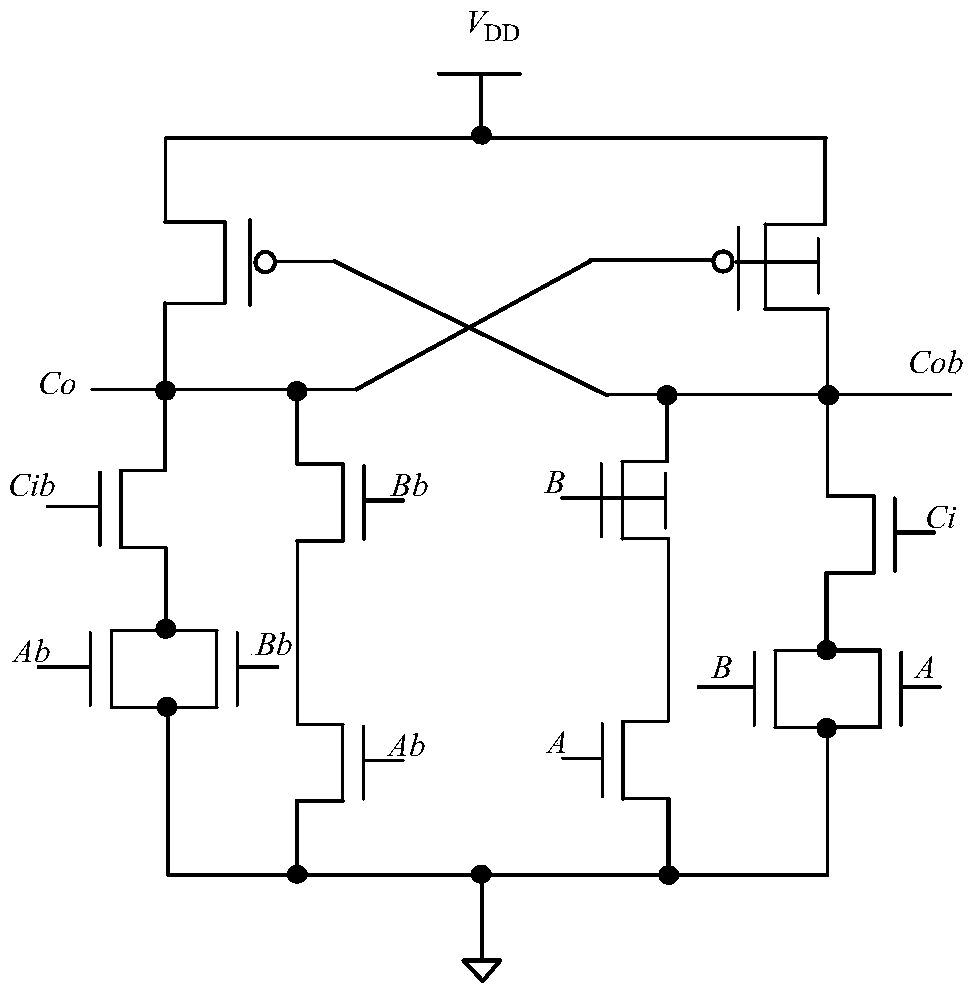

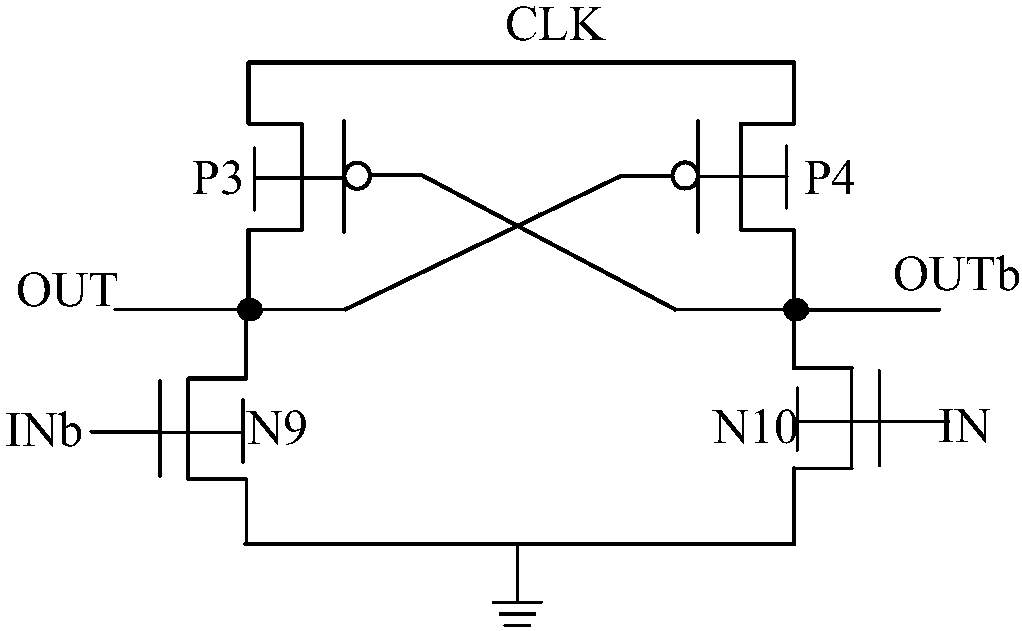

Low-dynamic maladjusted high-speed low-power consumption comparator circuit

InactiveCN108832916AImprove stabilityReduce complexityMultiple input and output pulse circuitsDifferential signalingComparators circuits

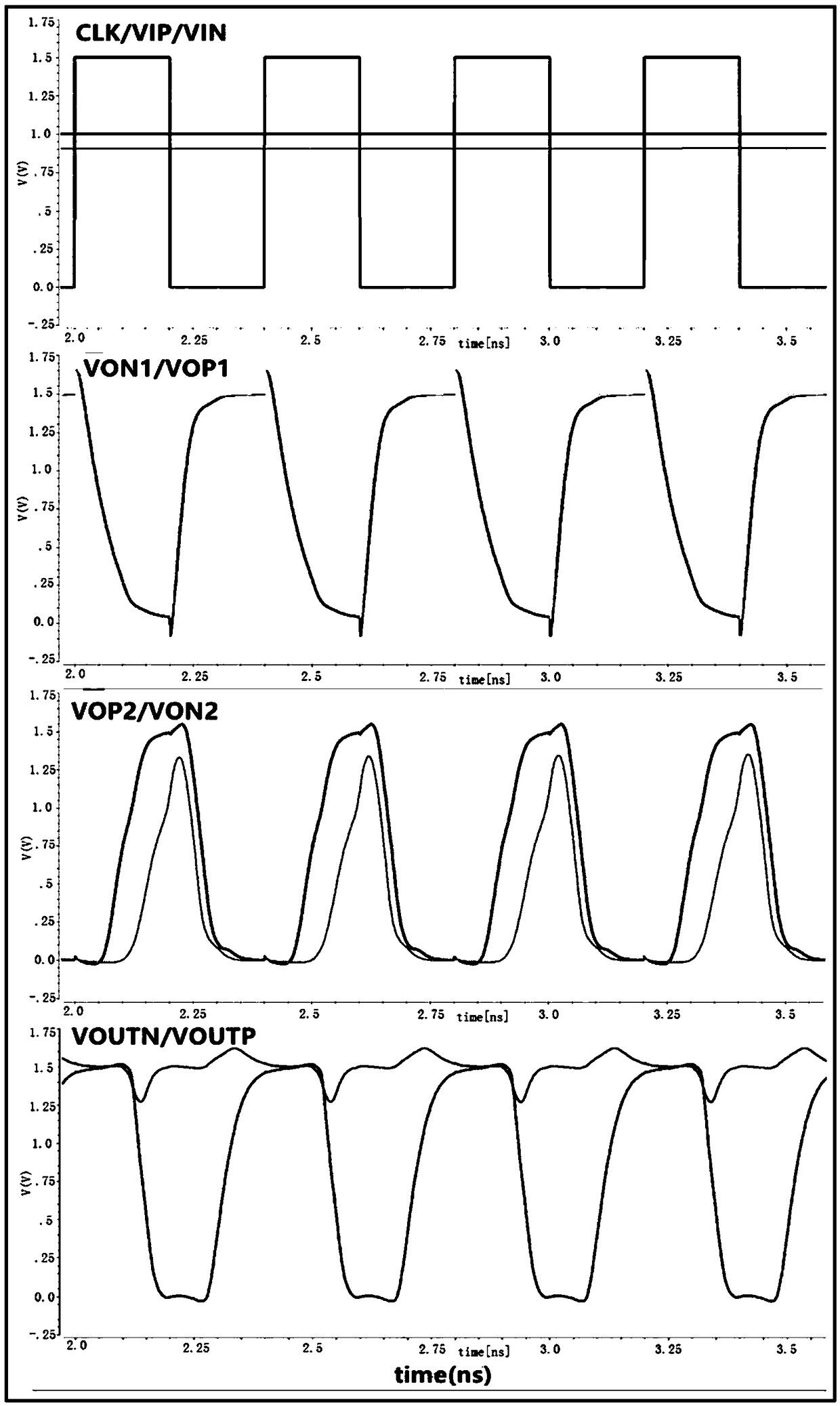

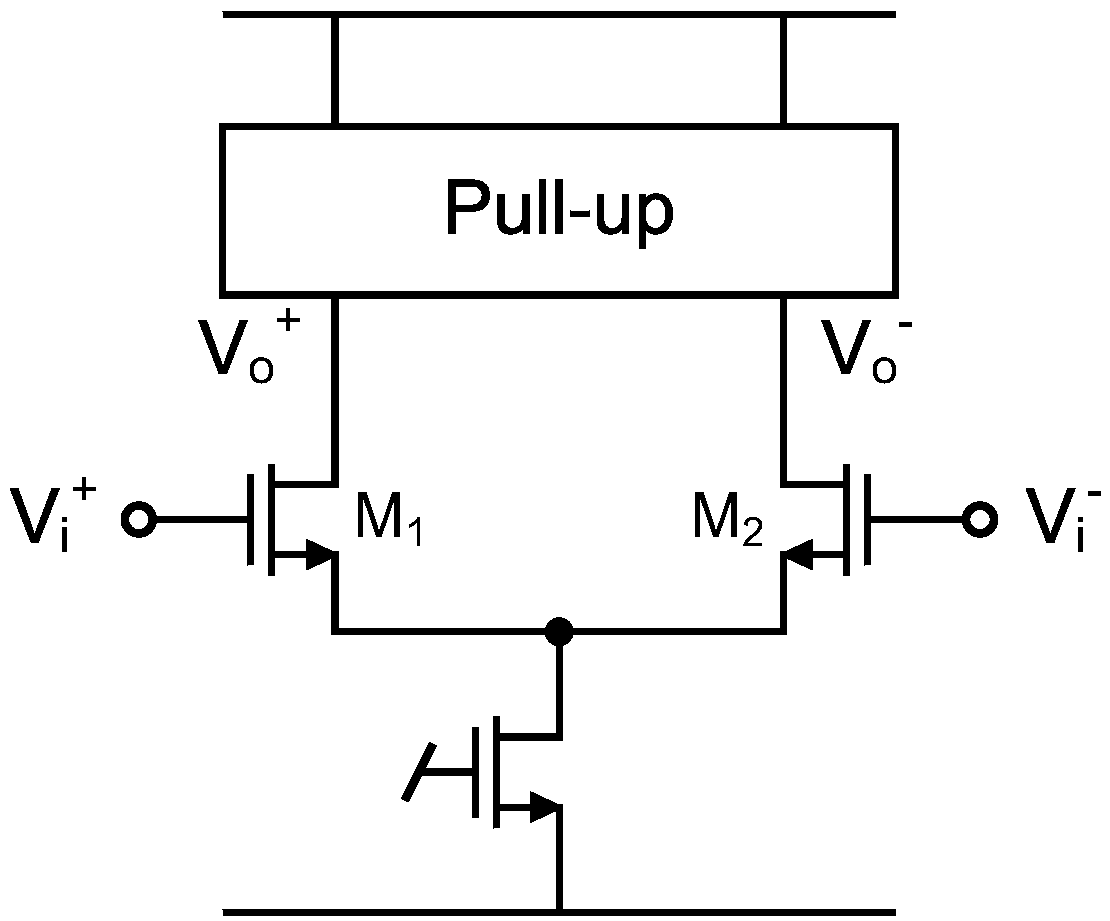

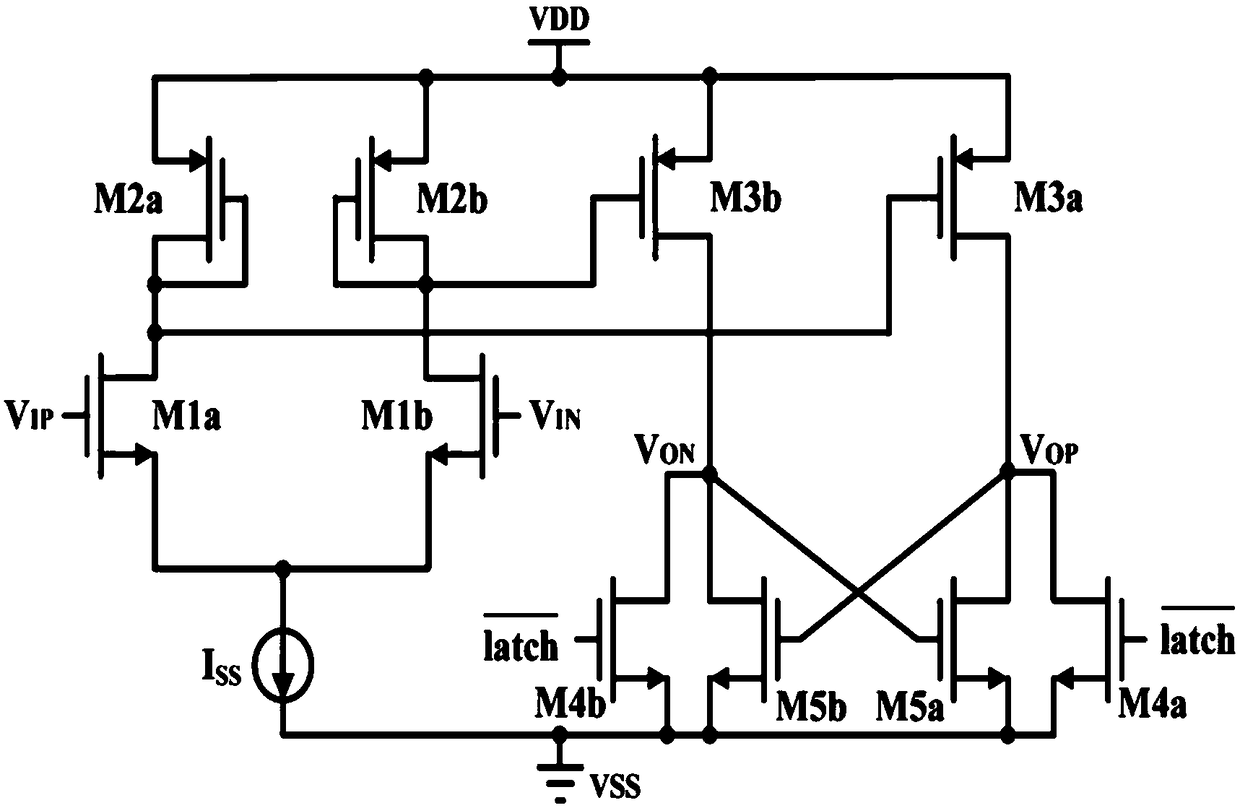

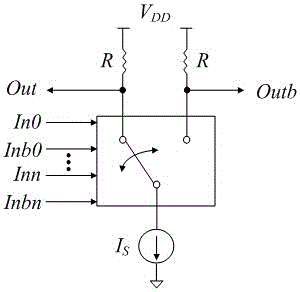

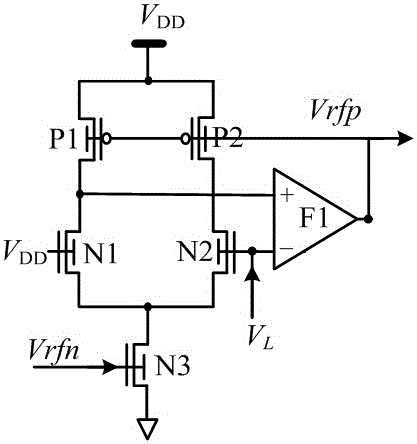

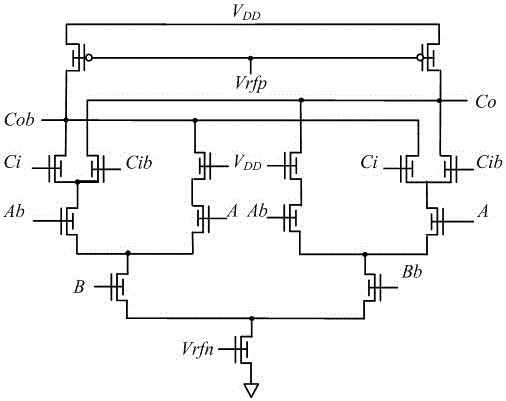

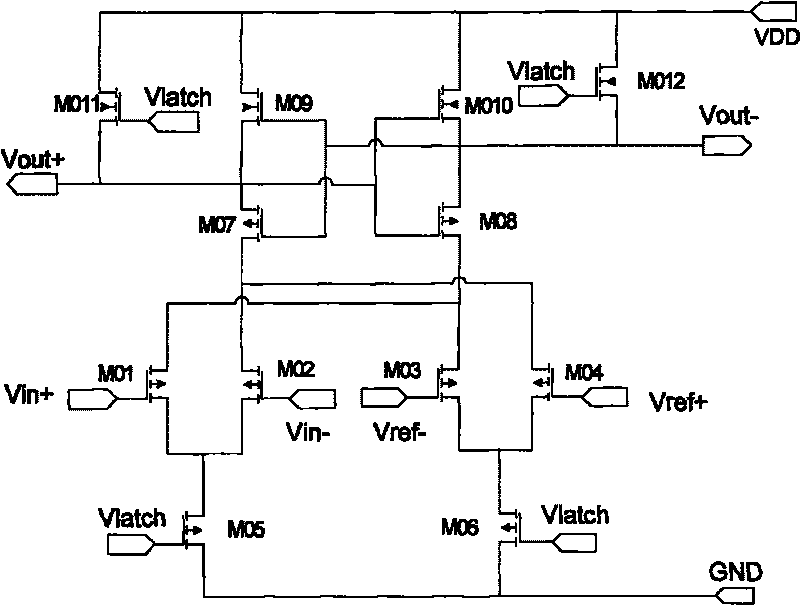

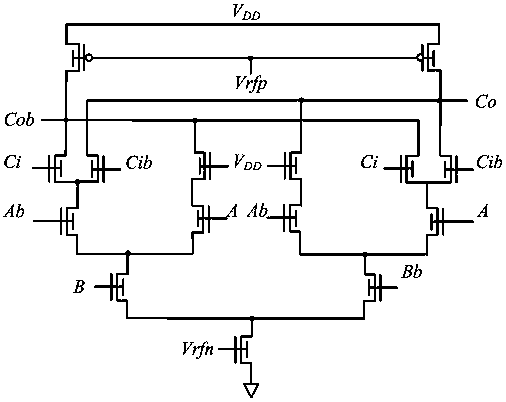

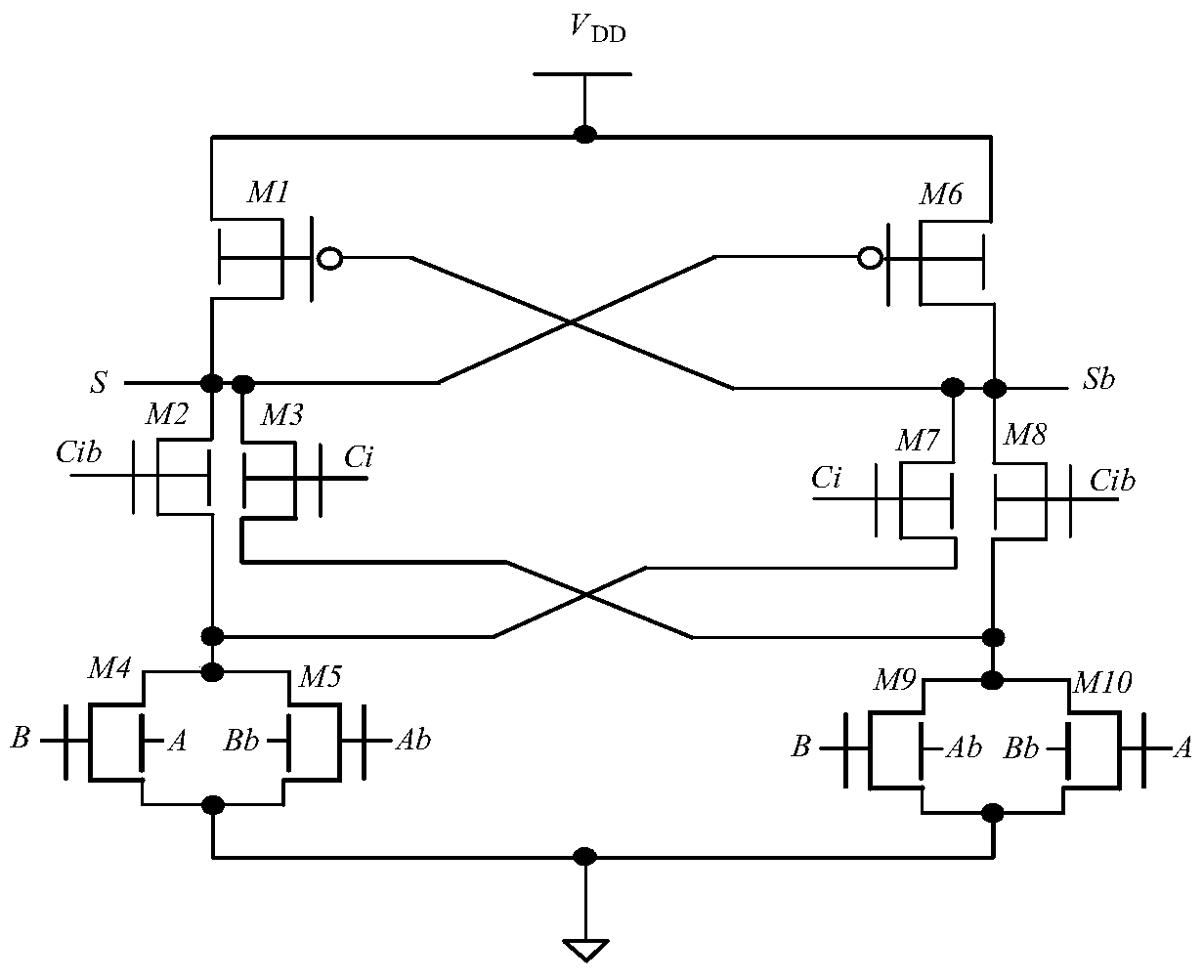

The invention discloses a low-dynamic maladjusted high-speed low-power consumption comparator circuit. The circuit comprises a first-stage pre-amplifying circuit and a second-stage positive-feedback latch circuit; the comparator circuit controls a comparison stage and a reset stage of the comparator circuit by adopting a clock signal; the comparator circuit is located at the comparison stage whenthe clock signal is located at high level, a pair of differential input signals are respectively amplified through the first-stage pre-amplifying circuit so as to form a pair of primary differential signals; the second-stage feedback latch circuit inversely amplifies a pair of primary differential signals and forms a pair of secondary differential signals, and performs the positive feedback latching on the secondary differential signals so as to obtain a pair of differential output signals. By adopting a tail current source biased by a bias voltage and a cascade switch tube controlled by the clock signal, the static power consumption is eliminated, the stability on the tube over-driving voltage by the differential input is guaranteed, and the dynamic maladjustment is effectively reduced.

Owner:ANHUI CHUANSI MICROELECTRONICS CO LTD +1

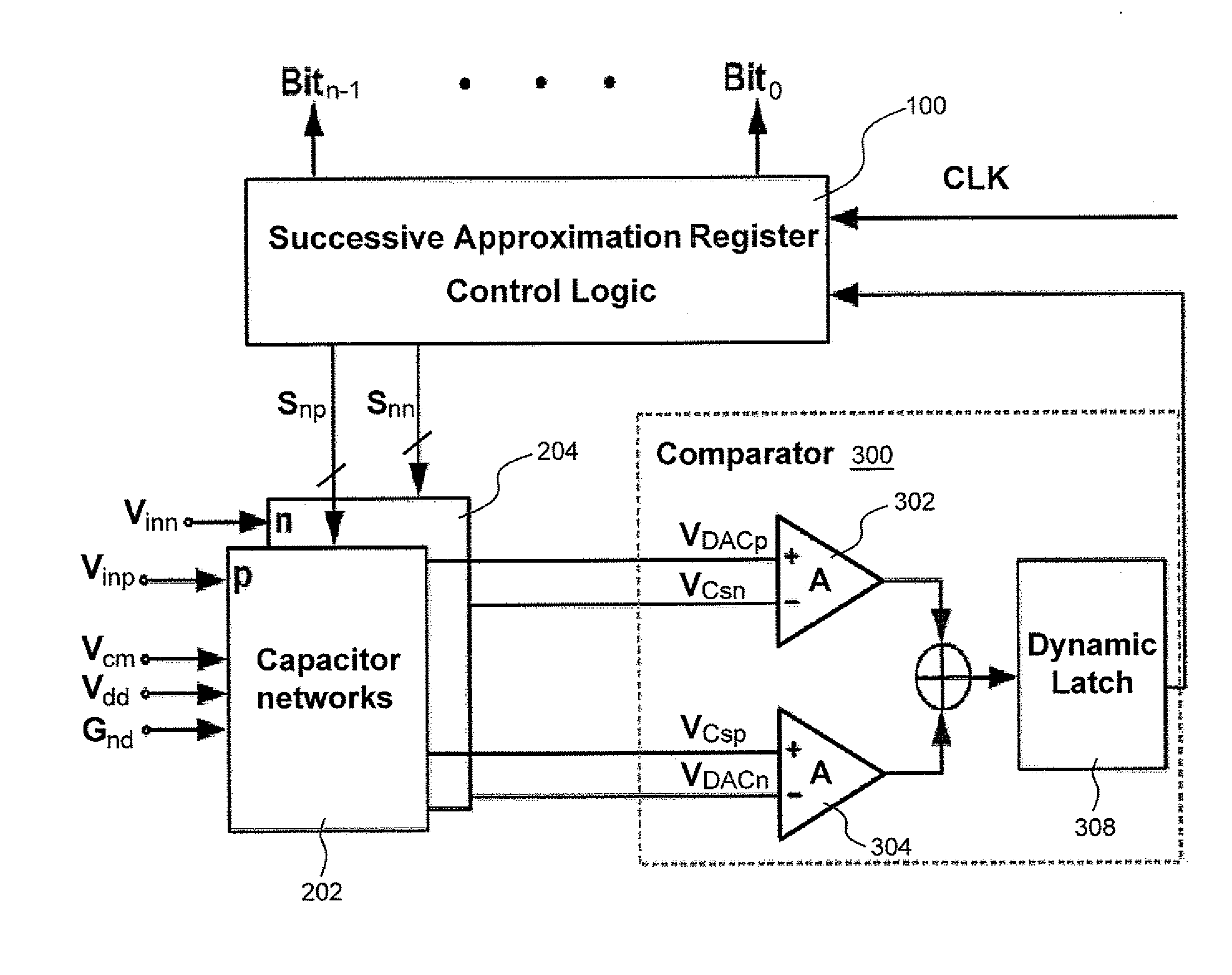

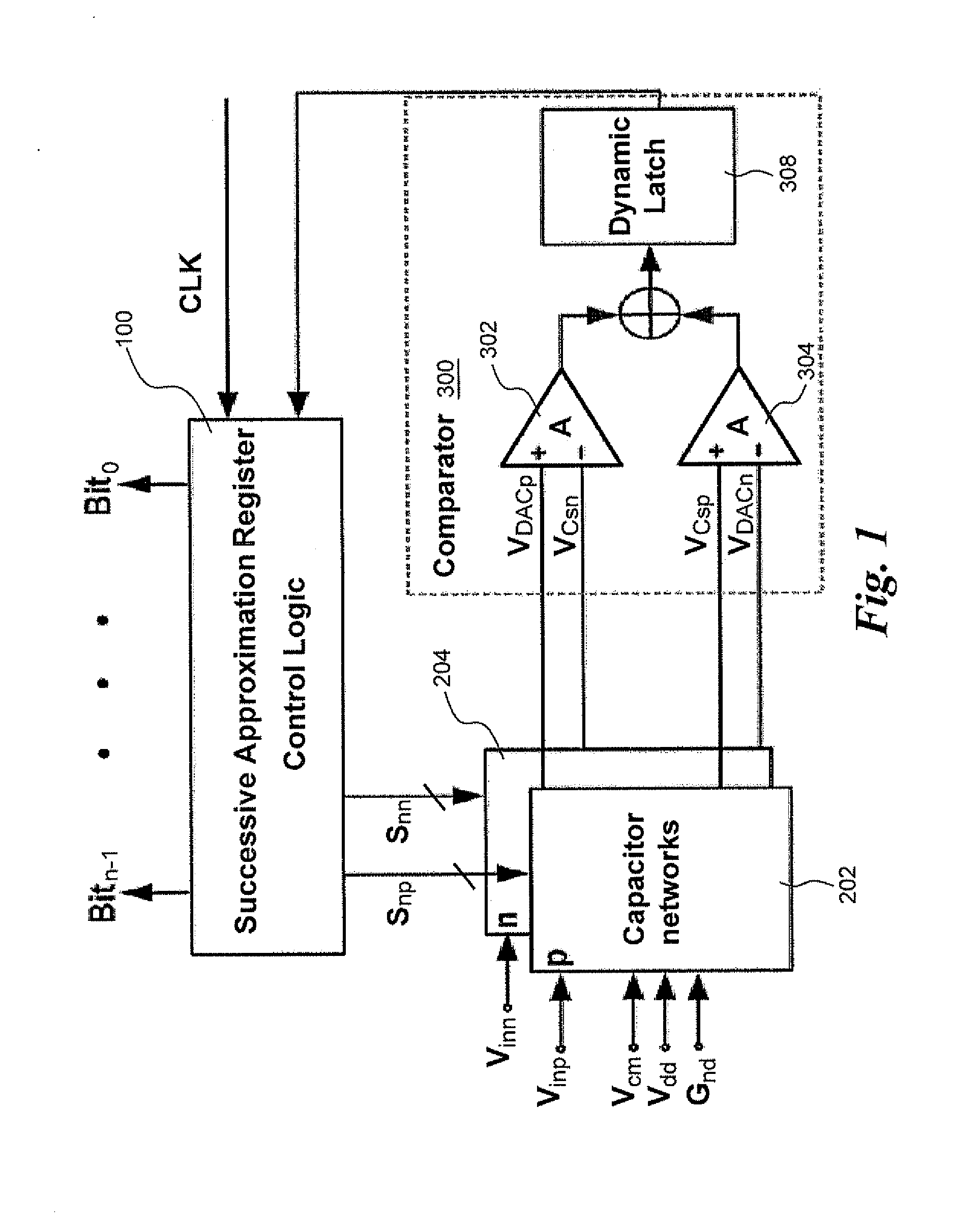

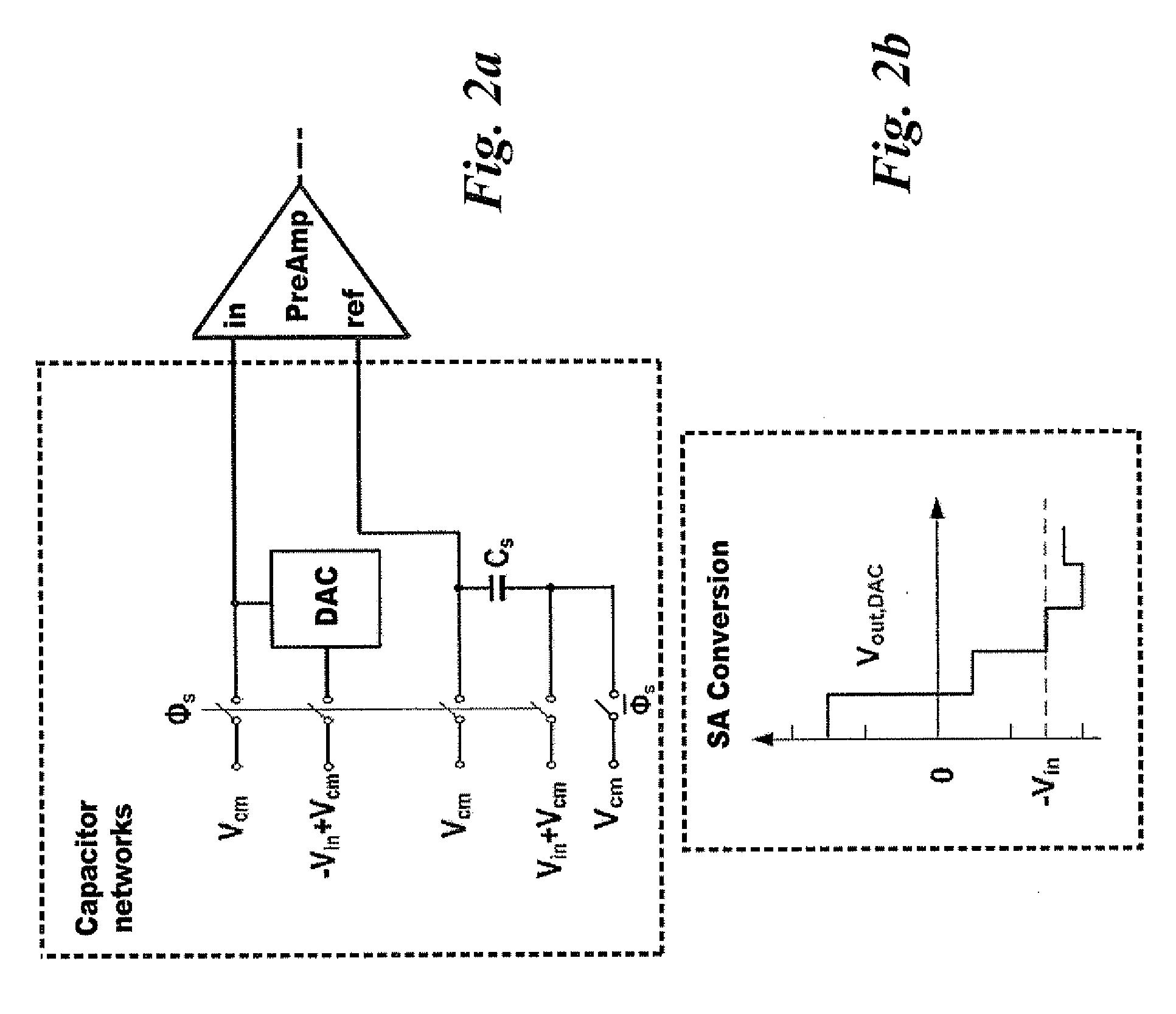

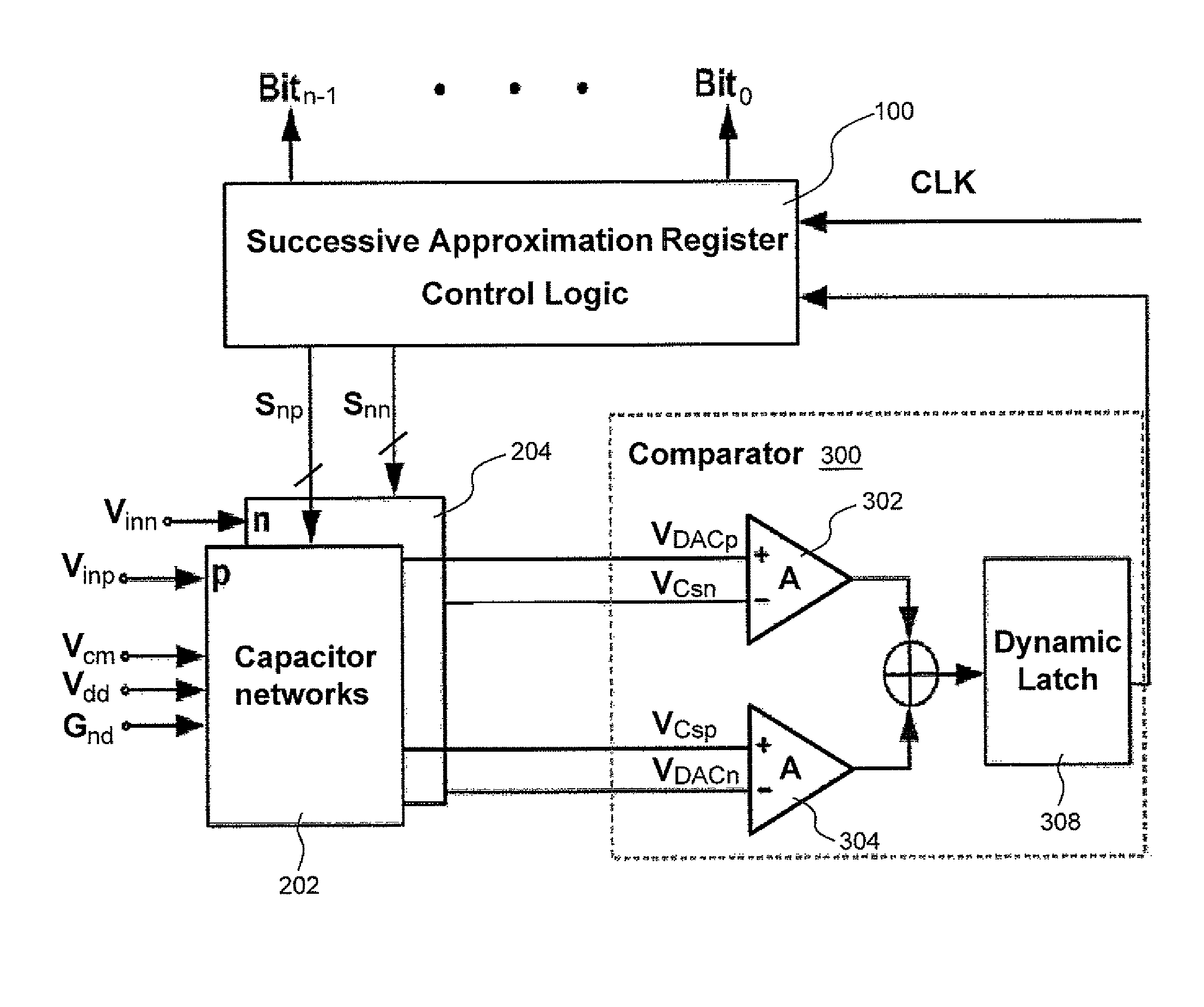

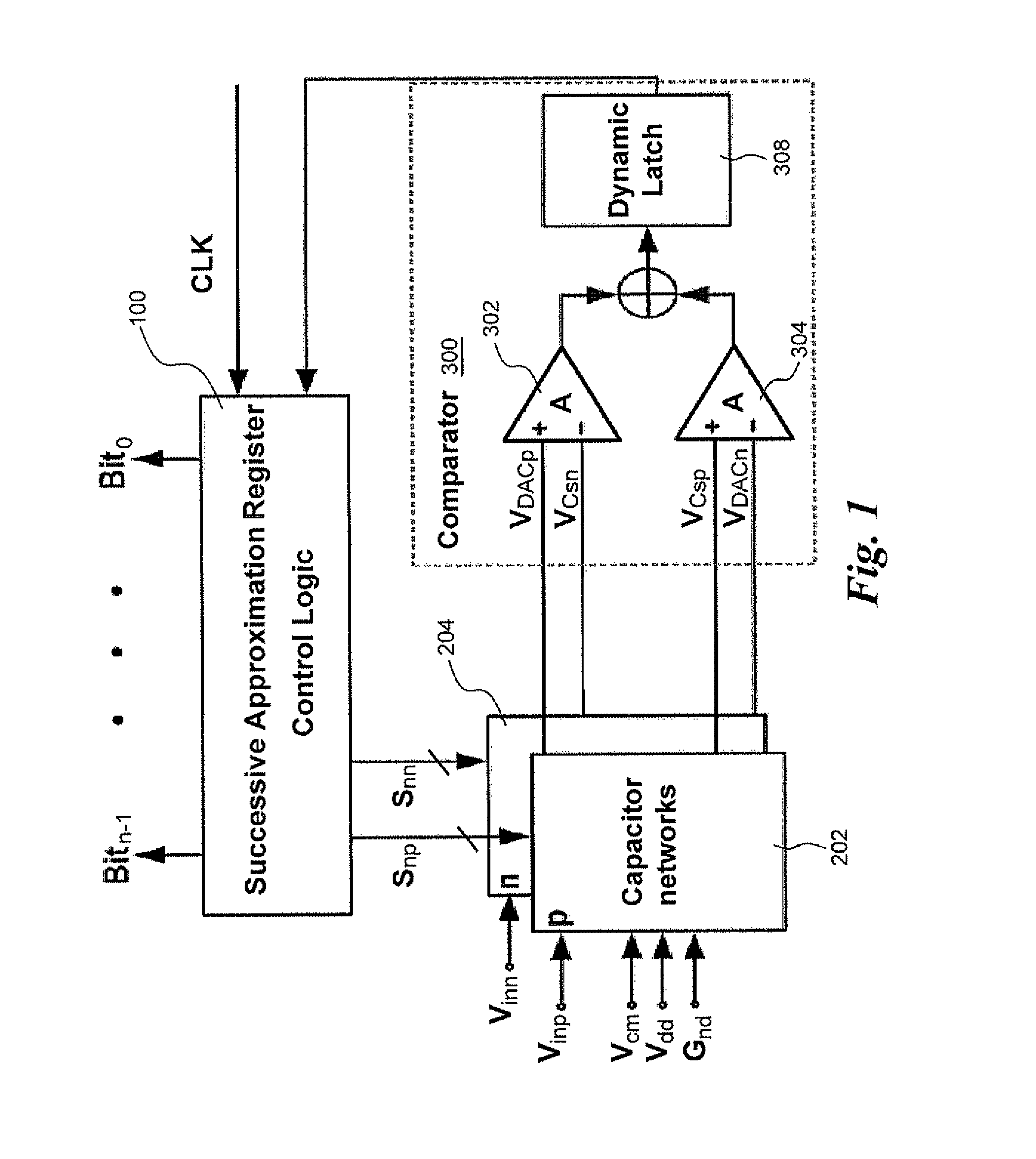

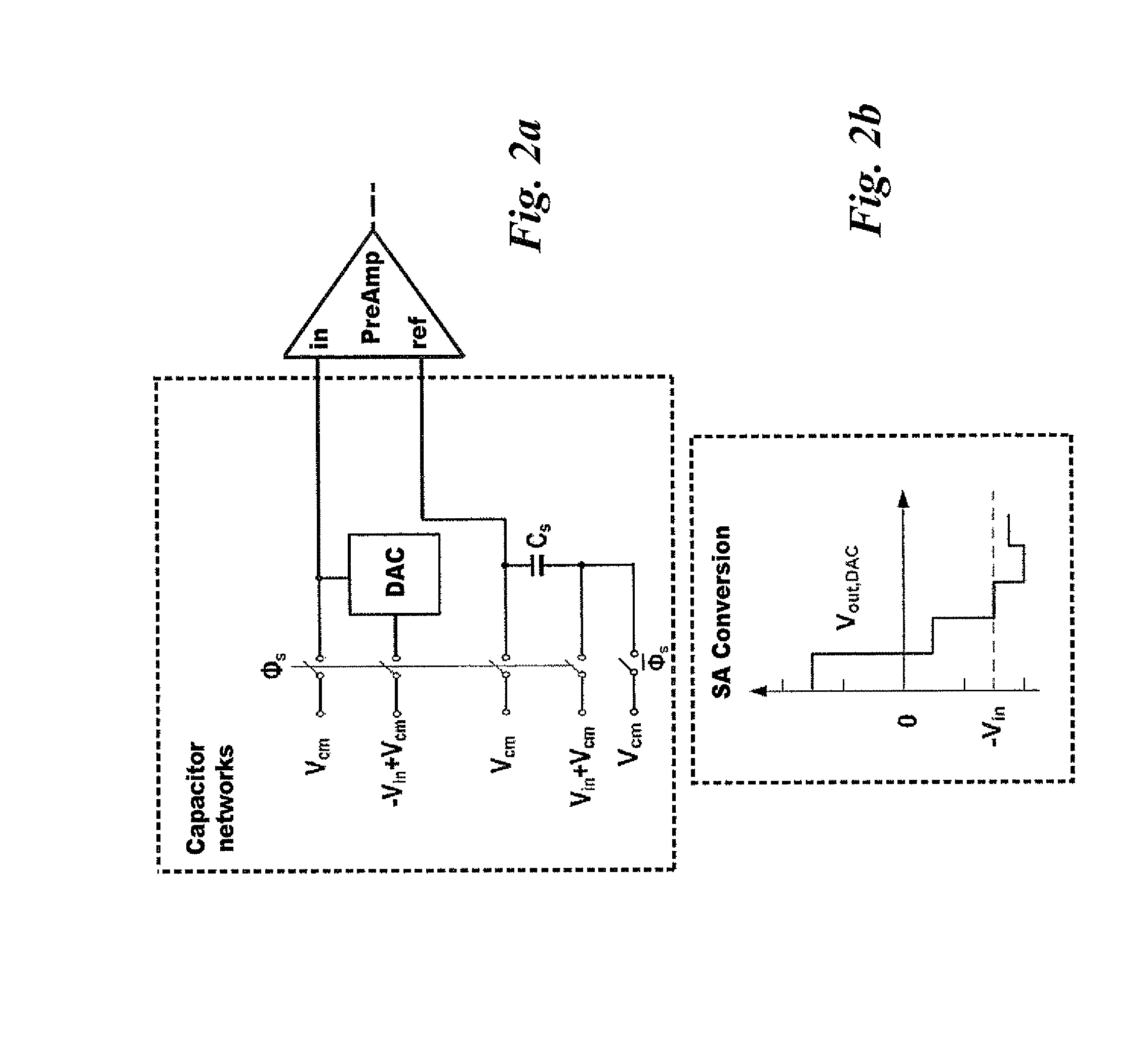

N-bits successive approximation register analog-to-digital converting circuit

ActiveUS20120306679A1Remove static power dissipationEliminate Static Power ConsumptionPower saving provisionsElectric signal transmission systemsAnalog to digital conversionCapacitance

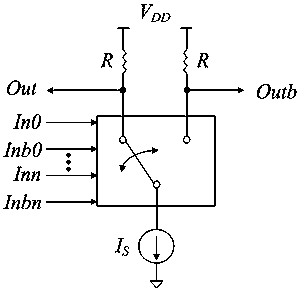

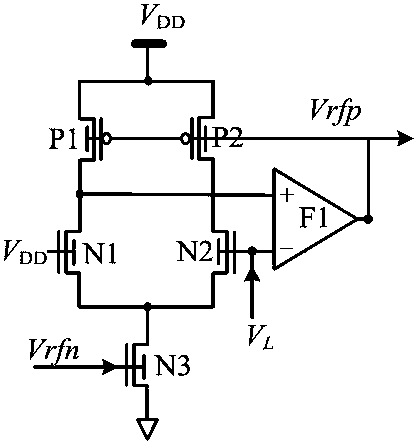

The present invention provides an n-bits successive approximation register (SAR) analog-to-digital converting (ADC) circuit, comprising: an n-bits SAR control logic, a p-type capacitor network including a DACp array and a sampling capacitor CSp, an n-type capacitor network including a DACn array and a sampling capacitor CSn; and a comparator for comparing outputs from the p-type capacitor network and the n-type capacitor network, wherein a power supply and ground are directly connected to the p-type capacitor network and the n-type capacitor network without using reference voltages produced by a reference voltage generator. The n-bits SAR control logic comprises n shift registers, n bit registers, and a switching logic. The comparator comprises a first pre-amplifier, a second pre-amplifier and a dynamic latch. Alternative, the comparator comprises a four-input pre-amplifier and a dynamic latch.

Owner:UNIVERSITY OF MACAU

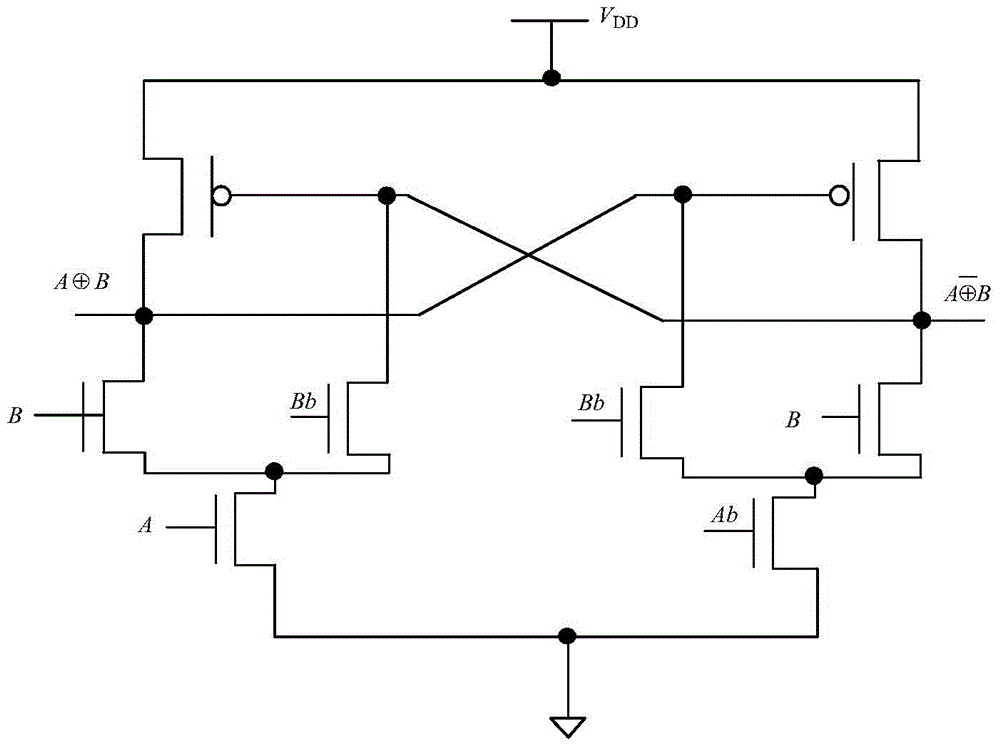

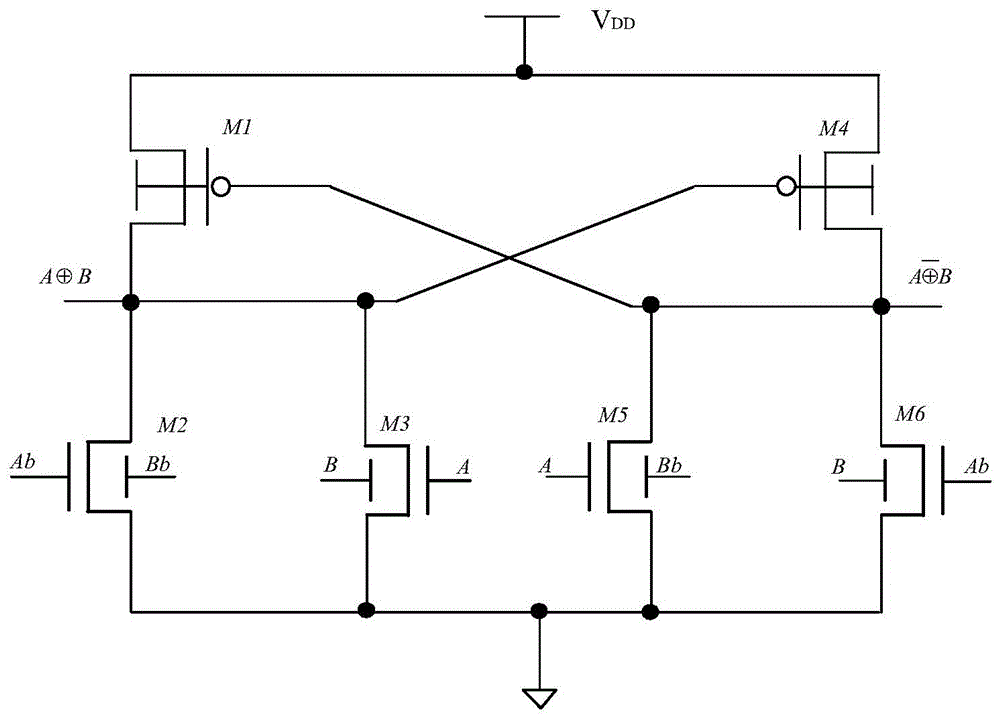

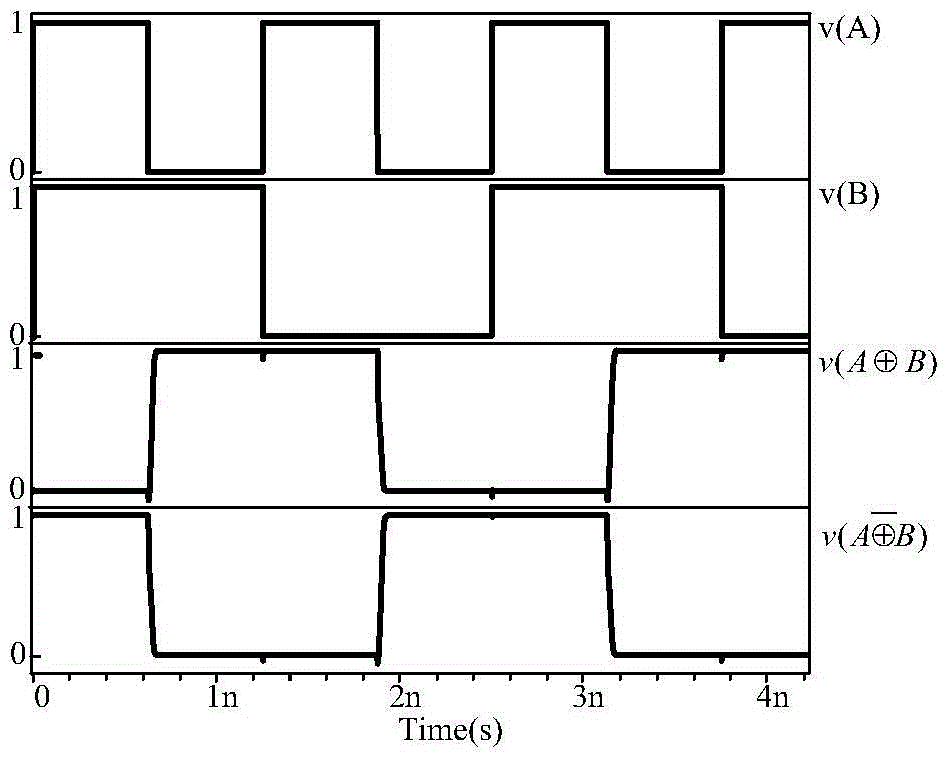

XOR/XNOR gate circuit based on FinFET devices

The invention discloses an XOR / XNOR gate circuit based on FinFET devices. The circuit comprises a first FinFET transistor, a second FinFET transistor, a third FinFET transistor, a fourth FinFET transistor, a fifth FinFET transistor, and a sixth FinFET transistor, the first FinFET transistor and the fourth FinFET transistor are both P-type FinFET transistors, the second FinFET transistor, the third FinFET transistor, the fifth FinFET transistor, and the sixth FinFET transistor are all N-type FinFET transistors, the first FinFET transistor and the fourth FinFET transistor are both low-threshold FinFET transistors, the second FinFET transistor, the third FinFET transistor, the fifth FinFET transistor, and the sixth FinFET transistor are all high-threshold FinFET transistors, the numbers of the fins of the first FinFET transistor and the fourth FinFET transistor are both 1, and the numbers of the fins of the second FinFET transistor, the third FinFET transistor, the fifth FinFET transistor, and the sixth FinFET transistor are all 2. The circuit is advantageous in that the logic function is correct, the circuit area is small, the time delay is short, the power consumption is low, and the consumption-delay product is small.

Owner:NINGBO UNIV

N-bits successive approximation register analog-to-digital converting circuit

ActiveUS8344931B2Eliminate Static Power ConsumptionPower saving provisionsElectric signal transmission systemsCapacitanceShift register

The present invention provides an n-bits successive approximation register (SAR) analog-to-digital converting (ADC) circuit, comprising: an n-bits SAR control logic, a p-type capacitor network including a DACp array and a sampling capacitor CSp, an n-type capacitor network including a DACn array and a sampling capacitor CSn; and a comparator for comparing outputs from the p-type capacitor network and the n-type capacitor network, wherein a power supply and ground are directly connected to the p-type capacitor network and the n-type capacitor network without using reference voltages produced by a reference voltage generator. The n-bits SAR control logic comprises n shift registers, n bit registers, and a switching logic. The comparator comprises a first pre-amplifier, a second pre-amplifier and a dynamic latch. Alternative, the comparator comprises a four-input pre-amplifier and a dynamic latch.

Owner:UNIVERSITY OF MACAU

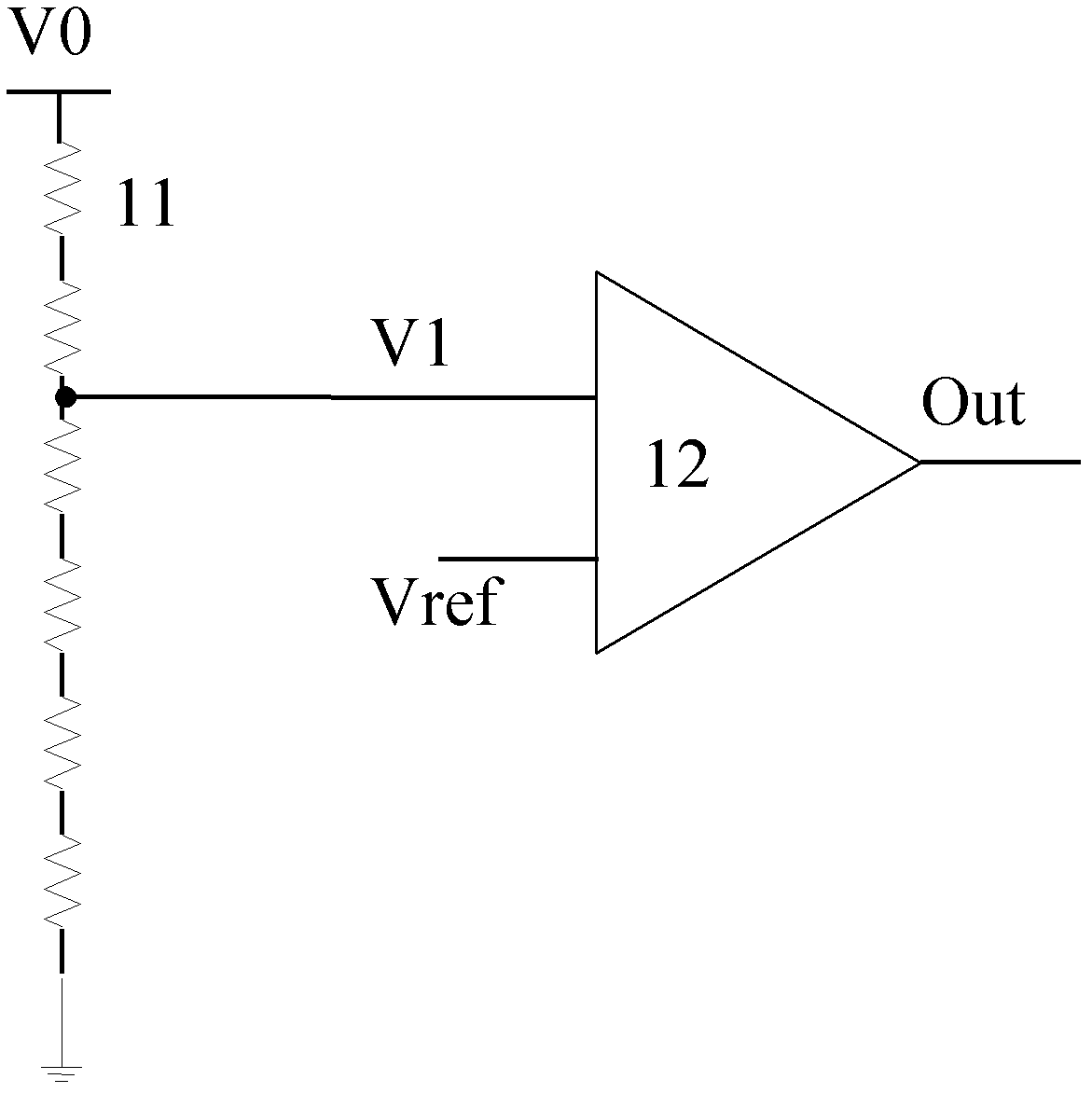

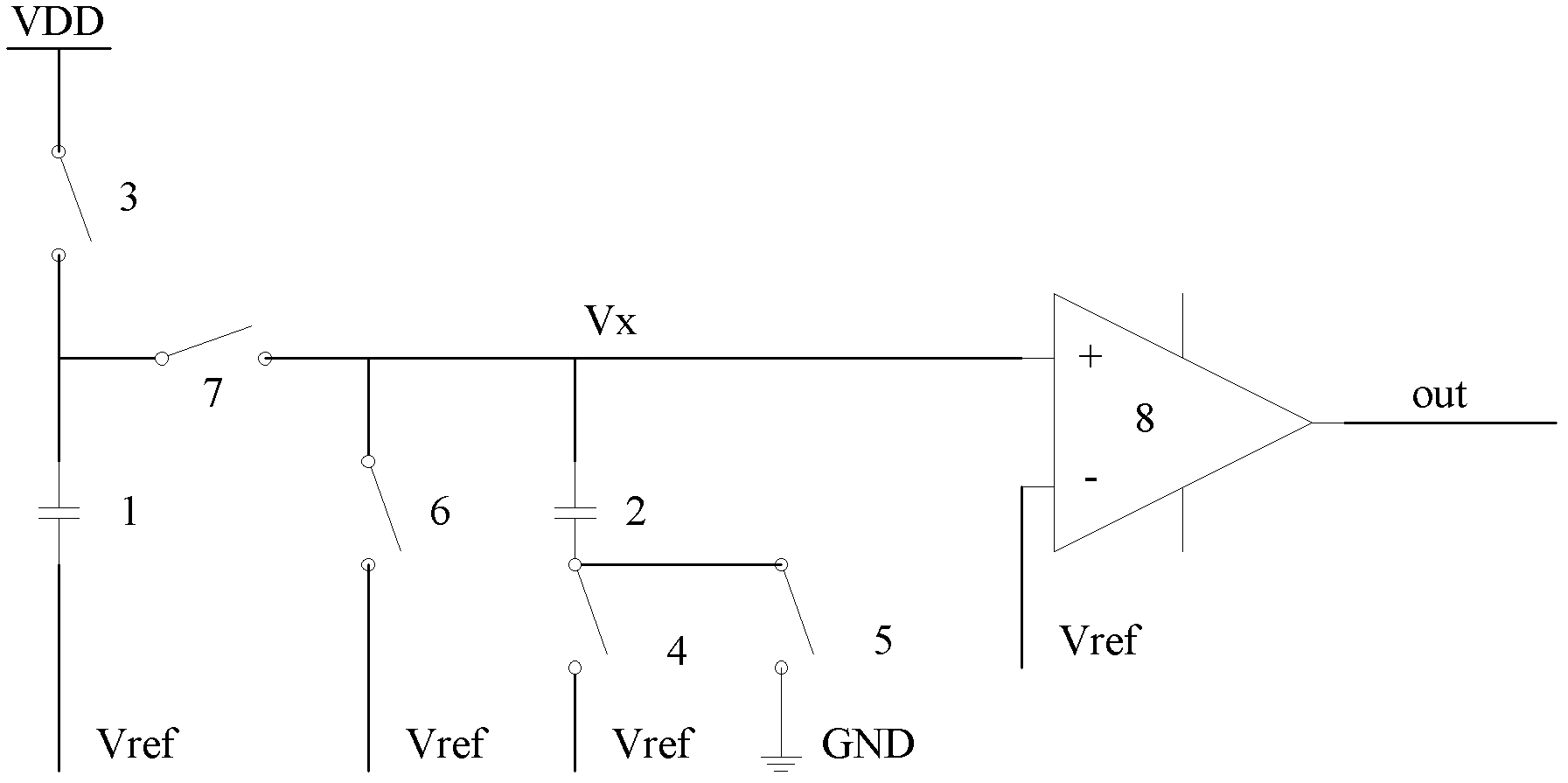

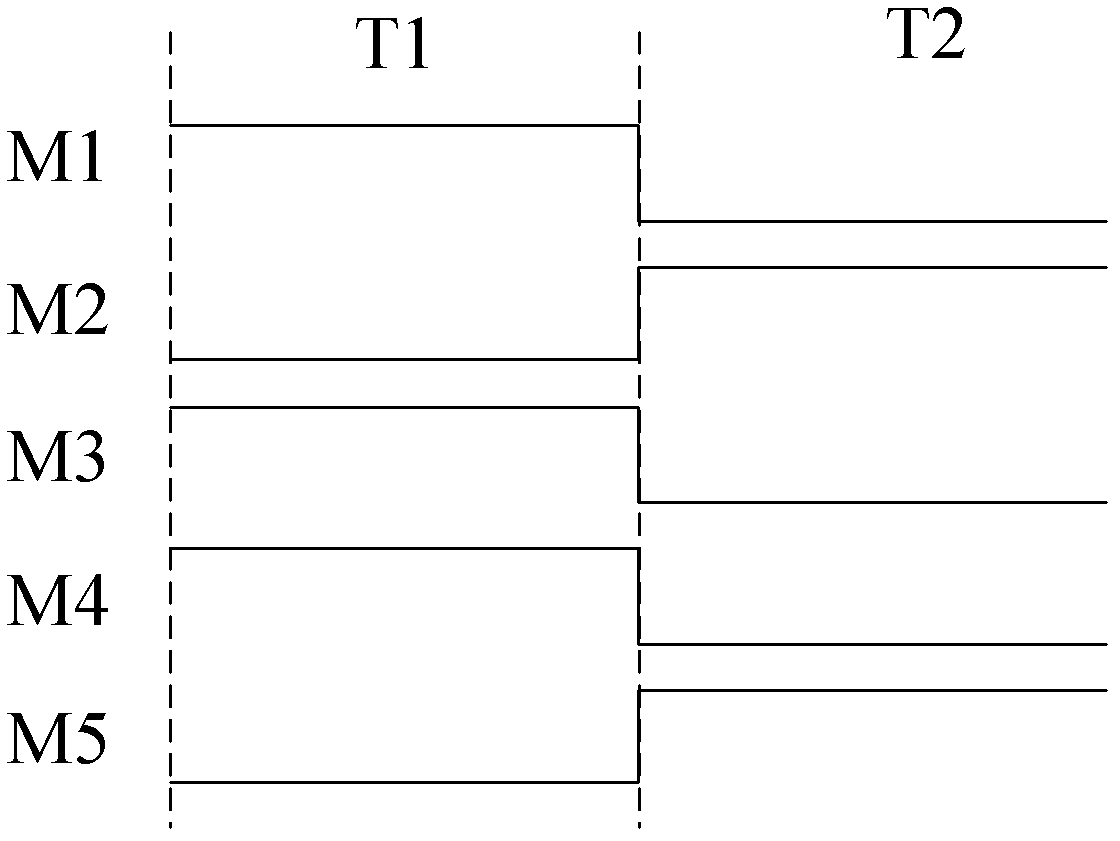

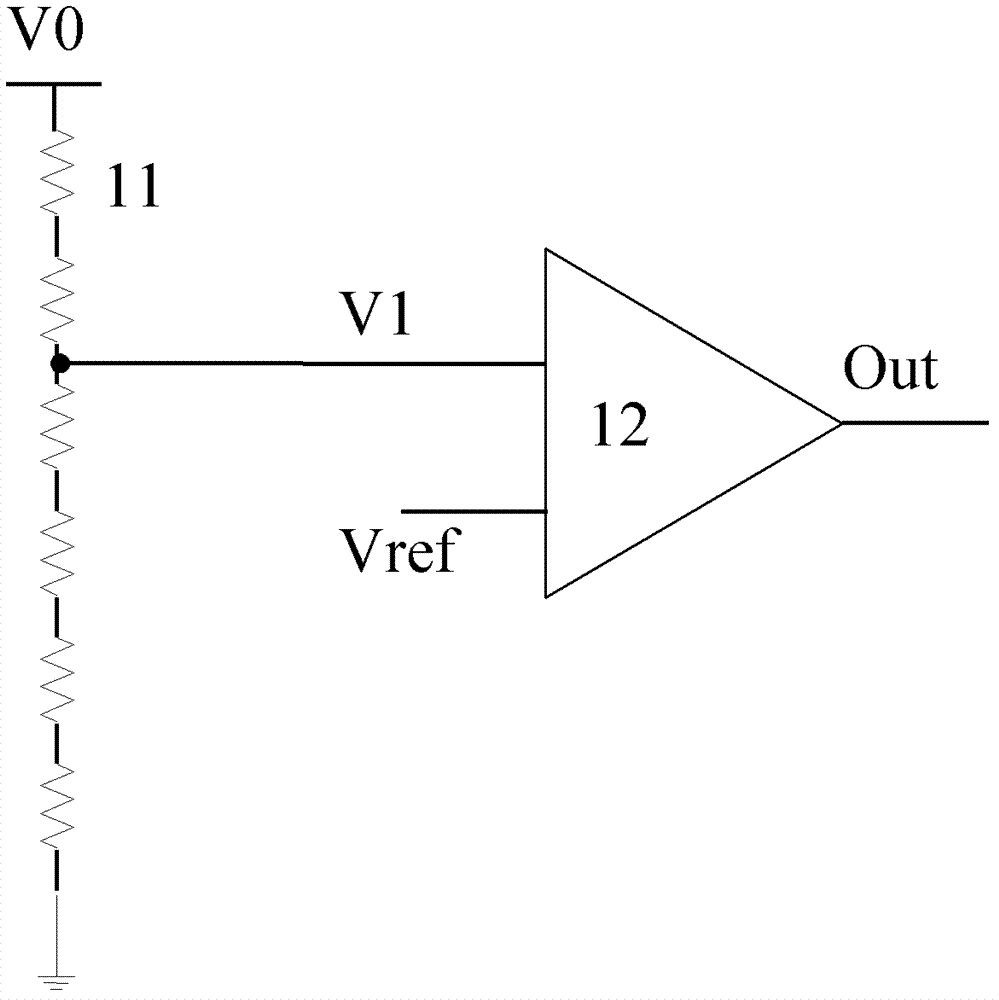

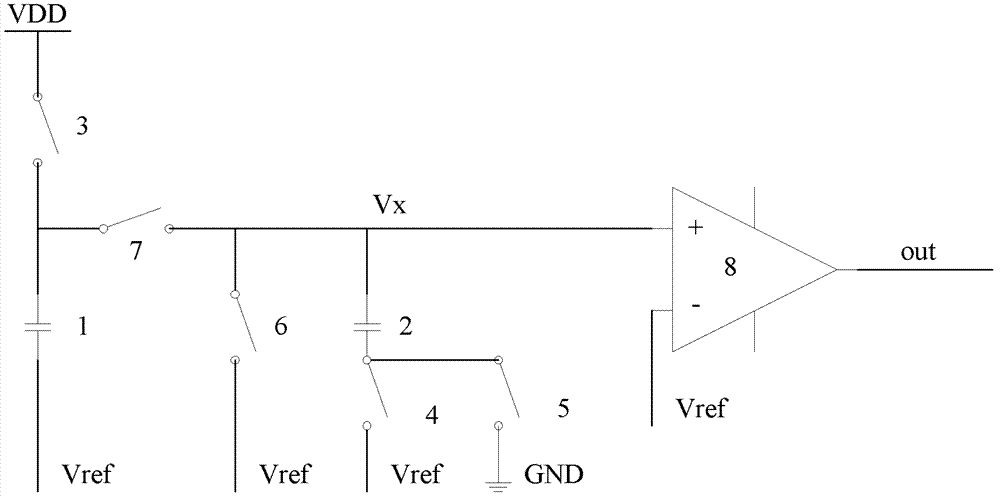

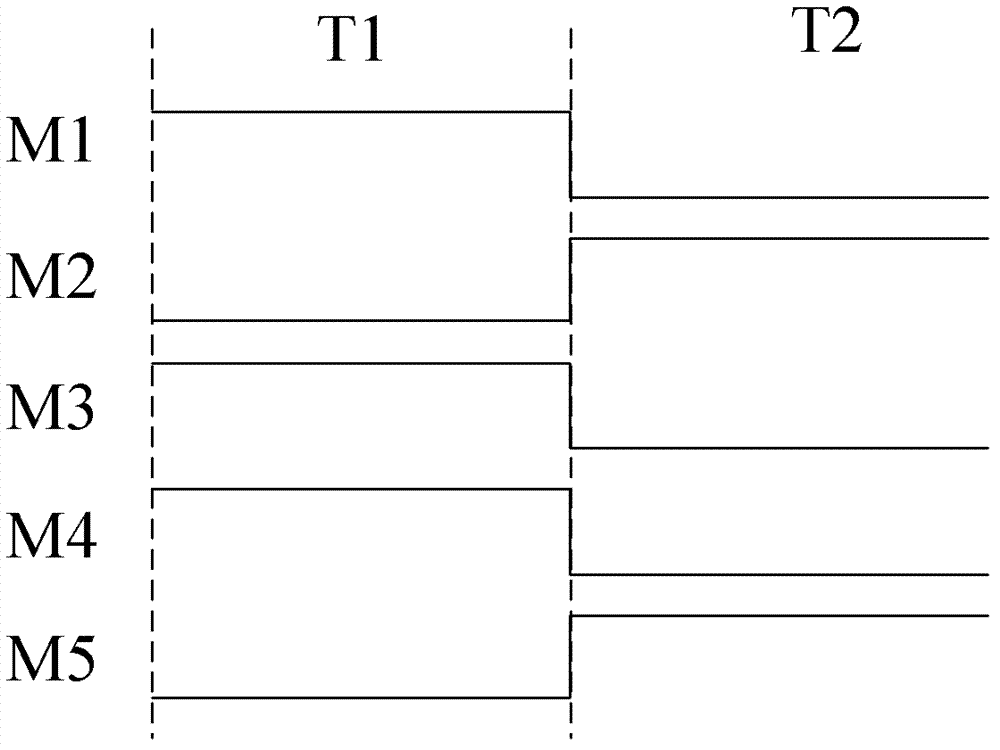

Voltage detection circuit

ActiveCN103176020ASmall footprintHighly integratedCurrent/voltage measurementVoltage dividersCapacitanceVoltage reference

The invention discloses a voltage detection circuit which comprises a voltage divider circuit and a comparator. The voltage divider circuit includes a first capacitor and a second capacitor. A first end of the first capacitor is connected with a reference voltage, and a second end of the first capacitor is connected with a supply voltage through a first switch. A first end of the second capacitor is connected with the reference voltage through a second switch and connected with a ground potential through a third switch, and a second end of the second capacitor is the output end of the voltage divider circuit, connected with a first end of the comparator, and connected with the reference voltage through a forth switch. The second end of the first capacitor is connected with the second end of the second capacitor through a fifth switch. The voltage detection circuit can reduce the occupation space of the circuit on a chip, completely cancel the static power consumption of the circuit, thereby reducing the power consumption of the circuit, and guarantee that the high voltage dividing precision of the circuit.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

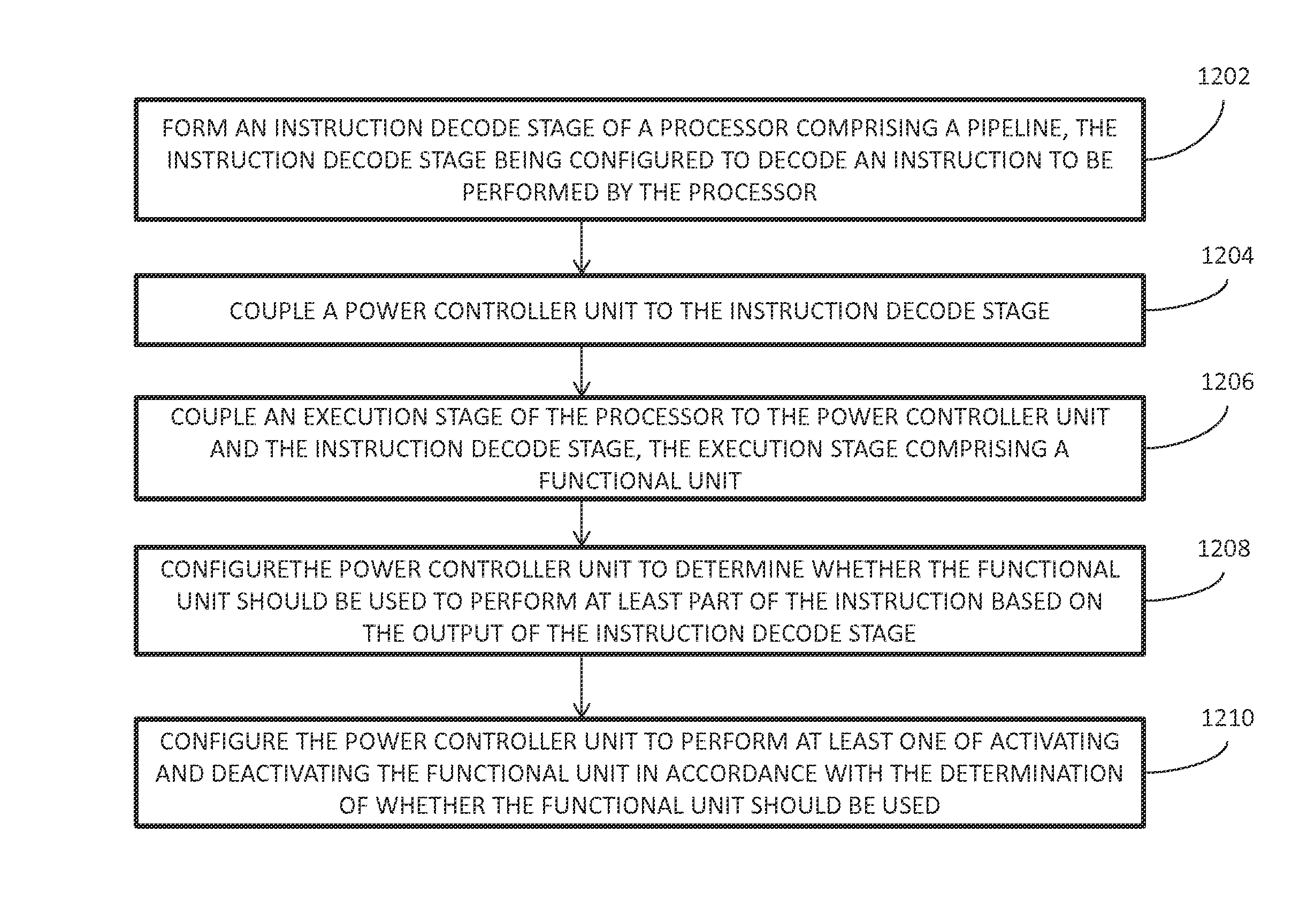

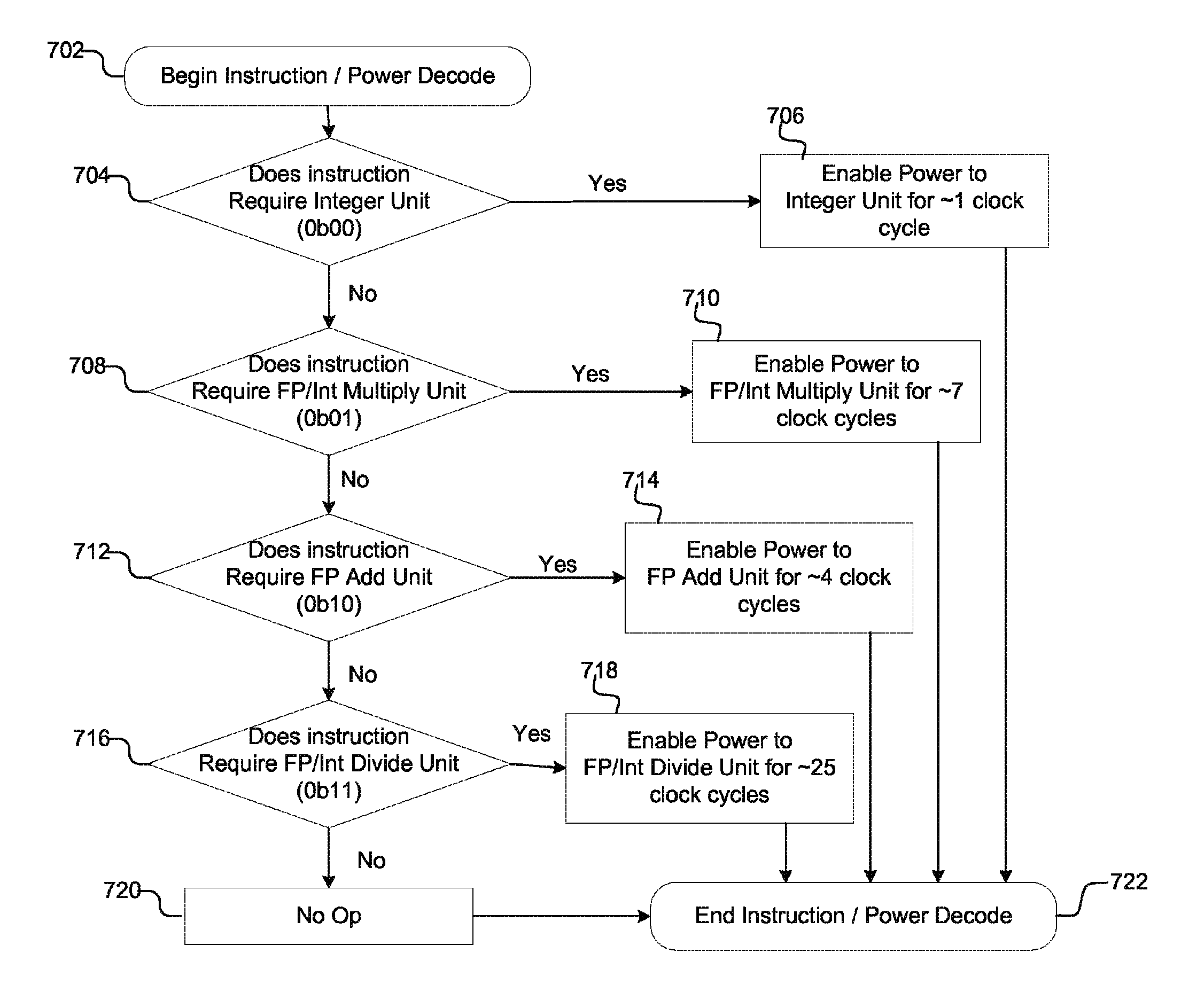

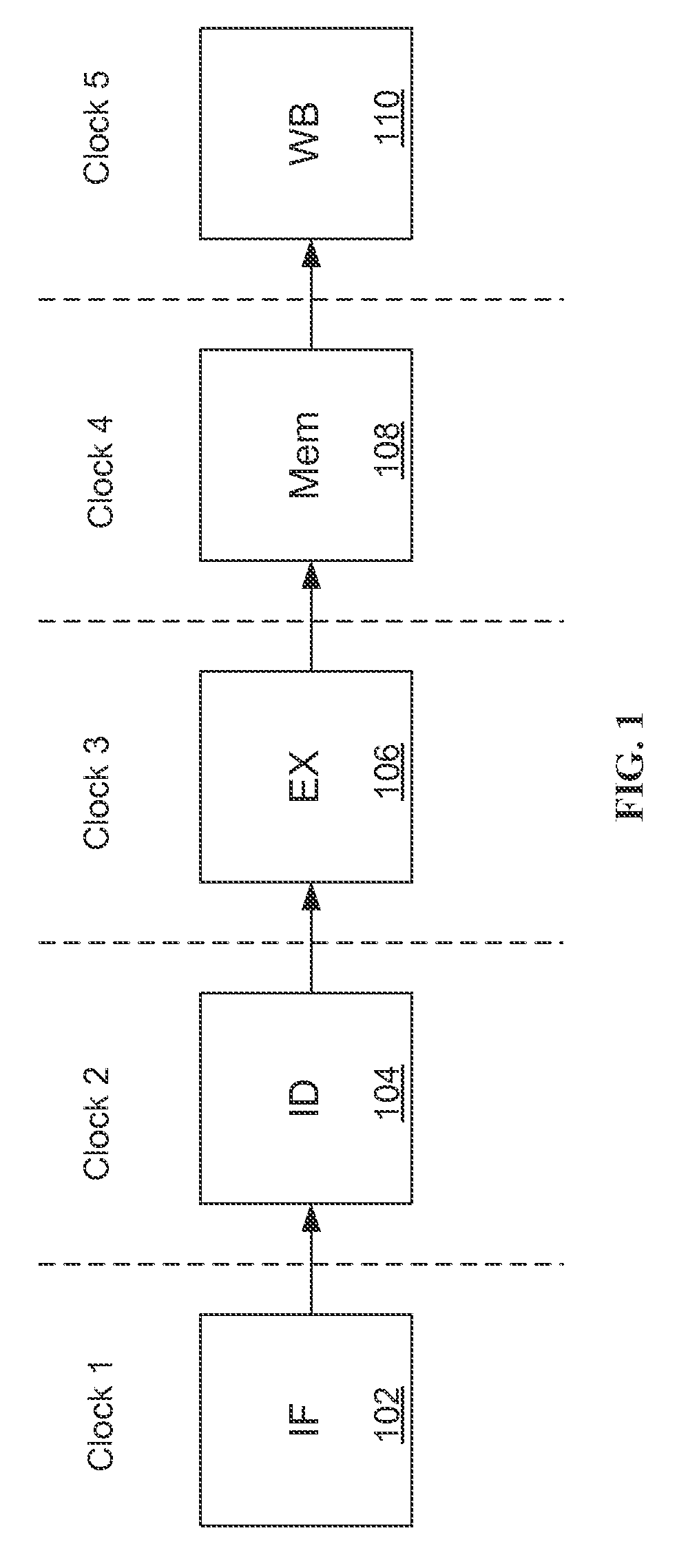

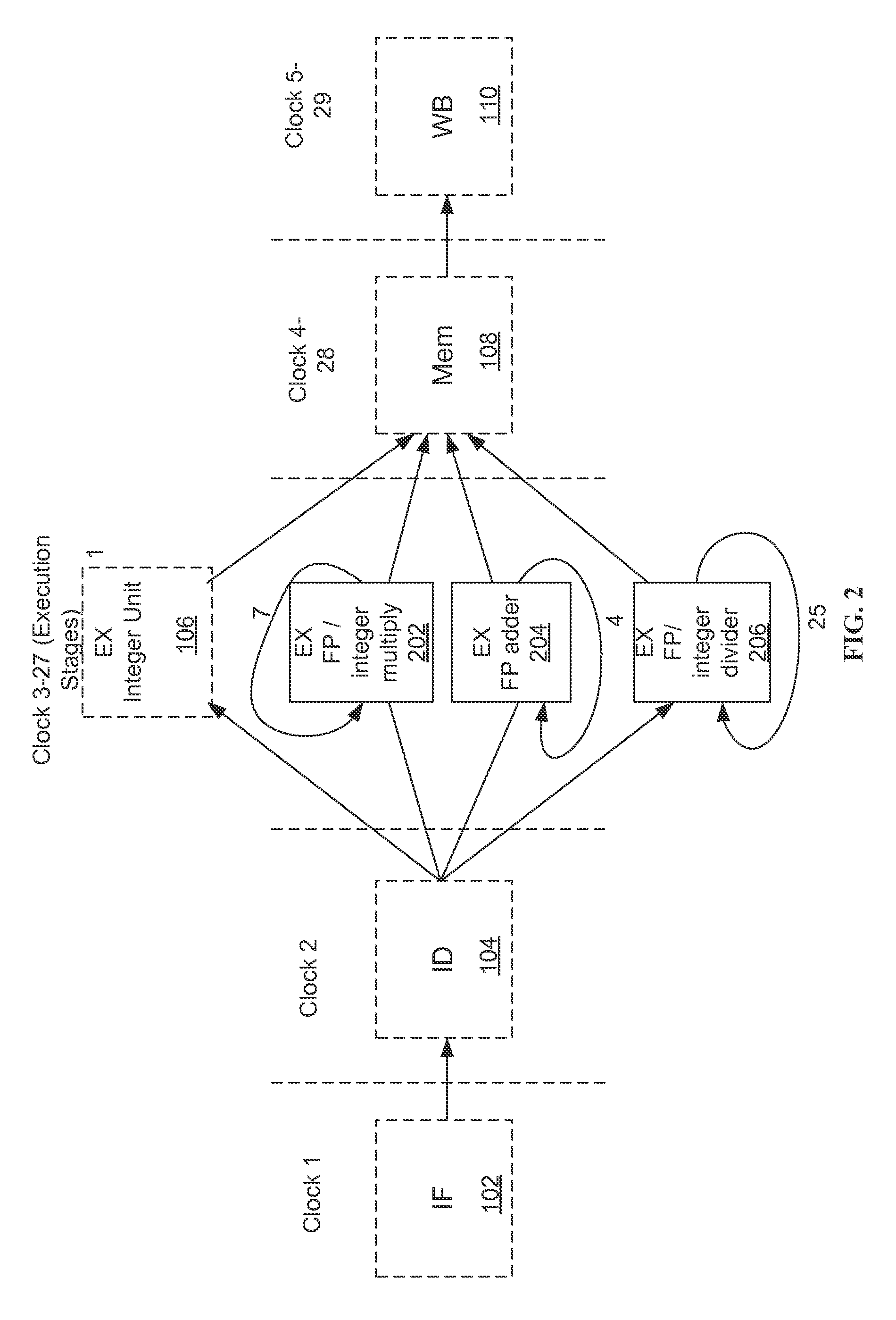

Autonomous microprocessor re-configurability via power gating execution units using instruction decoding

ActiveUS20140047258A1Shortened battery lifeIncrease temperaturePower supply for data processingEnergy efficient computingPower controllerControl system

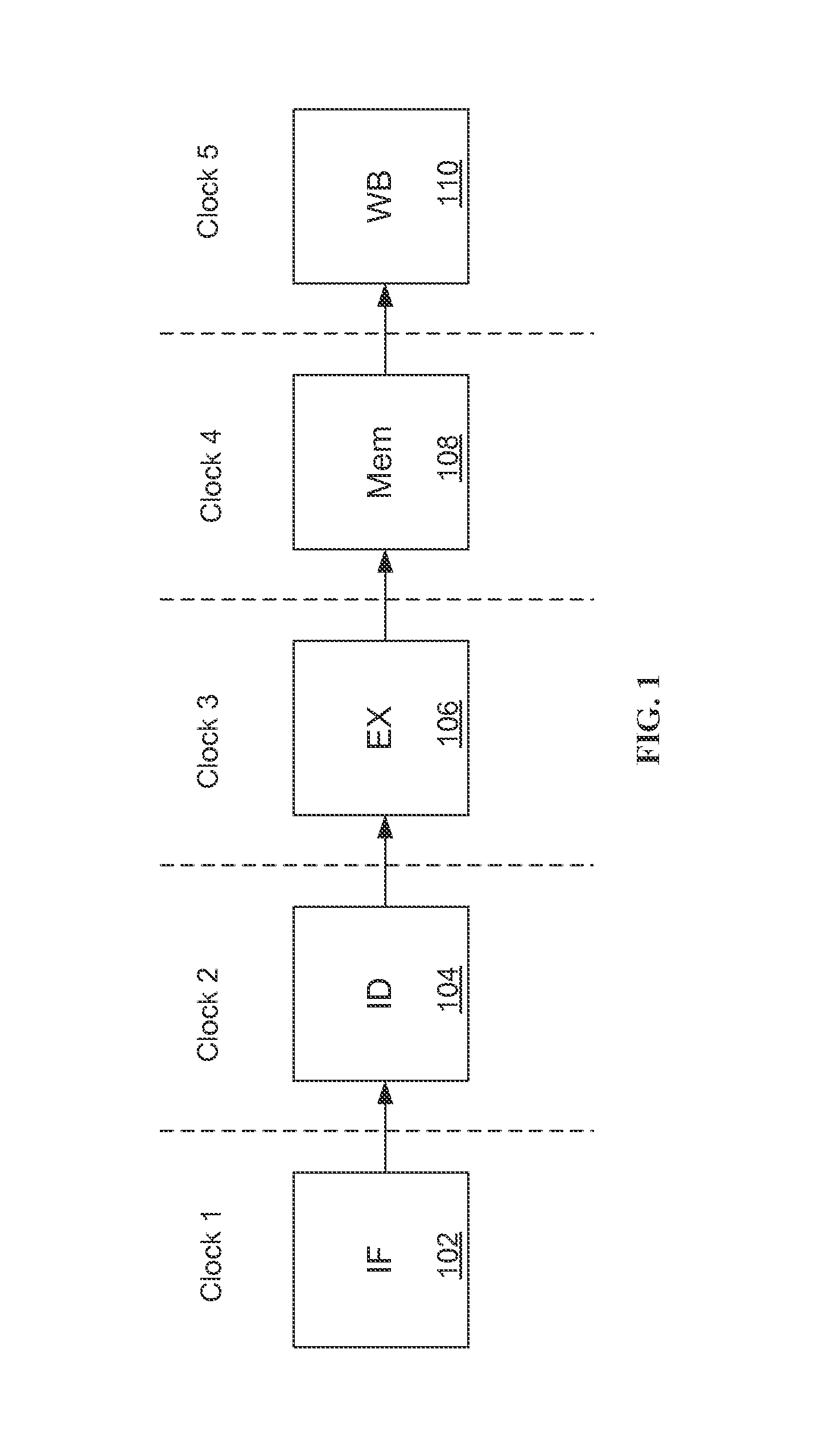

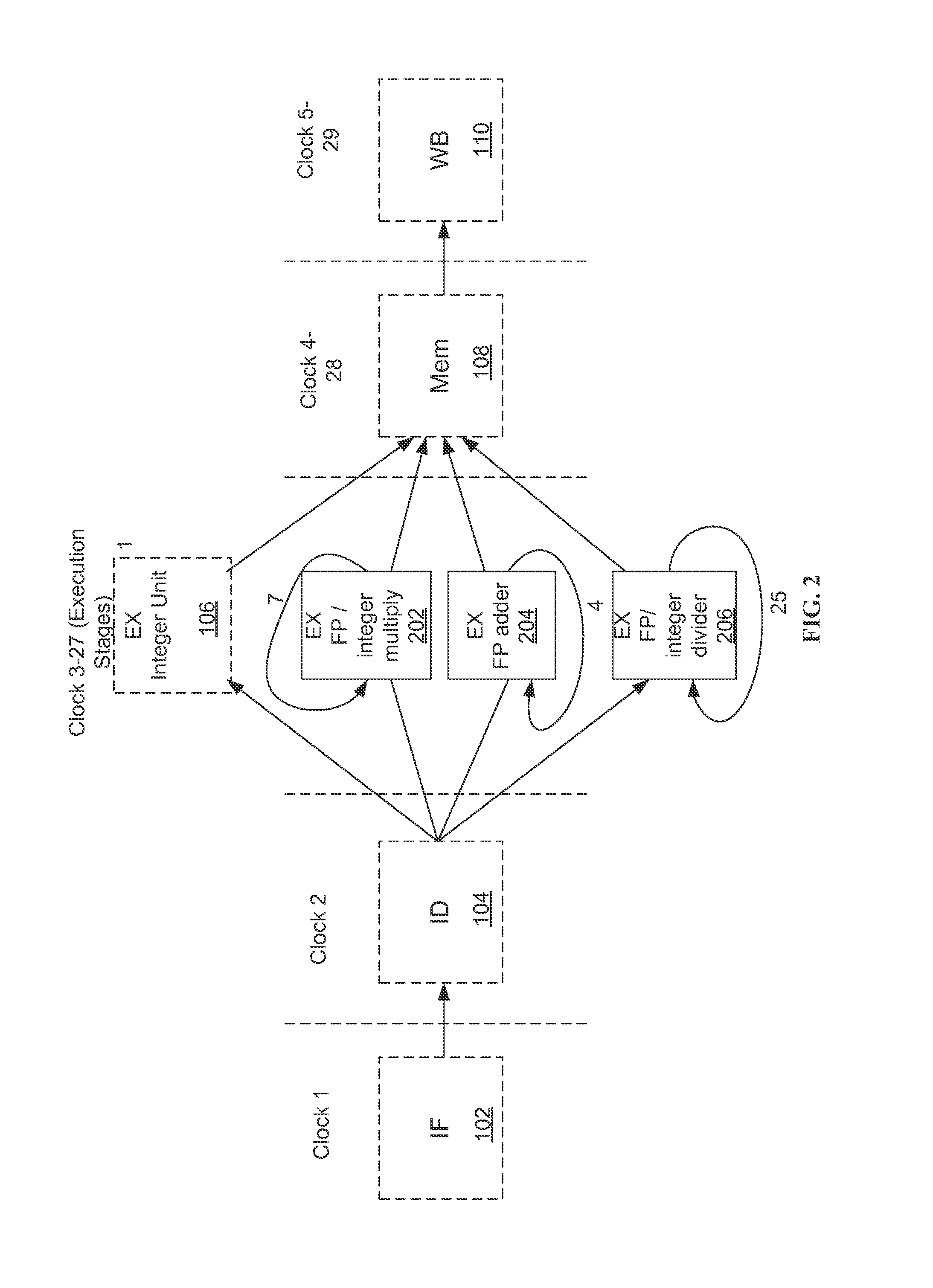

In an embodiment, a functional unit control system includes an instruction decoder of a processor comprising a pipeline, the instruction decoder being configured to decode an instruction to be performed by the processor. The system further includes a power controller unit coupled to the instruction decoder, and a functional unit which may operate during execution stages of the processor's pipeline coupled to the power controller unit and the instruction decode stage. The power controller unit is configured to determine whether the functional unit should be used to perform at least part of the instruction based on data of the instruction decoder. The power controller unit is further configured to perform at least one of activating and deactivating the functional unit in accordance with the determination of whether the functional unit should be used.

Owner:VAMPIRE LABS

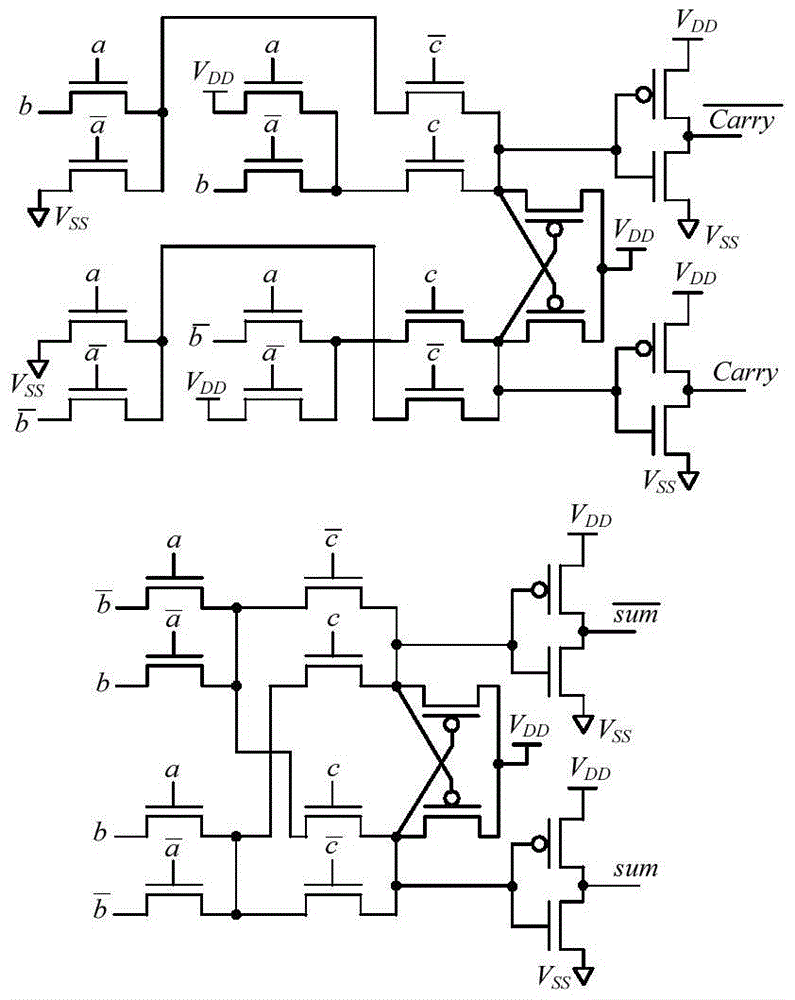

Single track current mode one bit full adder based on FinFET device

ActiveCN106505995AReduce areaImprove stabilityLogic circuits characterised by logic functionDigital data processing detailsMulti inputHemt circuits

Owner:宁波华盾新能源科技有限公司

Low switching power limited switch dynamic logic

InactiveUS6940312B2Improve performanceEliminate Static Power ConsumptionElectric pulse generatorLogic circuitsPre-chargeP channel

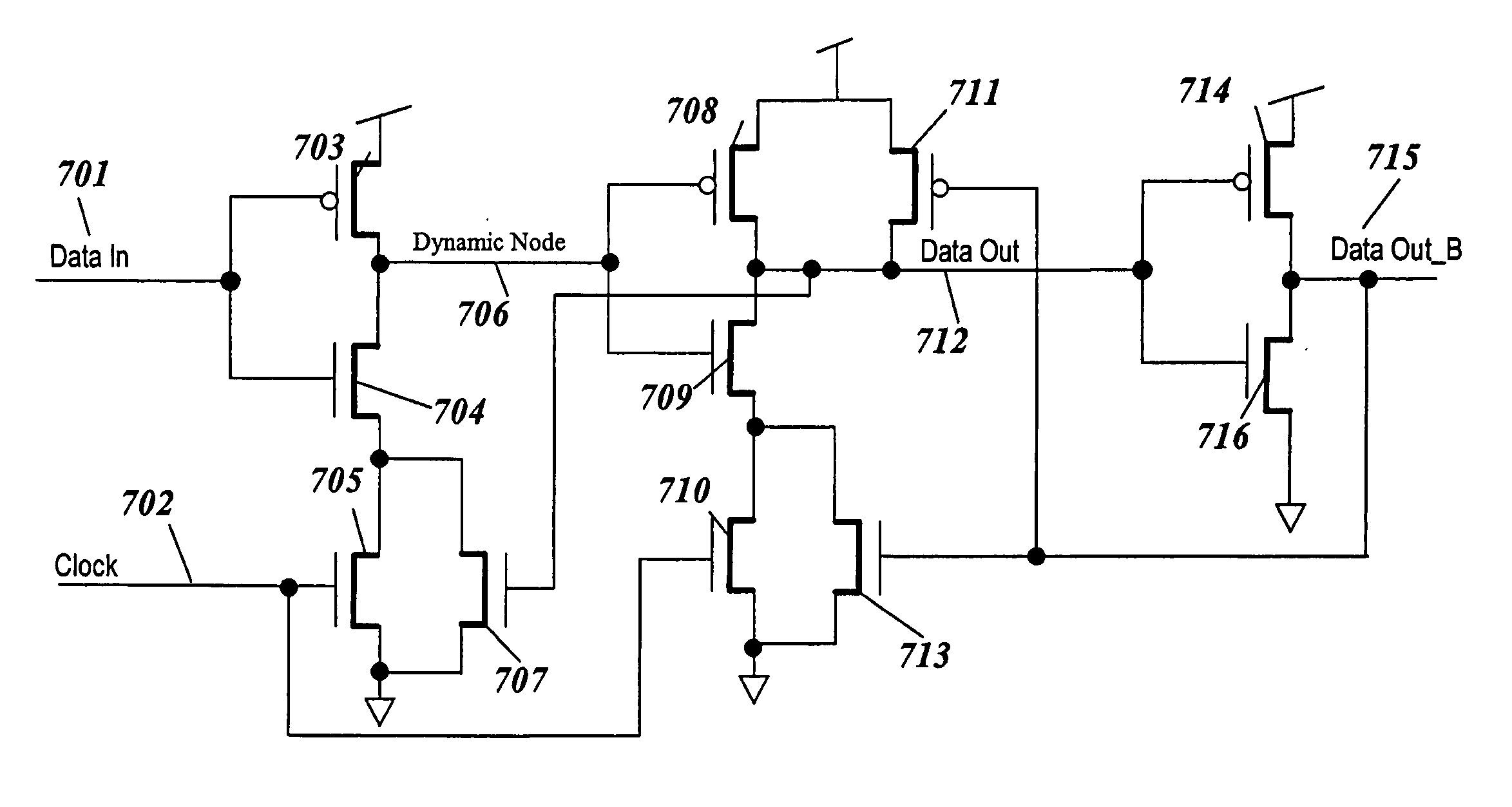

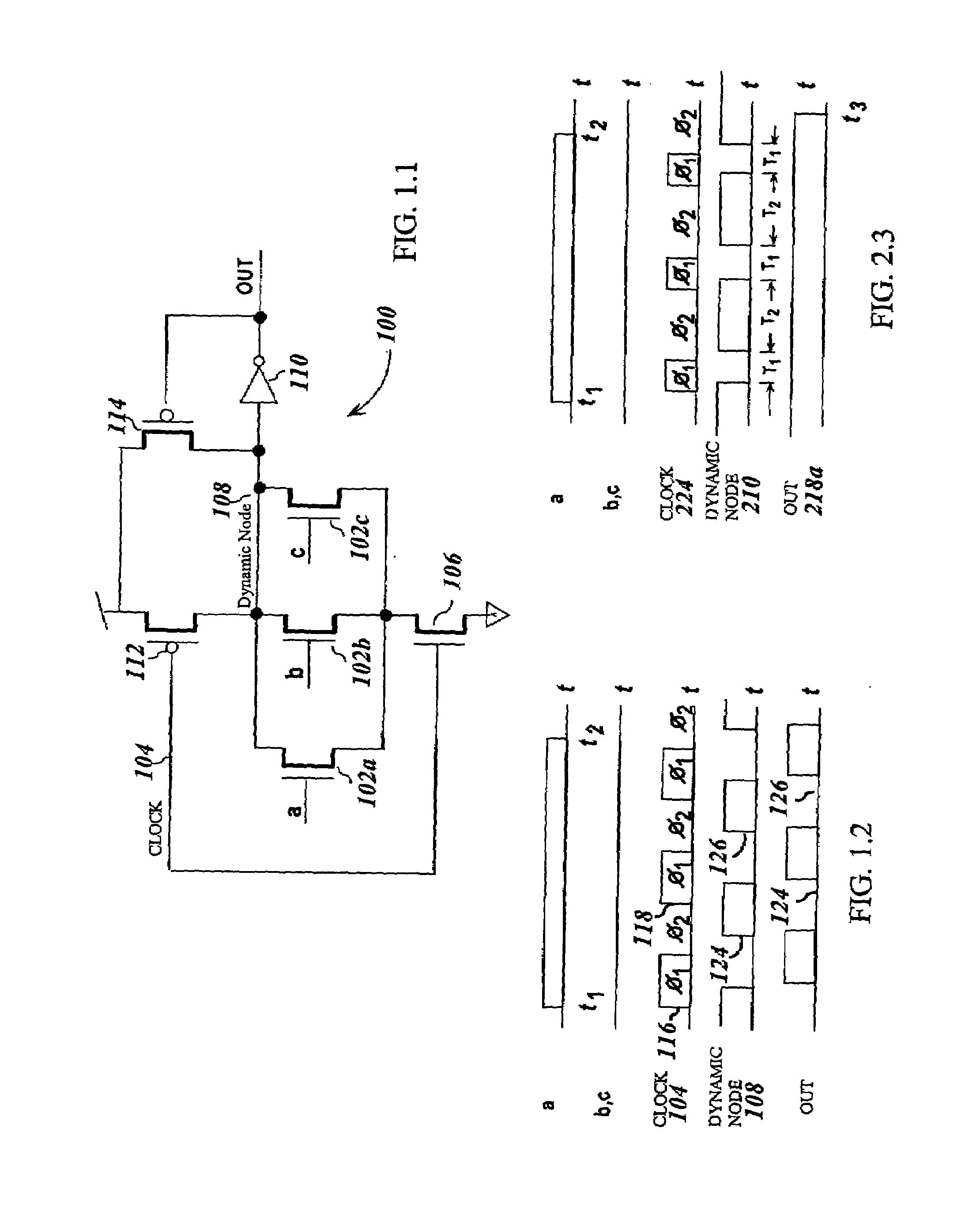

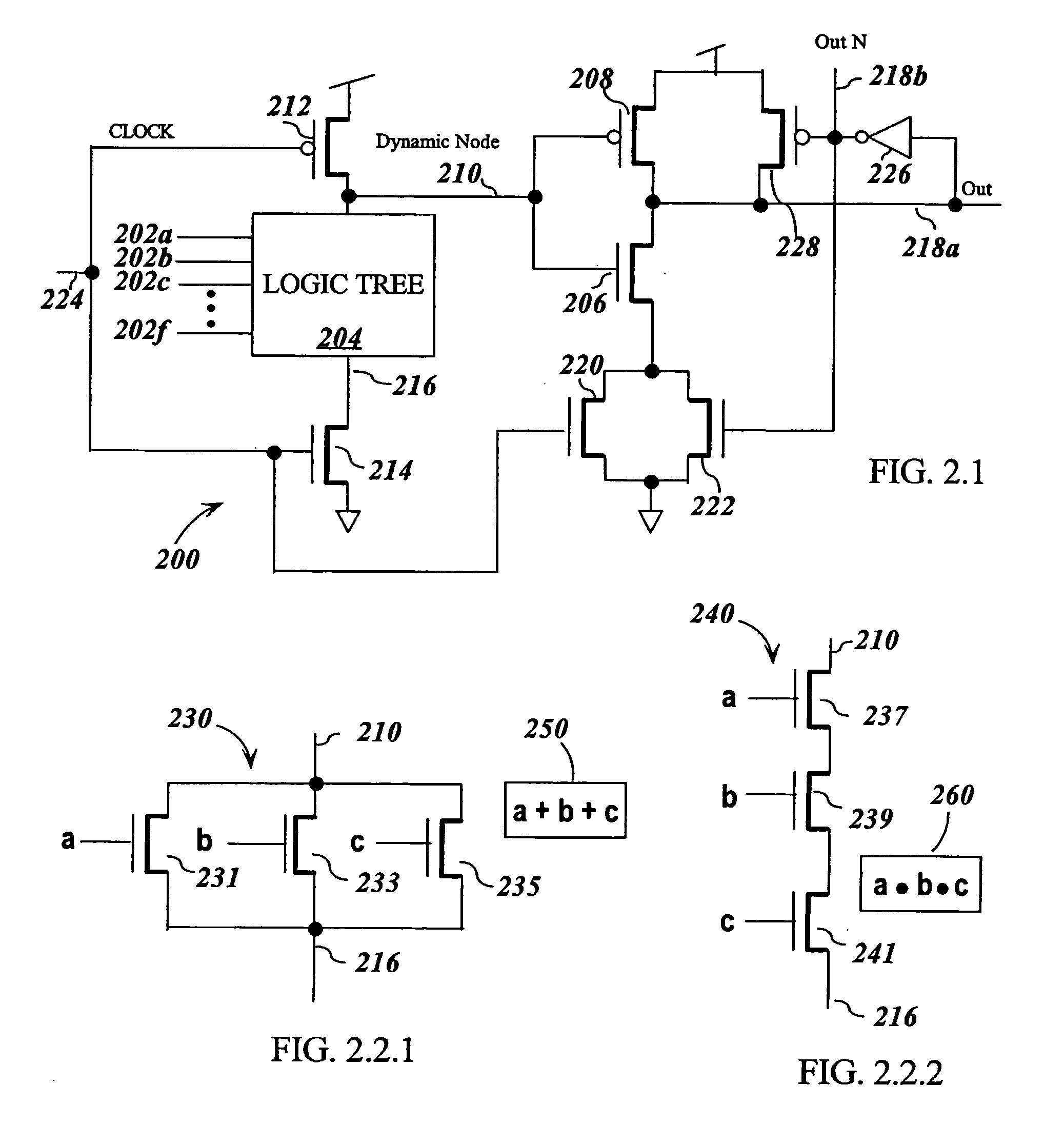

An LSDL circuit is improved by having the data input function to control the pre-charging of the dynamic node. The clock signal no longer is coupled to the P channel FET used to pre-charge the dynamic node. Additionally an N channel FET (NFET) is added in parallel with the NFET coupled to the clock for evaluating the dynamic node. This NFET assures the dynamic node does not float when the data input is a logic one and the clock is a logic zero.

Owner:INT BUSINESS MASCH CORP

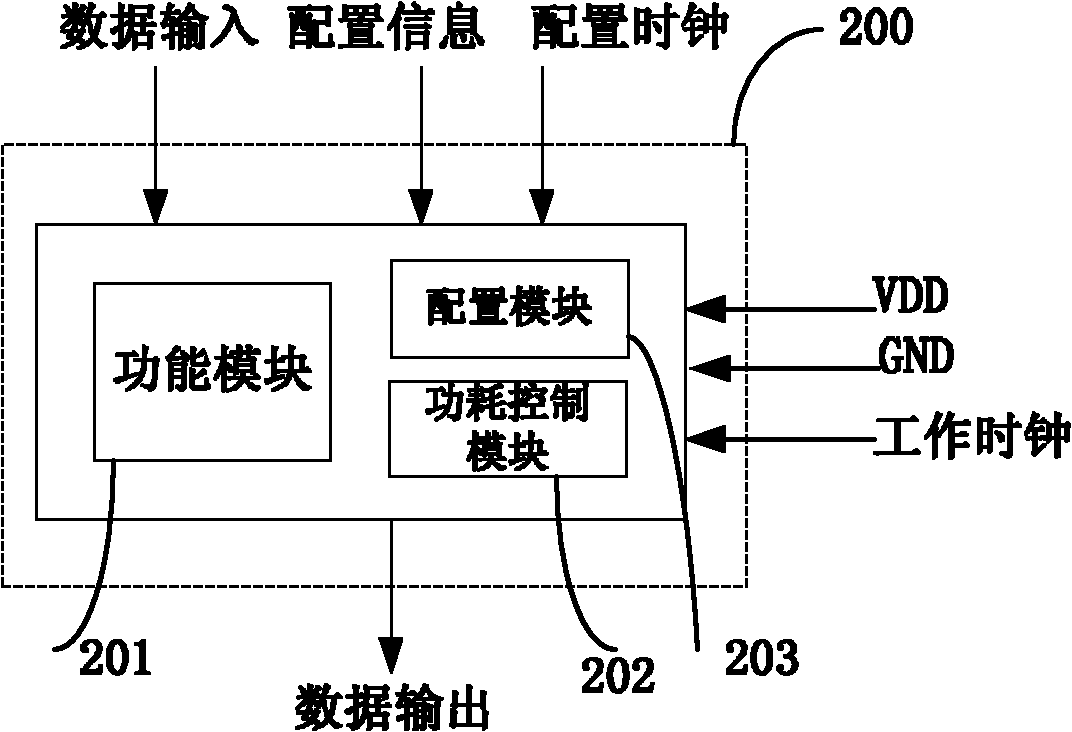

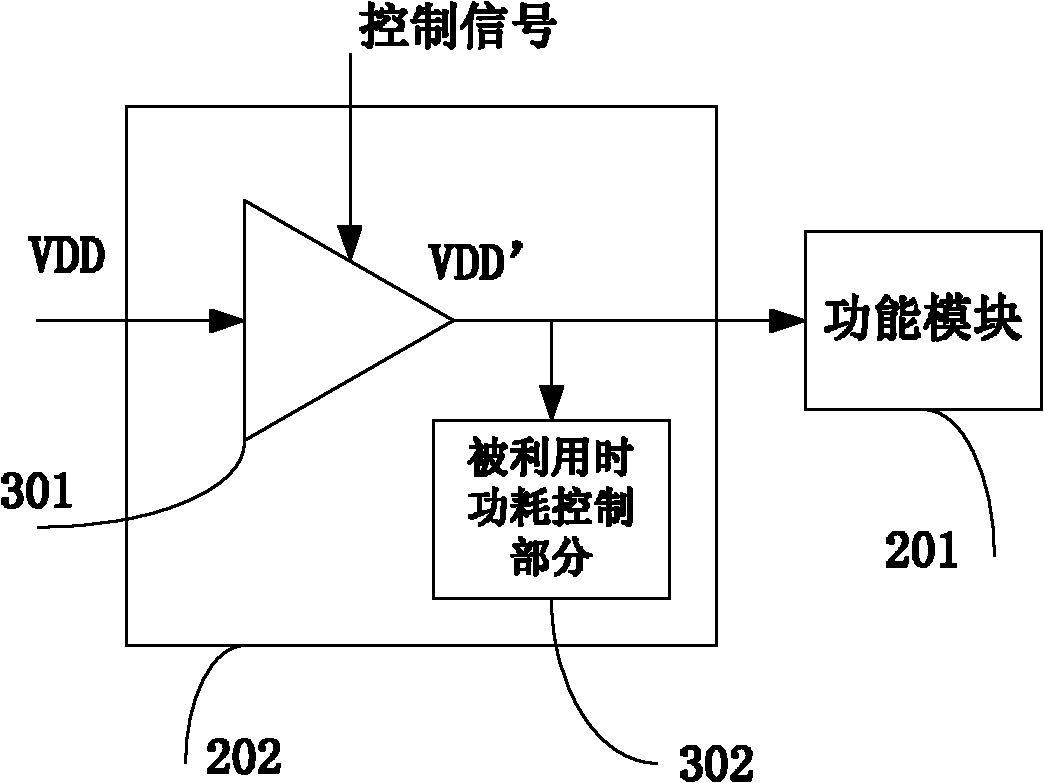

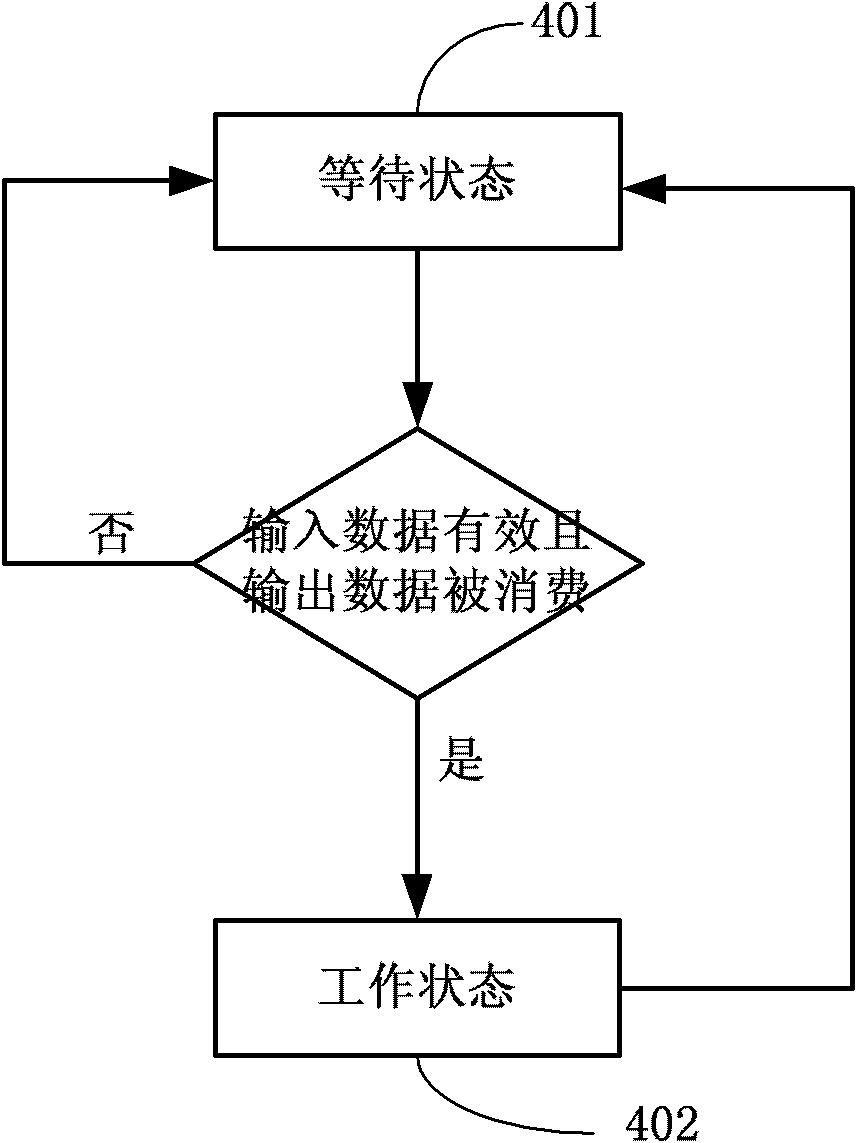

Reconfigurable operator, integrated circuit and method for reducing power consumption of reconfigurable operator

InactiveCN102184274AReduce jump rateEliminate Static Power ConsumptionSpecial data processing applicationsSpecific functionEngineering

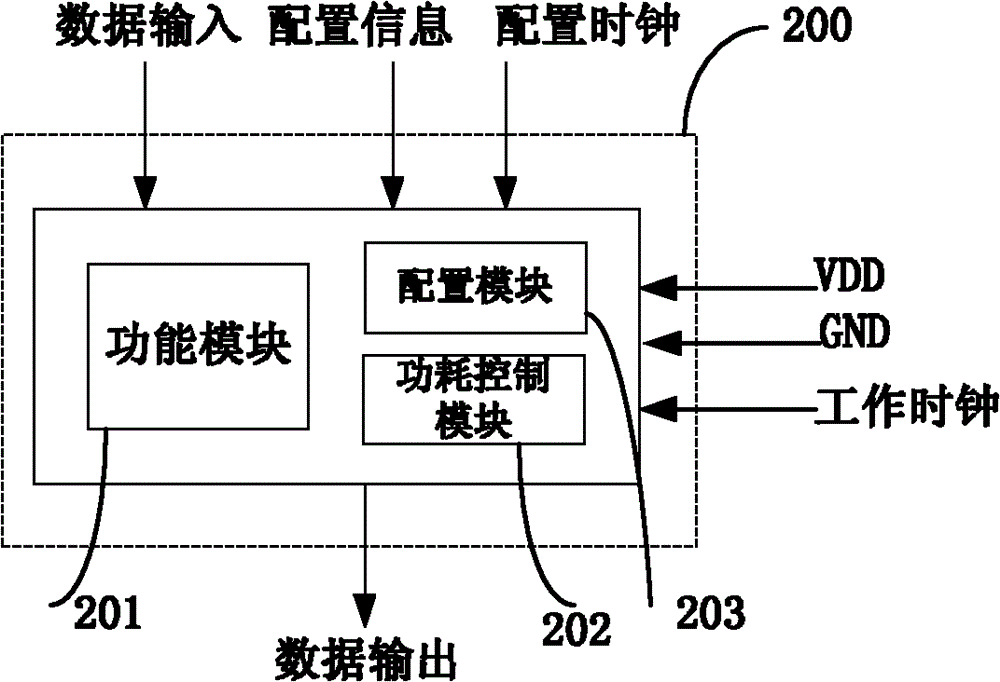

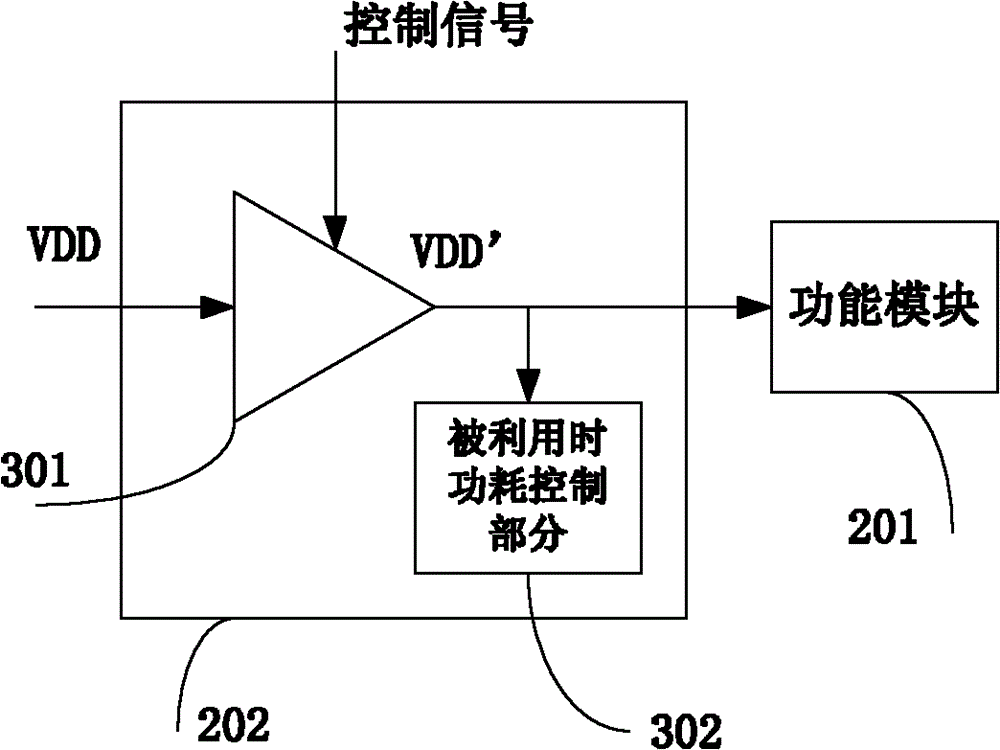

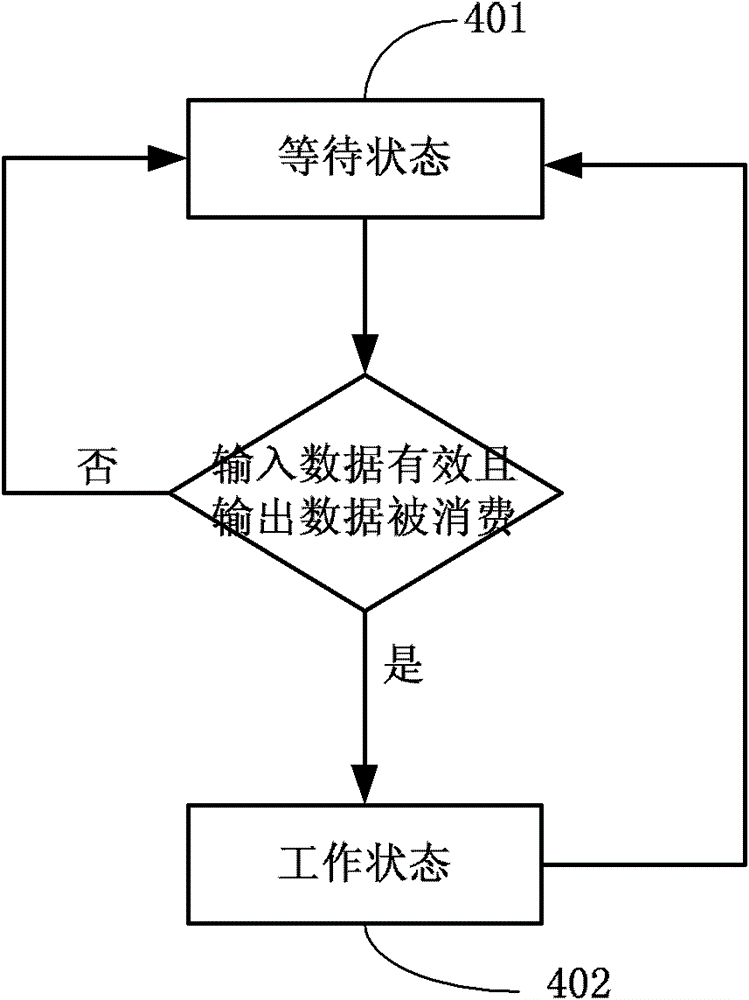

The invention discloses a reconfigurable operator, which comprises a power consumption control module, wherein the power consumption control module is used for controlling the power consumption of the reconfigurable operator; and the power consumption control module can control the power supply situation of the reconfigurable operator when a functional unit of the reconfigurable operator does not realize any specific function, or control output data according to the continuity of data processing of the reconfigurable operator when the reconfigurable operator realizes some specific function so as to fulfill the aim of reducing the power consumption. The invention also discloses an integrated circuit which comprises the reconfigurable operator. The invention also discloses a method for reducing the power consumption of the reconfigurable operator according to a principle of controlling the power consumption by the reconfigurable operator.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

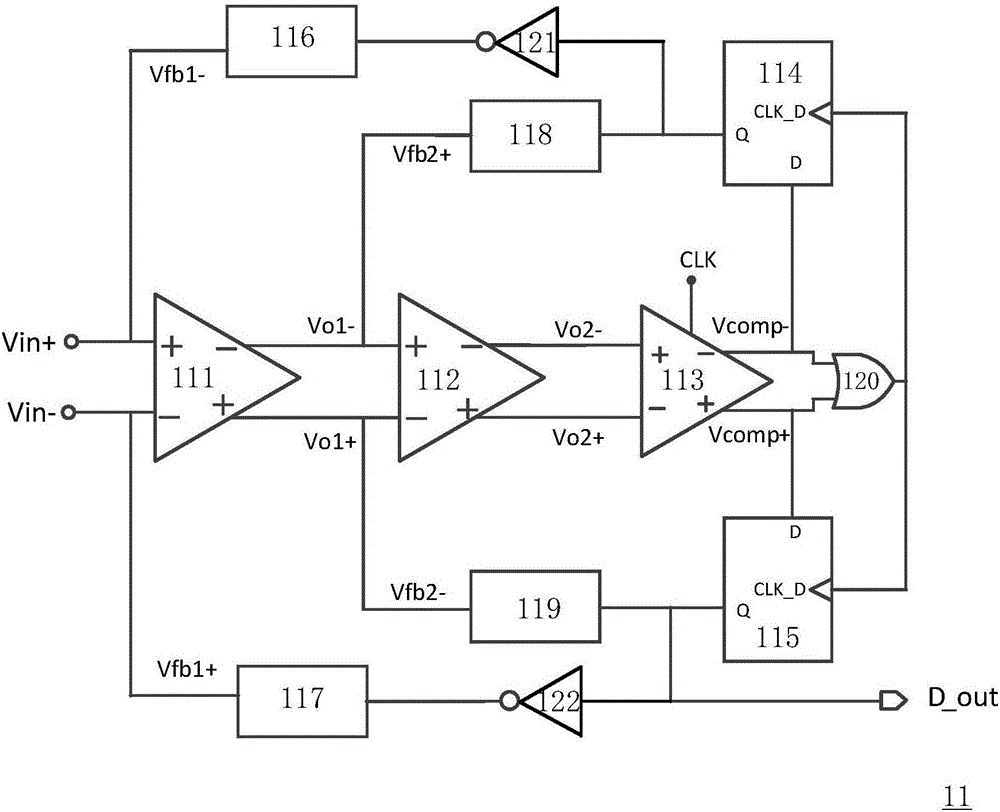

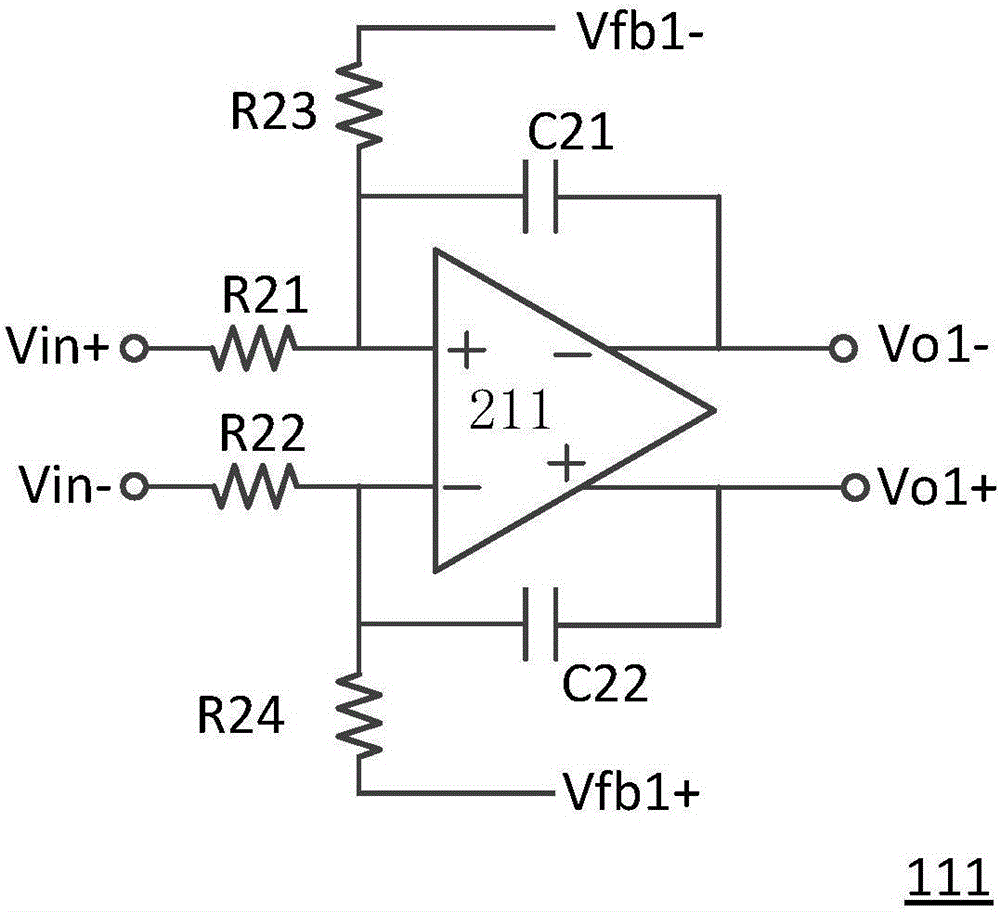

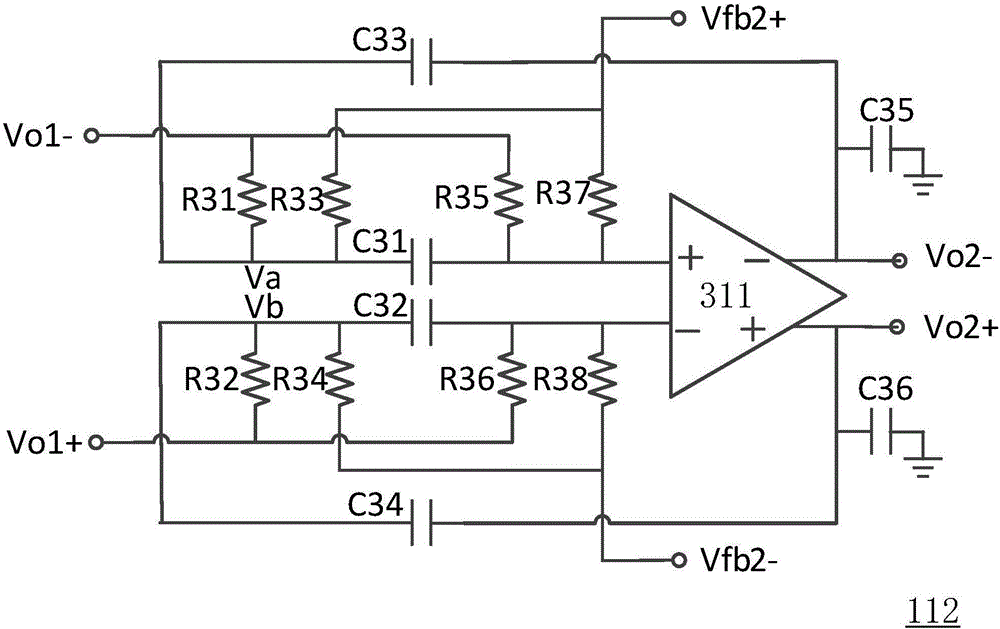

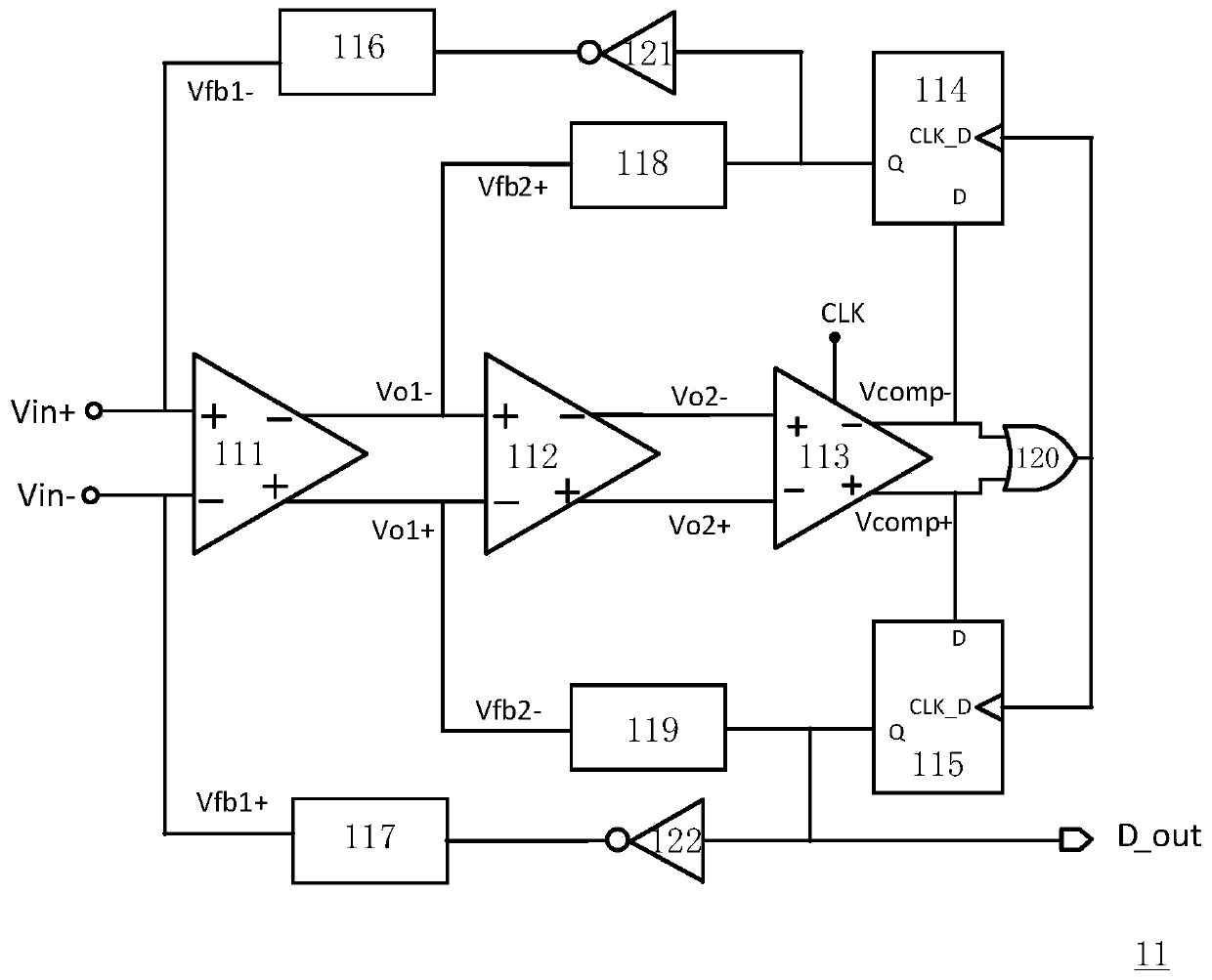

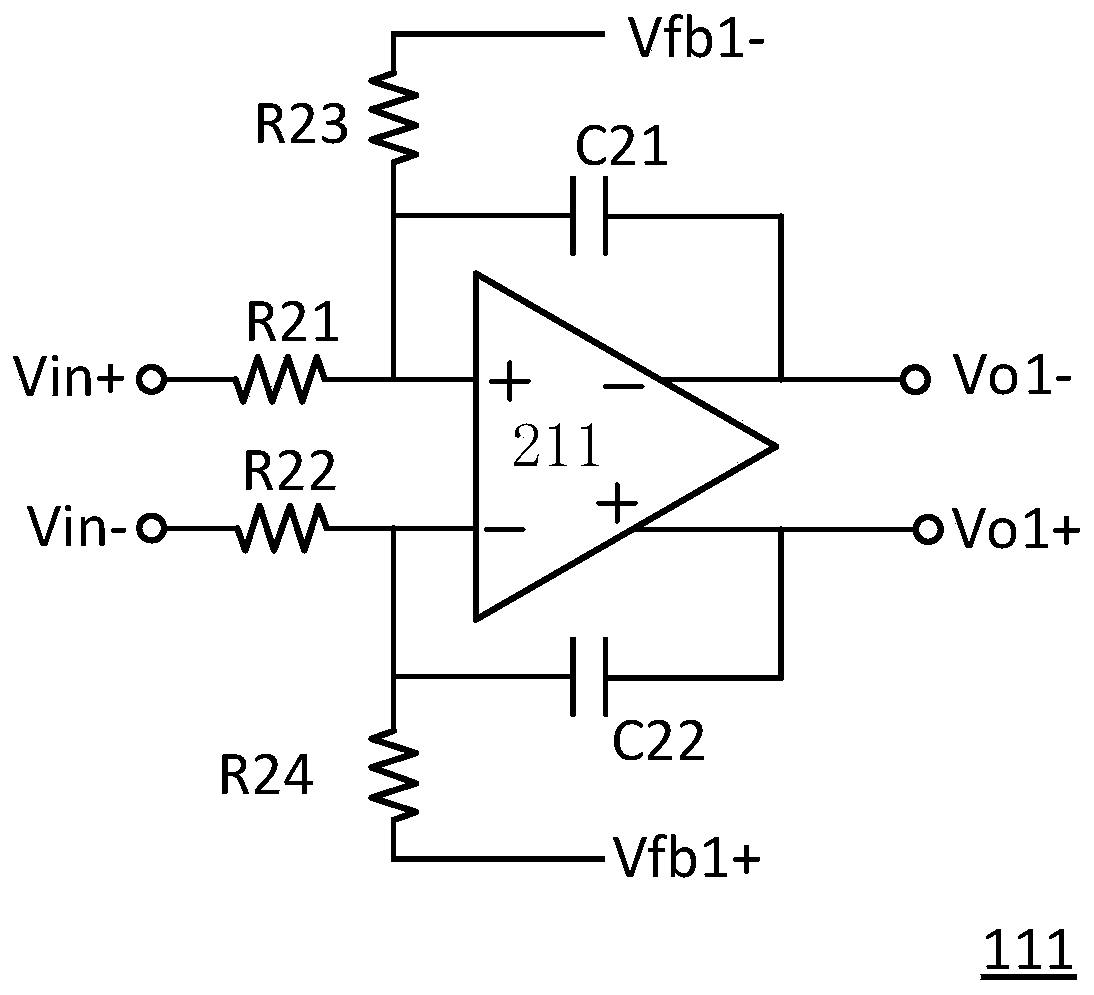

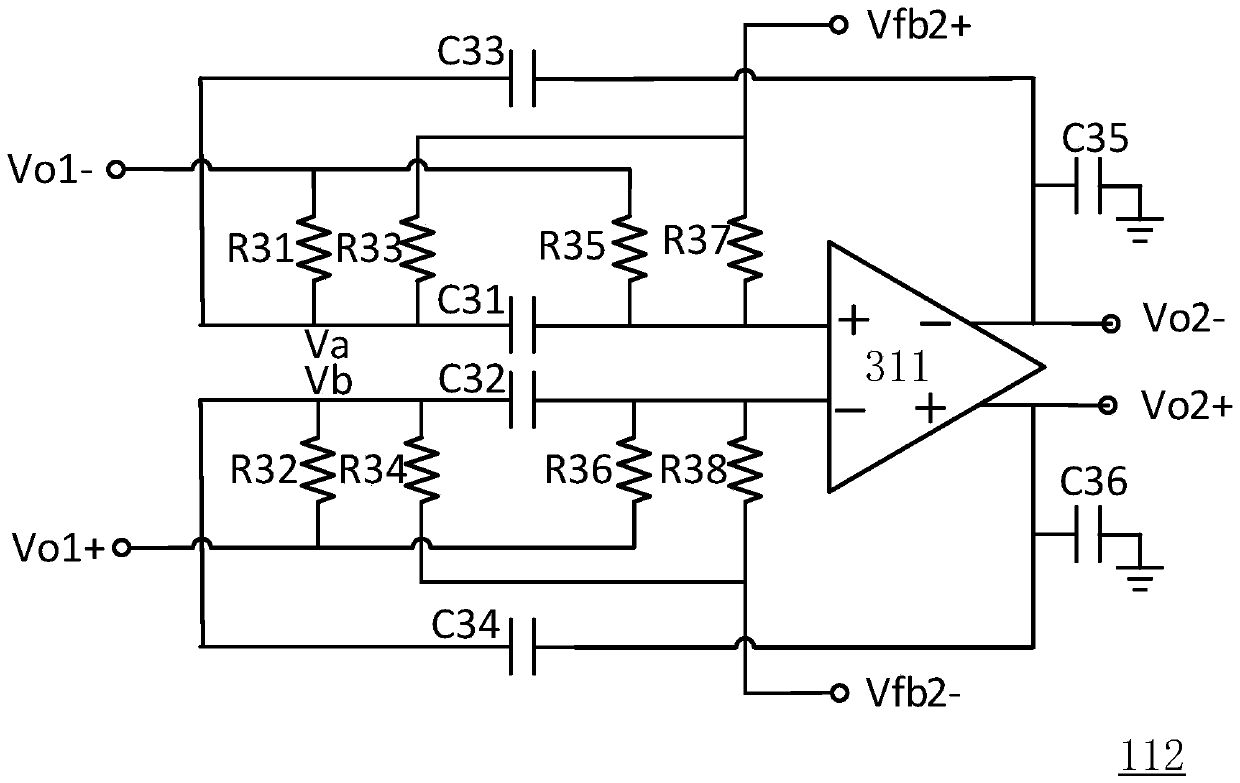

Continuous 3-order sigma-delta modulator circuit based on active resistance-capacitance integrator

ActiveCN106849953AImprove linearityEliminate Static Power ConsumptionAnalogue conversionCapacitanceDigital analog converter

The invention relates to a continuous 3-order sigma-delta modulator circuit (11) based on an active resistance-capacitance integrator. The circuit comprises a first integrator (111), a second integrator (112), a comparator (113), a first trigger (114), a second trigger (115), a first digital to analog converter (116), a second digital to analog converter (117), a third digital to analog converter (118), a fourth digital to analog converter (119), a logical OR circuit (120), a first inverter (121) and a second inverter (122). By adopting the circuit disclosed by the invention, the power consumption of the circuit can be significantly reduced.

Owner:XIDIAN UNIV

Individually activating or deactivating functional units in a processor system based on decoded instruction to achieve power saving

ActiveUS9218048B2Shortened battery lifeIncrease temperatureEnergy efficient ICTPower supply for data processingPower controllerControl system

In an embodiment, a functional unit control system includes an instruction decoder of a processor comprising a pipeline, the instruction decoder being configured to decode an instruction to be performed by the processor. The system further includes a power controller unit coupled to the instruction decoder, and a functional unit which may operate during execution stages of the processor's pipeline coupled to the power controller unit and the instruction decode stage. The power controller unit is configured to determine whether the functional unit should be used to perform at least part of the instruction based on data of the instruction decoder. The power controller unit is further configured to perform at least one of activating and deactivating the functional unit in accordance with the determination of whether the functional unit should be used.

Owner:VAMPIRE LABS

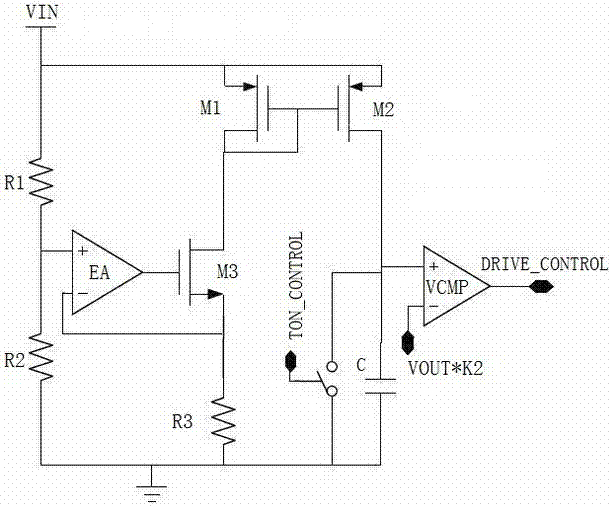

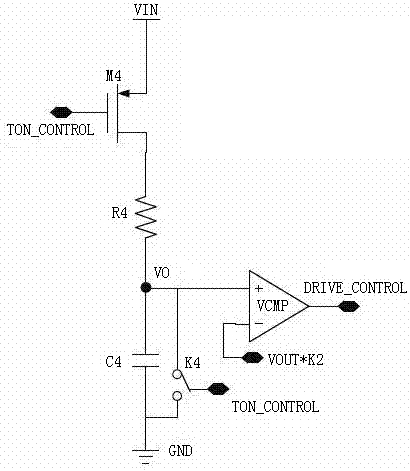

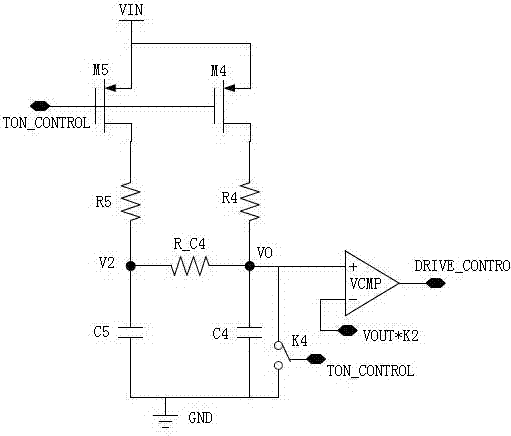

Low-power-consumption constant conduction time timing circuit design method and timing circuit

PendingCN107968568AEliminate Static Power ConsumptionReduce power consumptionMultiple input and output pulse circuitsEfficient power electronics conversionCapacitanceEngineering

The invention provides a low-power-consumption constant conduction time timing circuit design method and timing circuit. An RC circuit is adopted for timing and the static power consumption of the timer is eliminated. The concrete structure is that the timing circuit comprises a fourth PMOS transistor M4 of which the source electrode is connected with input voltage VIN, the gate electrode is connected with the conduction time control end TON_CONTROL and the drain electrode is connected with one end of a fourth resistor R4. The other end of the fourth resistor R4 is connected with one end of afourth capacitor C4. The other end of the fourth capacitor C4 is grounded. The input negative electrode of a comparator VCMP is connected with reference voltage, and the input positive electrode is connected between the fourth capacitor C4 and the fourth resistor R4. According to the circuit under the design method, the static power consumption of the constant conduction time timing circuit can beeliminated so that the power consumption of the whole circuit can be reduced, and the circuit structure is simple and the cost is low.

Owner:SICHUAN ENERGY INTERNET RES INST TSINGHUA UNIV

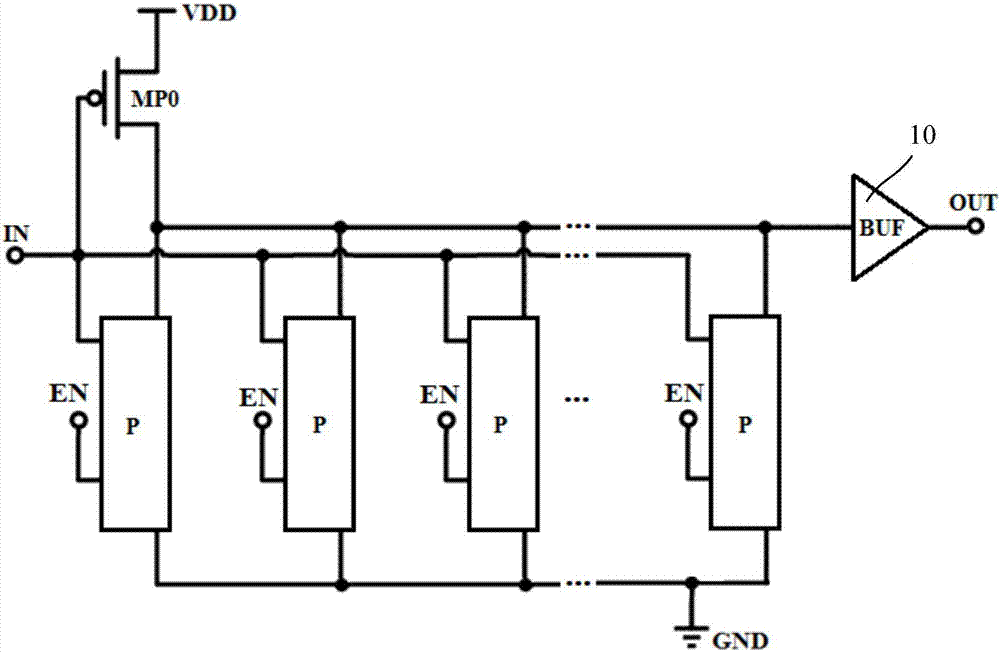

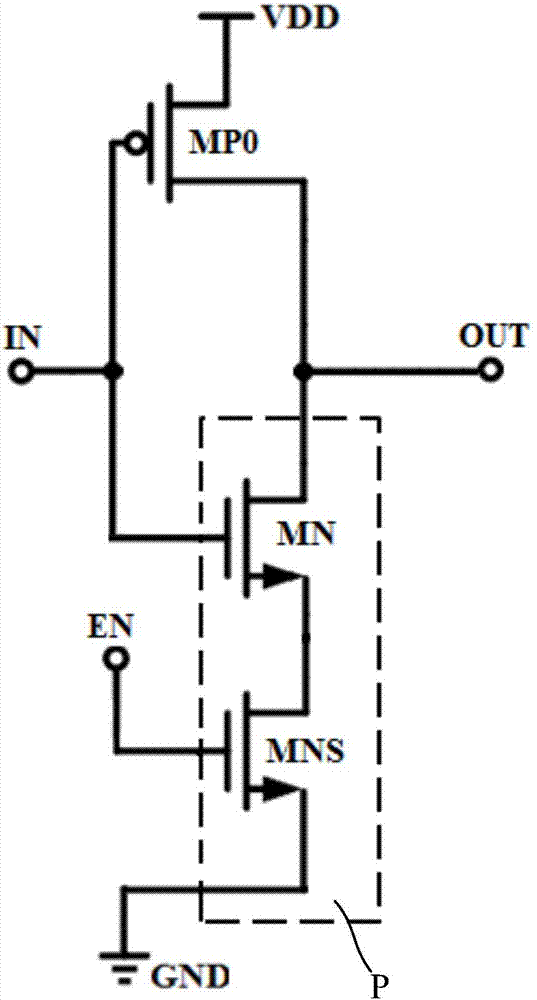

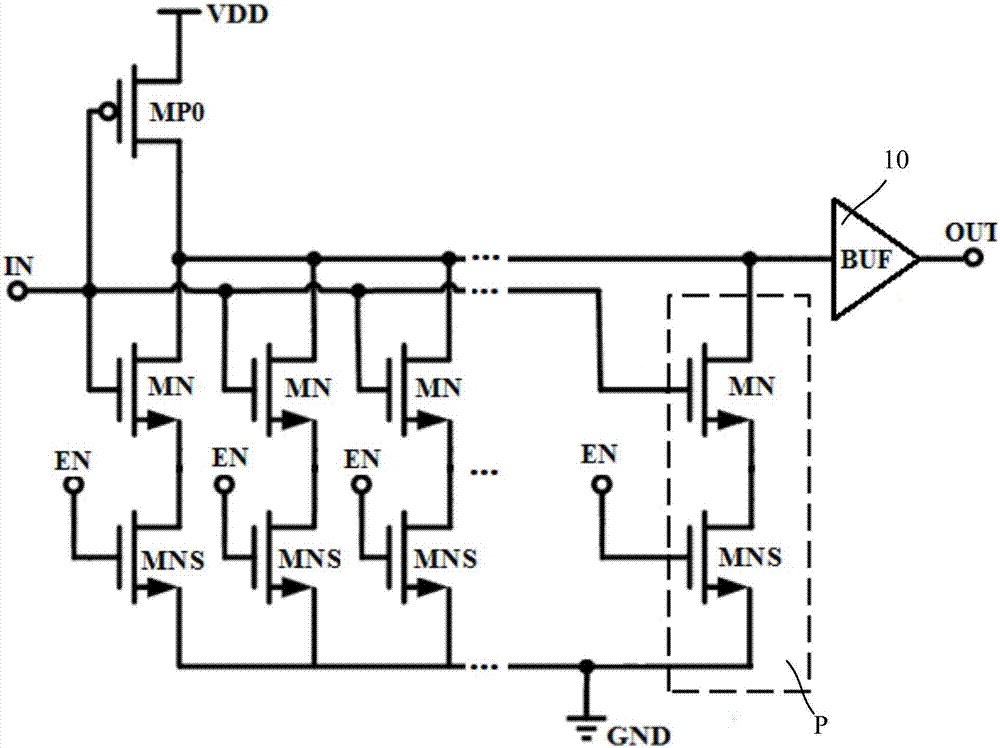

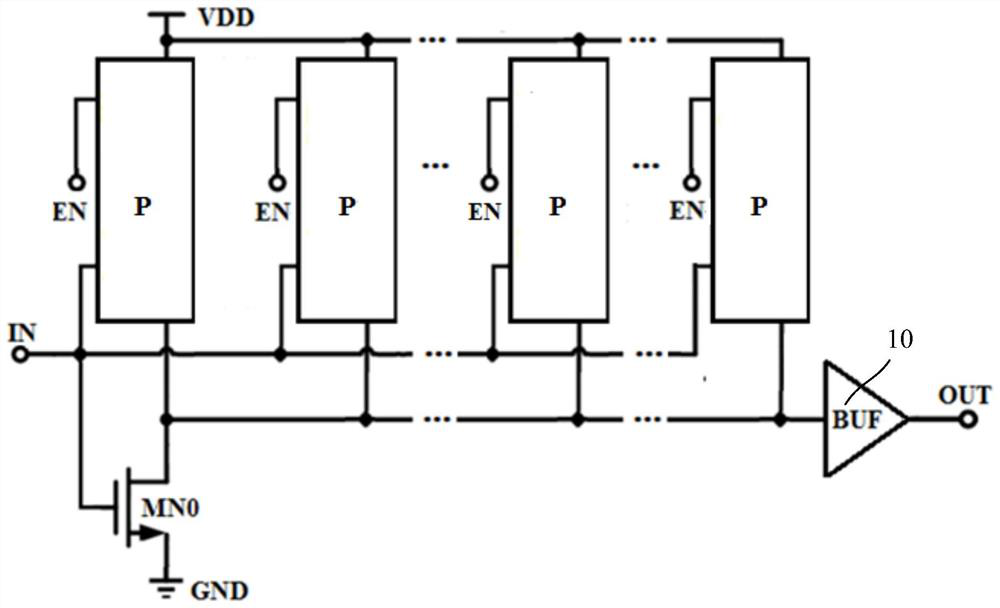

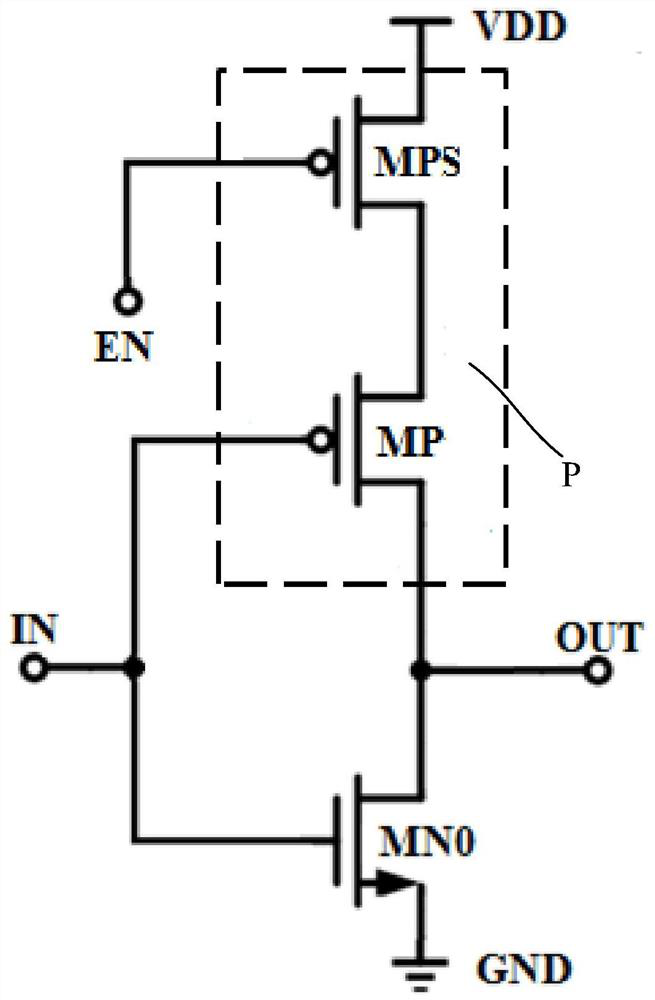

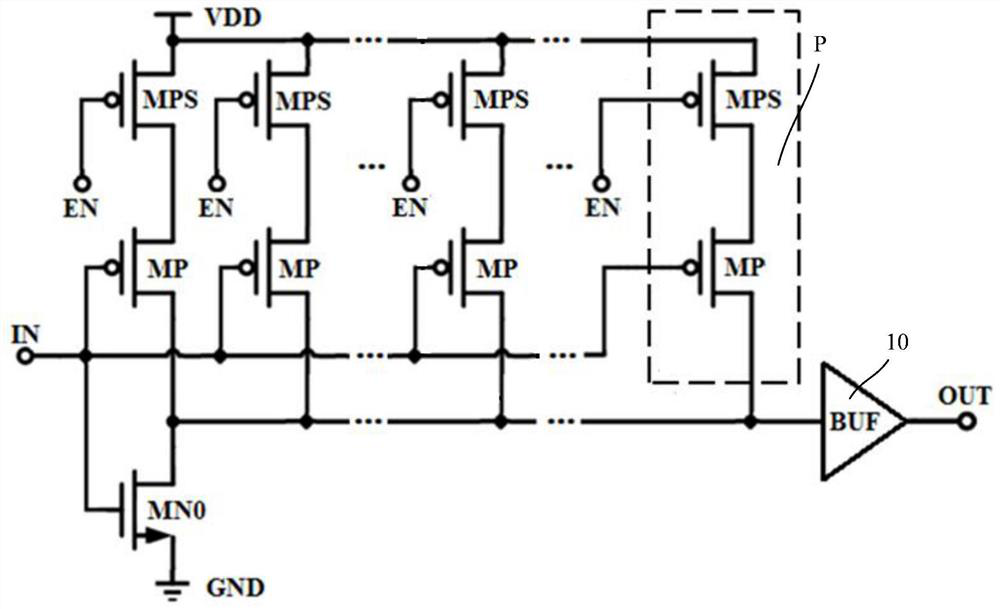

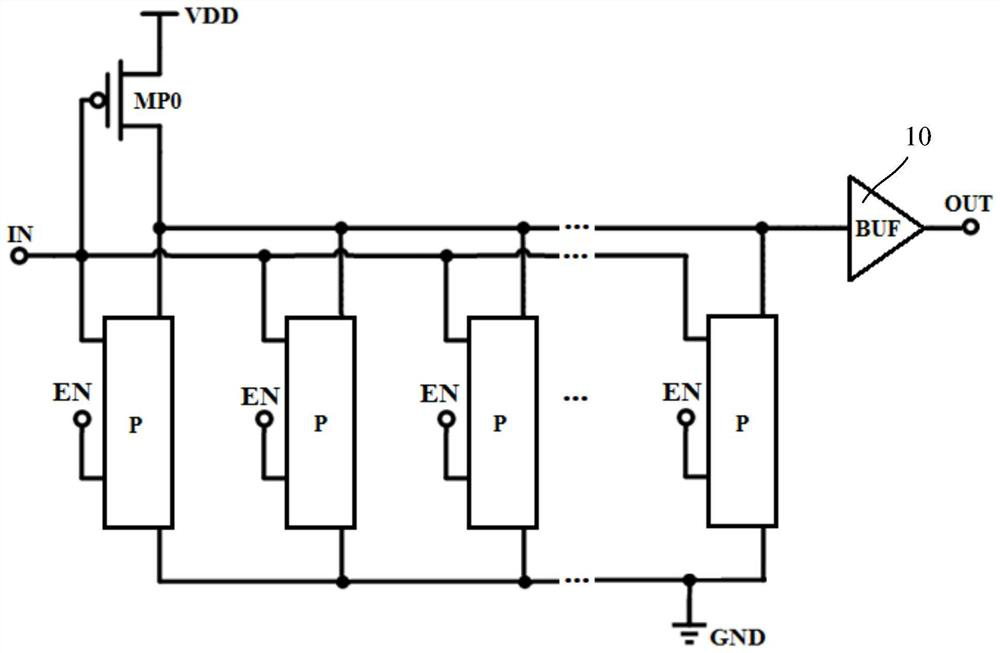

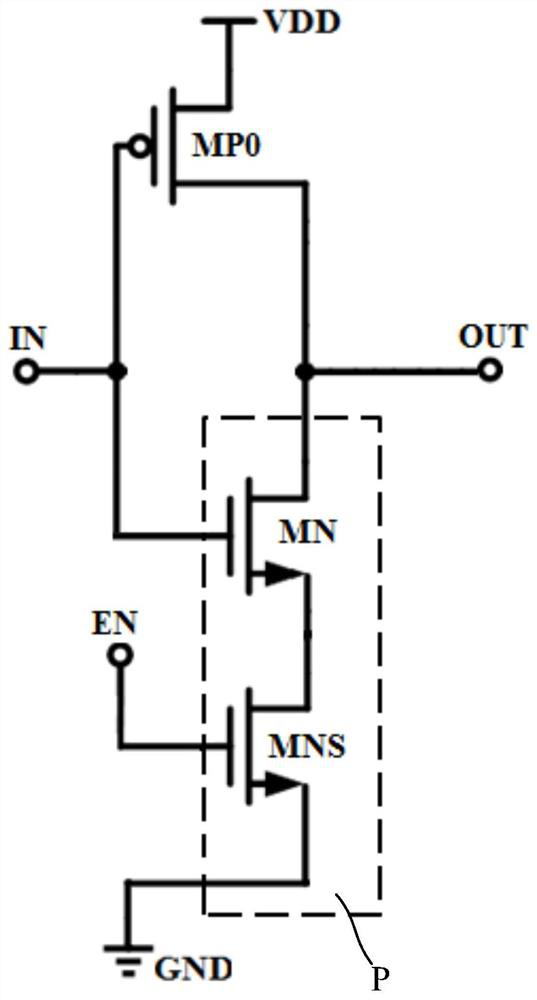

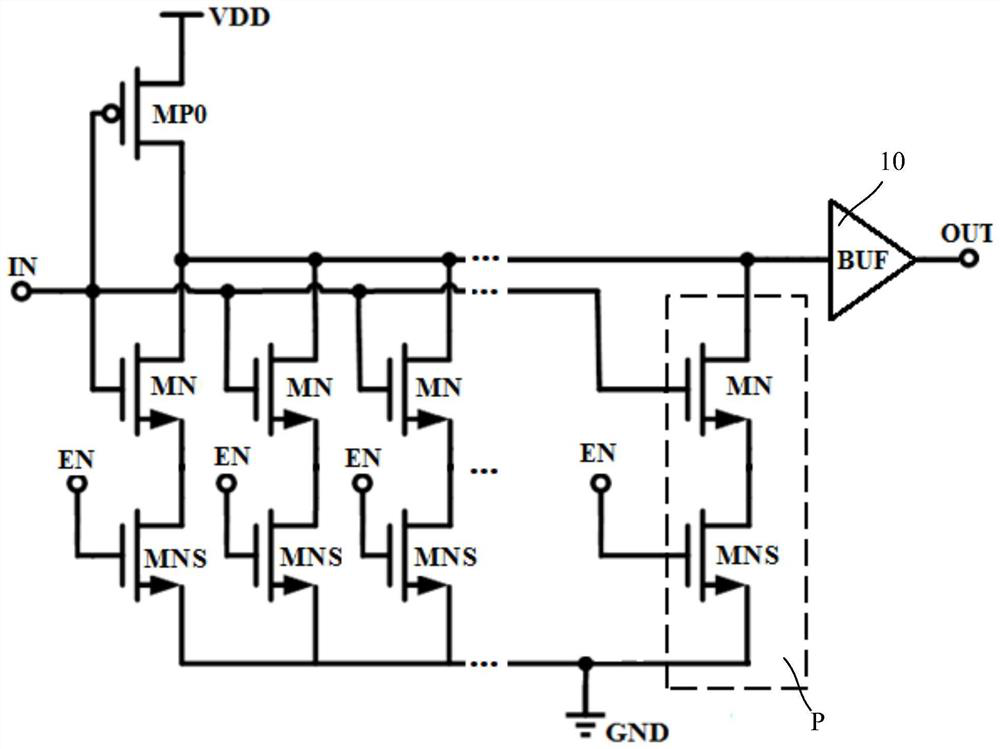

Discrete threshold voltage comparator with zero static power consumption

ActiveCN107196629AEliminate Static Power ConsumptionEliminate dead timeMultiple input and output pulse circuitsAnalogue-digital convertersVoltage regulationDigital control

The invention discloses a discrete threshold voltage comparator with zero static power consumption. The discrete threshold voltage comparator comprises a first transistor and a plurality of parallel threshold value adjustment branches, wherein each threshold value adjustment branch is connected with the first transistor and a digital enable bit of the voltage comparator, and each threshold value adjustment branch adjusts a threshold voltage of the voltage comparator according to a digital control signal received by the digital enable bit. According to the discrete threshold voltage comparator , the plurality of parallel threshold value adjustment branches are arranged in the voltage comparator, and the threshold voltage of the voltage comparator is adjusted based on the digital control signal received by the digital enable bit, thus the digital control of the threshold voltage of the voltage comparator is realized; and since the voltage comparator utilizes digital control for adjusting the threshold voltage, the threshold voltage is eliminated, the discrete threshold voltage comparator with zero static power consumption and adjustable threshold voltage values is implemented, reset operation is avoided and the system dead time is eliminated.

Owner:SHENZHEN UNIV

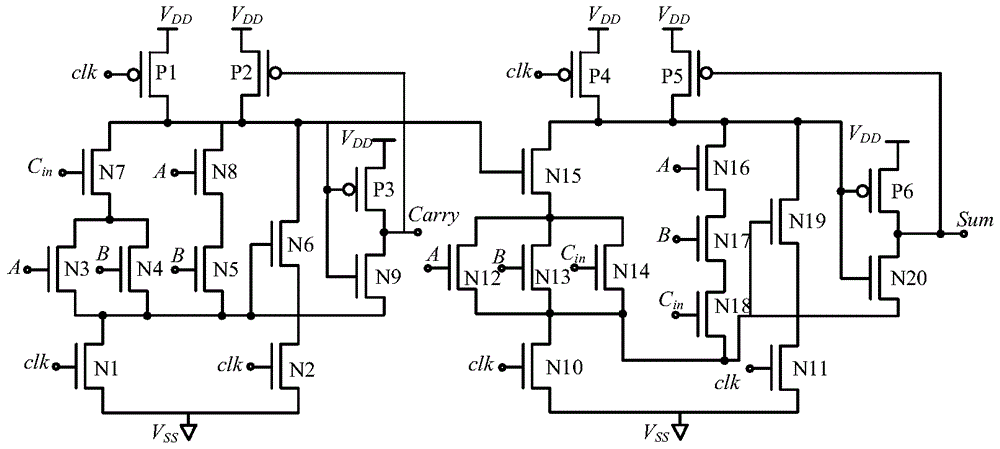

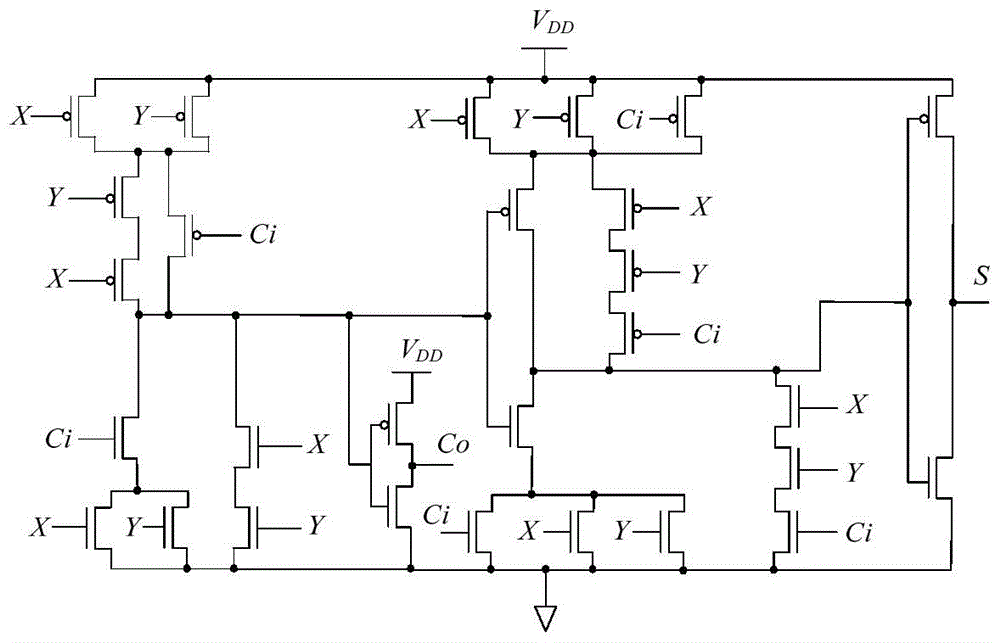

A cmos addition unit

ActiveCN104378104BReduce the numberEliminate Static Power ConsumptionLogic circuits characterised by logic functionCMOSHemt circuits

Owner:无锡三聚阳光知识产权服务有限公司

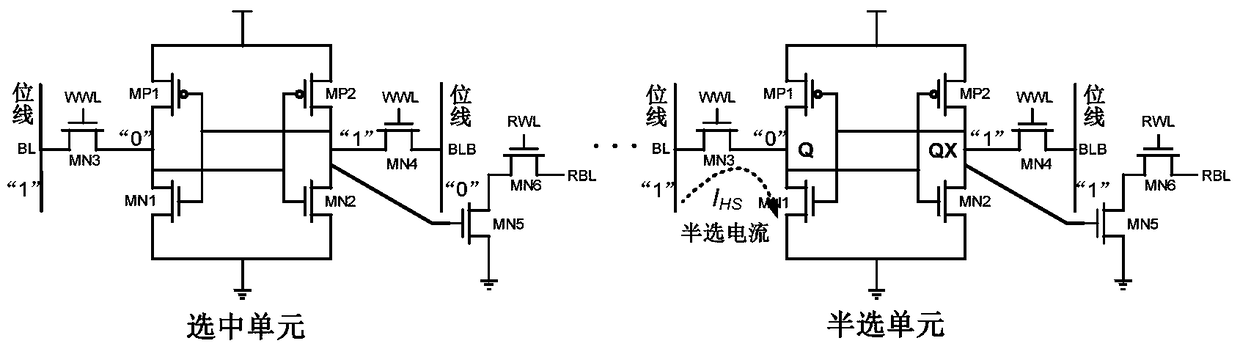

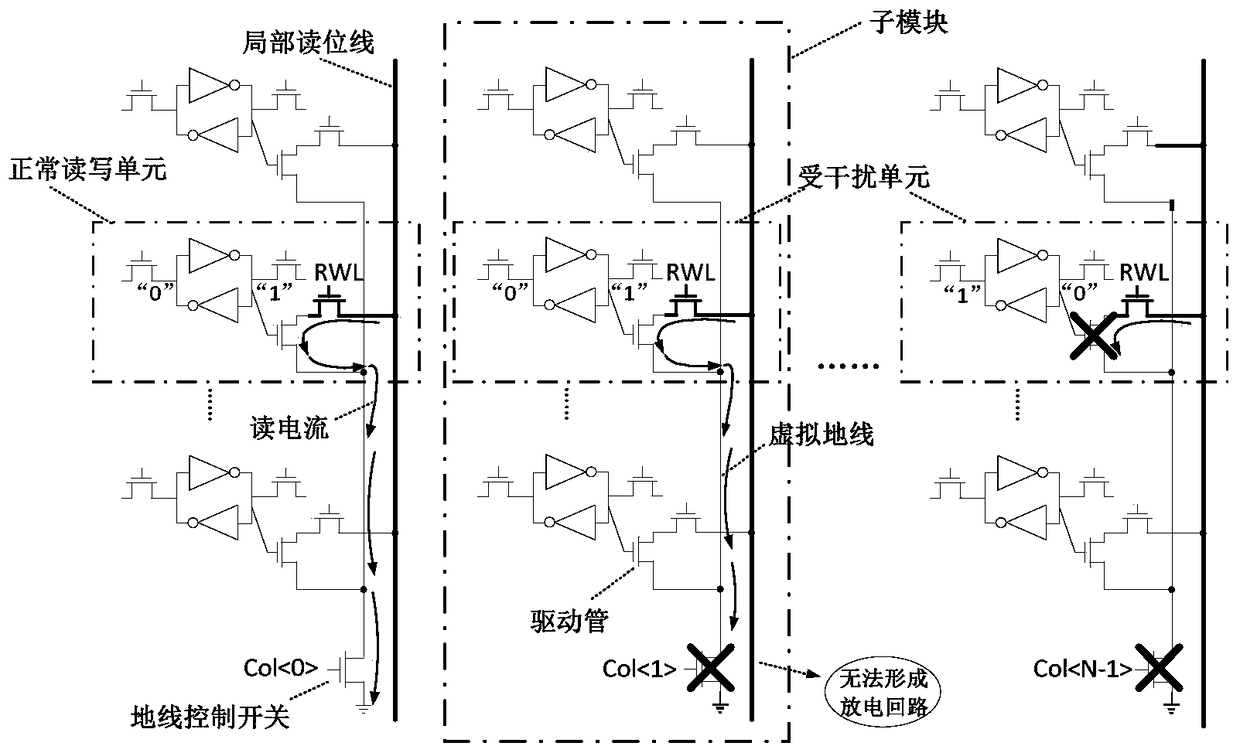

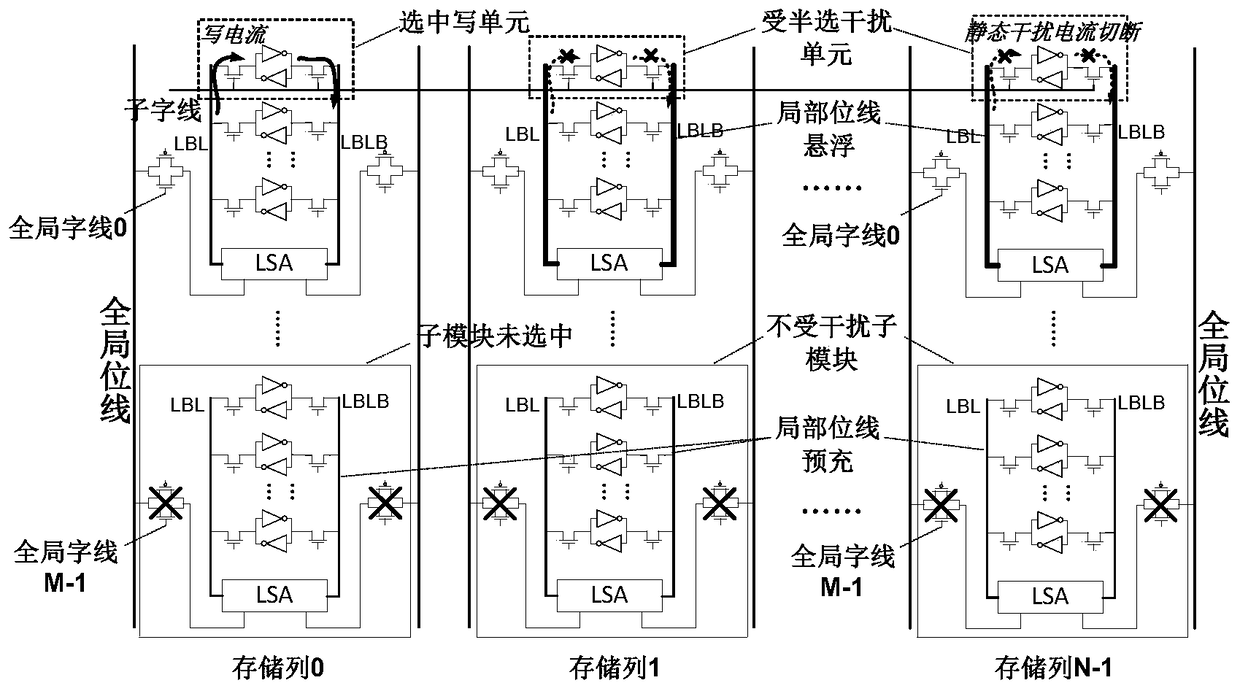

A half-selective interference cancellation structure for sram based on hierarchical bit line structure

ActiveCN105702281BReduce distractionsImprove robustnessDigital storageBit lineStatic random-access memory

Owner:XI AN JIAOTONG UNIV

A Discrete Threshold Voltage Comparator with Zero Static Power Consumption

ActiveCN107134990BEliminate Static Power ConsumptionEliminate dead timeMultiple input and output pulse circuitsVoltage regulationVoltage ratio

The invention discloses a discrete threshold value voltage comparator with zero static power consumption. The discrete threshold value voltage comparator comprises a first transistor and multiple parallel threshold value regulation branches, wherein each threshold value regulation branch is connected with the first transistor and a digital enable bit of the voltage comparator, each threshold value regulation branch controls the threshold value voltage of the voltage comparator according to the digital control signal received by the digital enable bit. In the voltage comparator, multiple parallel threshold value regulation branches are set, and the threshold value voltage is regulated according to the digital control signal received by the digital enable bit, thereby realizing the digital control of the threshold value voltage of the voltage comparator; since the voltage comparator uses the digital control threshold value voltage regulation, the static power consumption is eliminated, the zero static power consumption discrete threshold voltage comparator with adjustable threshold value voltage digital is realized, the reset operation is further avoided, and the system dead time is eliminated.

Owner:SHENZHEN UNIV

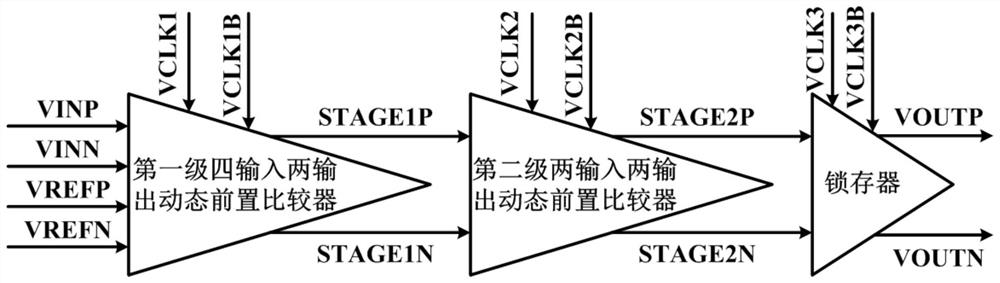

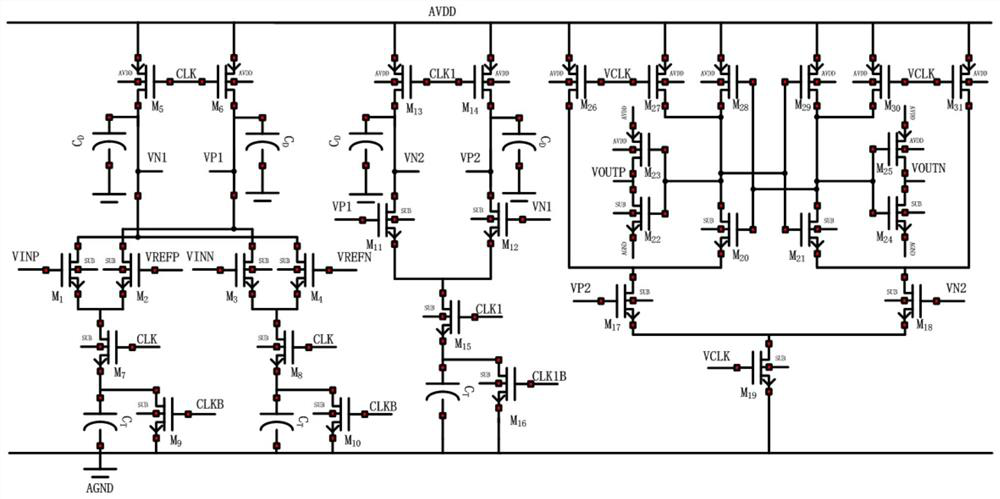

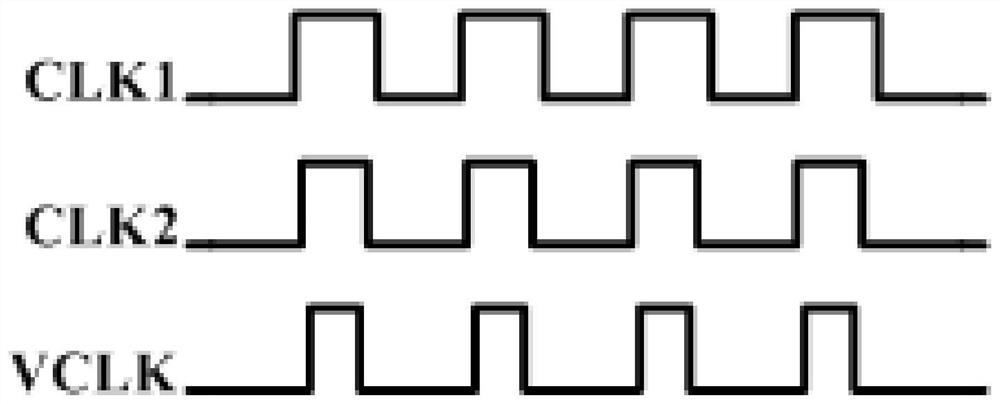

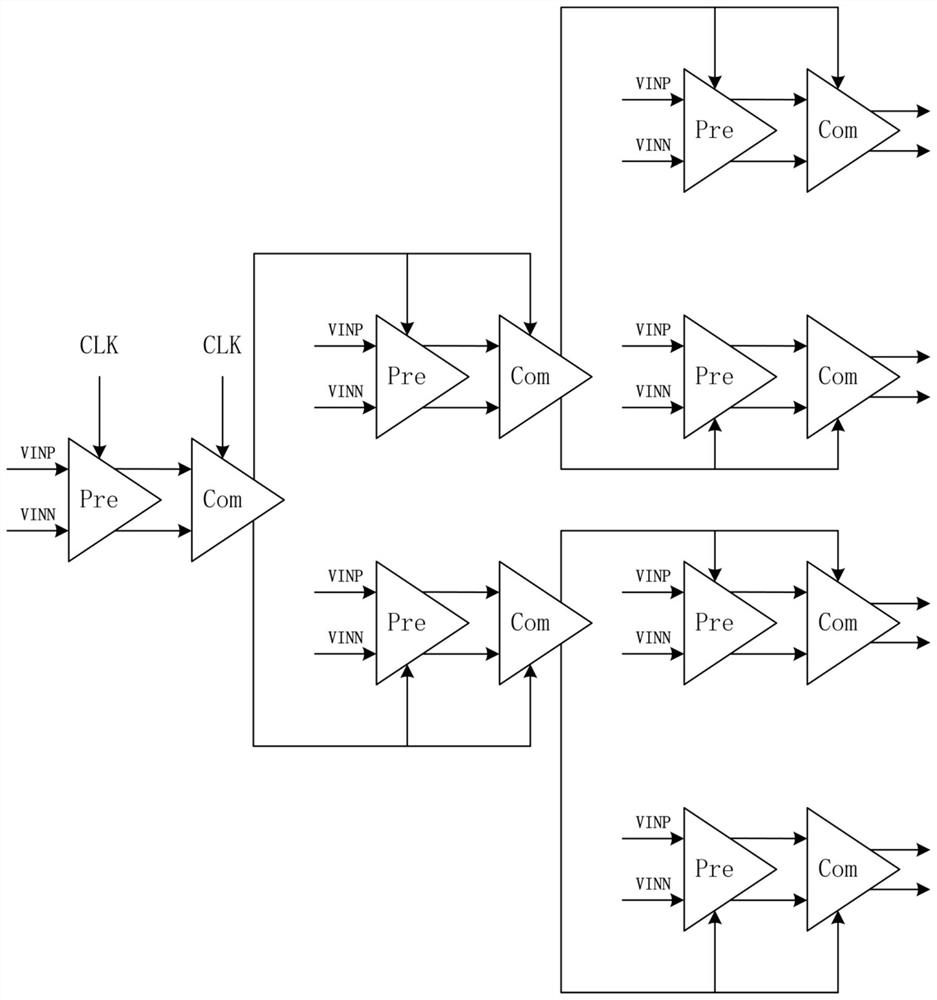

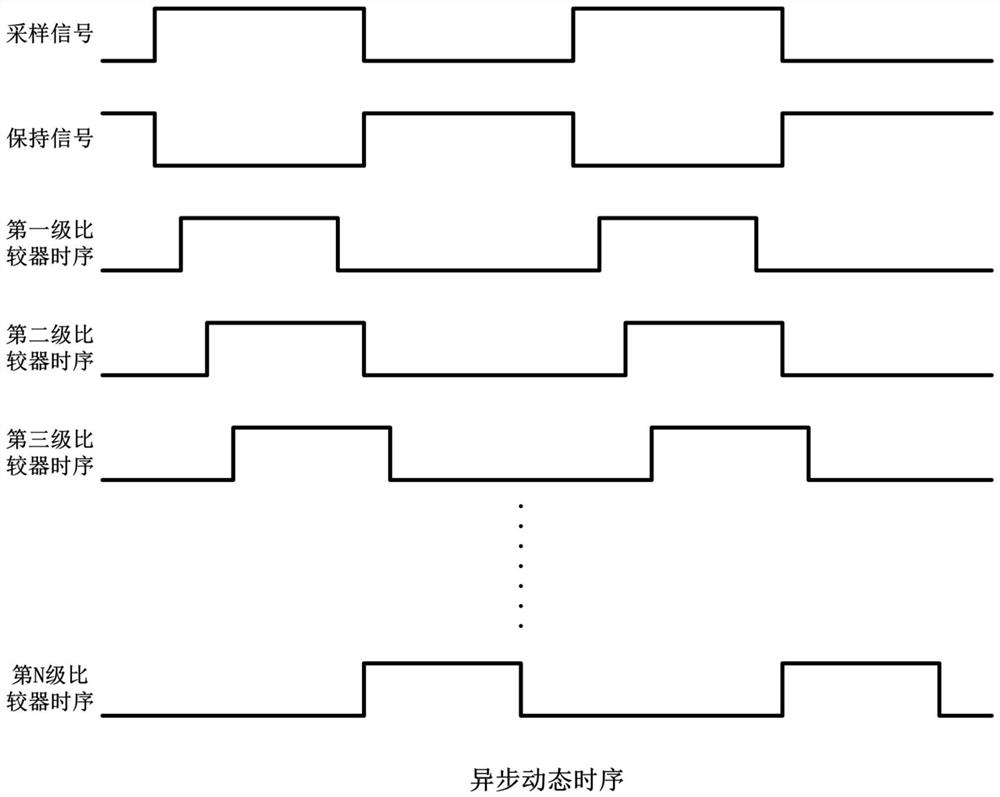

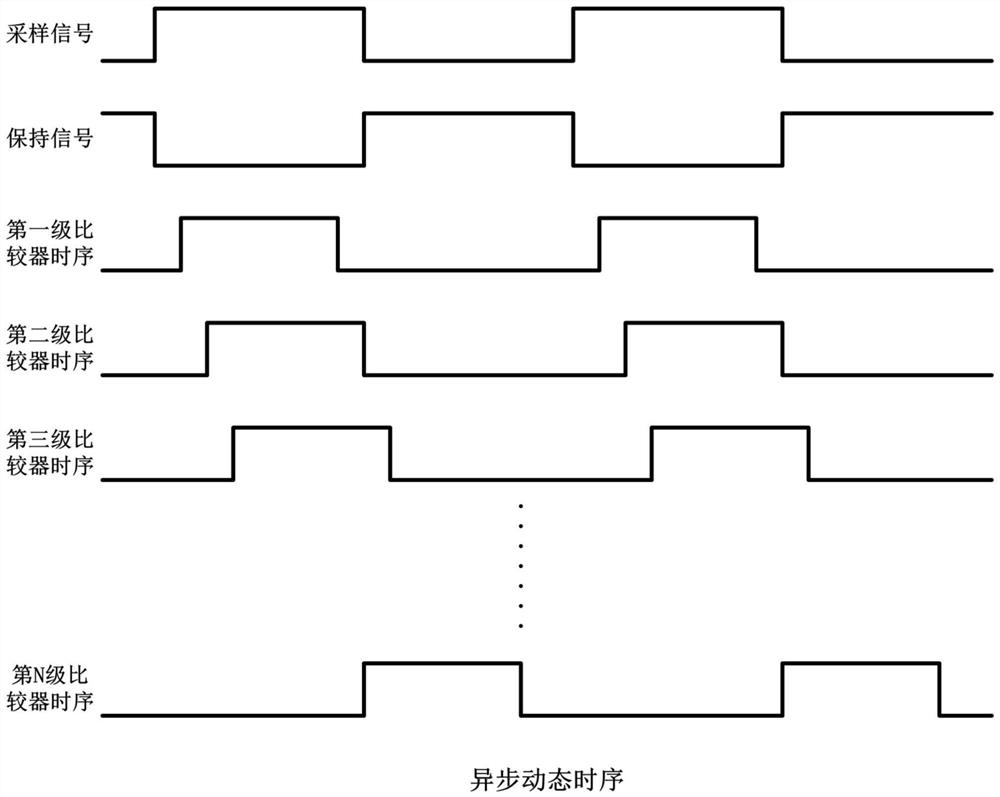

Three-stage comparator system suitable for medium-low precision high-speed low-power consumption ADC (Analog to Digital Converter)

PendingCN114679161AReduce power consumptionLower Offset VoltagePower saving provisionsElectric signal transmission systemsSoftware engineeringHemt circuits

The invention requests to protect a three-stage comparator system suitable for an ADC (Analog to Digital Converter) with medium and low precision, high speed and low power consumption, which comprises a first-stage four-input two-output dynamic small signal preamplifier, a second-stage two-input two-output dynamic small signal preamplifier and a latch, wherein the dynamic pre-amplifier comprises an input differential pair transistor, a tail charge source and a charge steering branch; the latch includes an input stage, a latch stage, and an output stage. The invention aims to improve all modules in a comparator circuit into a dynamic structure, so that the circuit is in an open-circuit state when no control time sequence is input, quiescent current is eliminated, and the power consumption is further reduced. And on the other hand, the offset voltage of the input end of the comparator is reduced through the gain multiple of the two-stage dynamic preamplifier, so that the precision of the comparator is guaranteed. The innovation point lies in that compared with a traditional architecture, the full-dynamic three-level structure has a remarkable effect of reducing the circuit power consumption and the offset voltage on the basis of the full-dynamic three-level structure.

Owner:重庆中易智芯科技有限责任公司

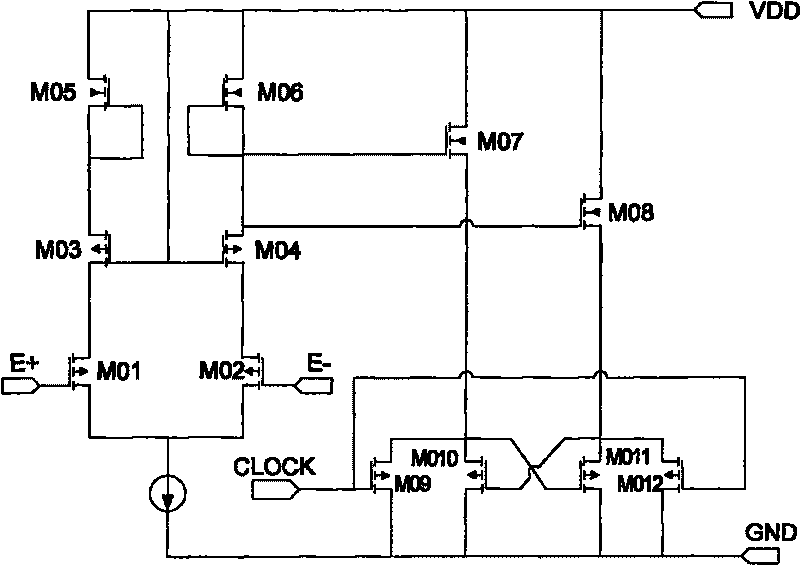

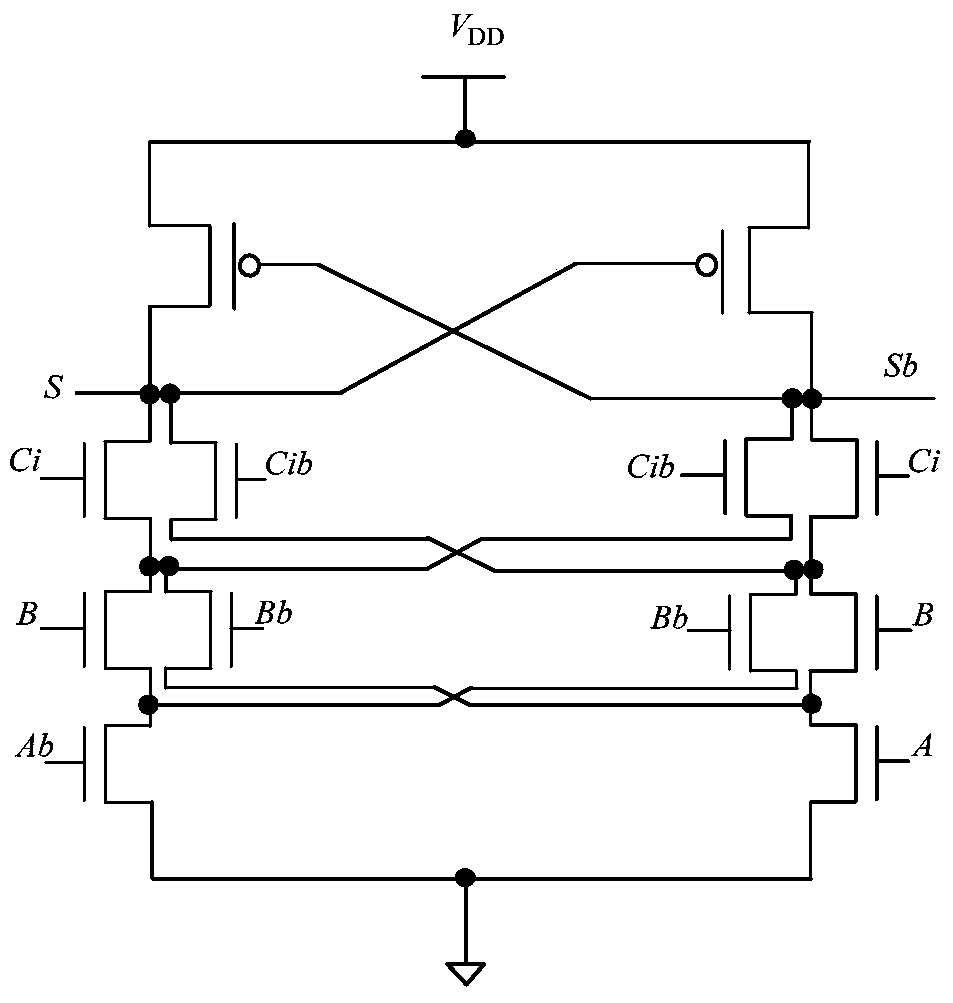

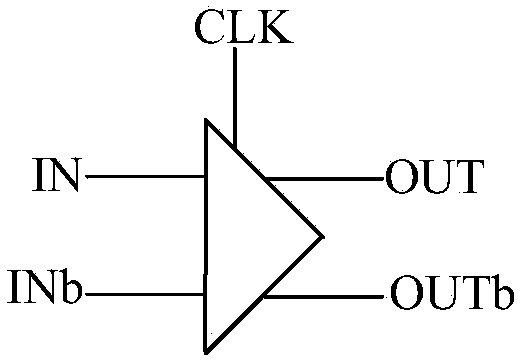

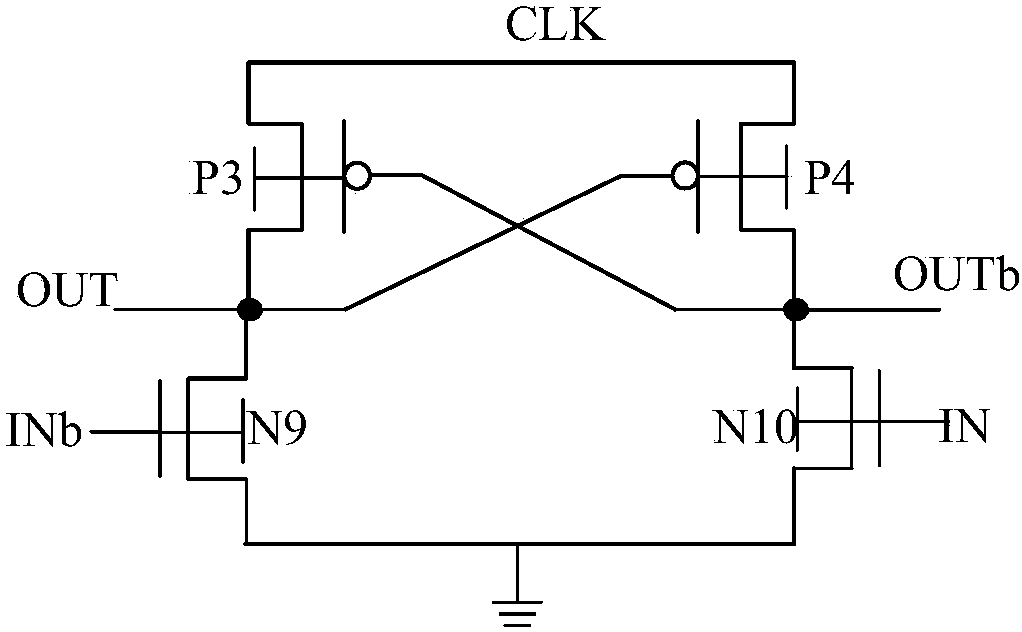

CMOS low-power consumption, low offset voltage, low return-stroke noise comparator

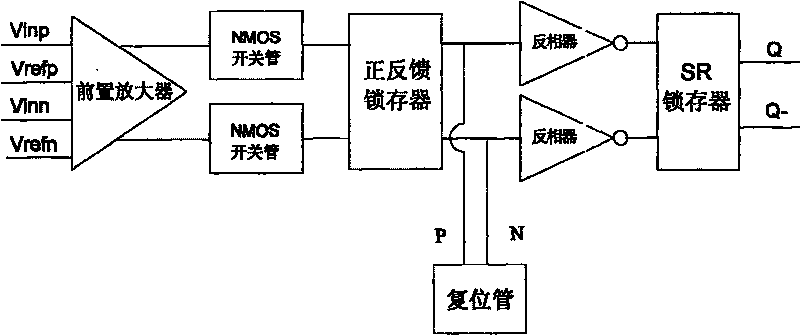

InactiveCN101355351BHigh gainLow mismatch process parametersAnalogue/digital conversionEnergy efficient ICTCmos comparatorCMOS

The invention discloses a CMOS comparator with low power consumption, low offset voltage and low return noise, belonging to the technical field of the radio communication system. The CMOS comparator comprises a preposing amplifier, a pair of switch tubes, a positive feedback latch unit, a CMOS phase inverter and an SR latch unit, wherein the preposing amplifier adopts a PMOS tube to serve as the input differential pairs, a diode is connected with an NMOS tube and is connected with a circuit structure which is in positive feedback connection with the NMOS tube in parallel to serve as the load so as to reduce the offset voltage of the comparator; the pair of the switch tubes is inserted between the preposing amplifier and the positive feedback latch unit so as to reduce the return noise of the comparator; and the positive feedback latch unit adopts a cross-coupling CMOS inverter circuit structure, a reset pipe is connected between regenerating nodes, thereby not only reducing the power consumption but also increasing the regenerating speed. The comparator has good properties of low power consumption, low offset voltage and low return noise, does not need to adopt the offset cancelingtechnique, and can be widely applied to a low power consumption high-speed AD converter with 6 to 8 medium and high accuracy of a radio communication system.

Owner:杭州中科微电子有限公司

A single-rail current modulus one-bit full adder based on finfet devices

ActiveCN106505995BReduce areaImprove stabilityLogic circuits characterised by logic functionDigital data processing detailsHemt circuitsCurrent mode

The invention discloses a single track current mode one bit full adder based on a FinFET device. The single track current mode one bit full adder comprises a bias circuit, a summation output circuit, and a carry output circuit. The summation output circuit comprises a third P-type FinFET pipe; a fourth P-type FinFET pipe and a fourth N-type FinFET pipe, which are respectively connected with the third P-type FinFET pipe; a fifth N-type FinFET pipe and a sixth N-type FinFET pipe, which are parallely connected together; a seventh N-type FinFET pipe; a ninth N-type FinFET pipe and a tenth N-type FinFET pipe, which are parallely connected together. The fourth N-type FinFET pipe is connected with the fifth N-type FinFET pipe and the sixth N-type FinFET pipe, which are parallely connected together. The seventh N-type FinFET pipe is connected with the fifth N-type FinFET pipe and the sixth N-type FinFET pipe, which are parallely connected together, and is connected with the ninth N-type FinFET pipe and the tenth N-type FinFET pipe, which are parallely connected together. By adopting a differential single track current mode structure, the N-type FinFET pipes in the pull-down network of the single track current mode adopt the parallel connection structures to realize a multi-input NOR function, and the serial connection configuration of the N-type FinFET pipes is prevented, and therefore circuit performance is optimized, and the circuit can still work normally under conditions of standard voltage and superthreshold.

Owner:宁波华盾新能源科技有限公司

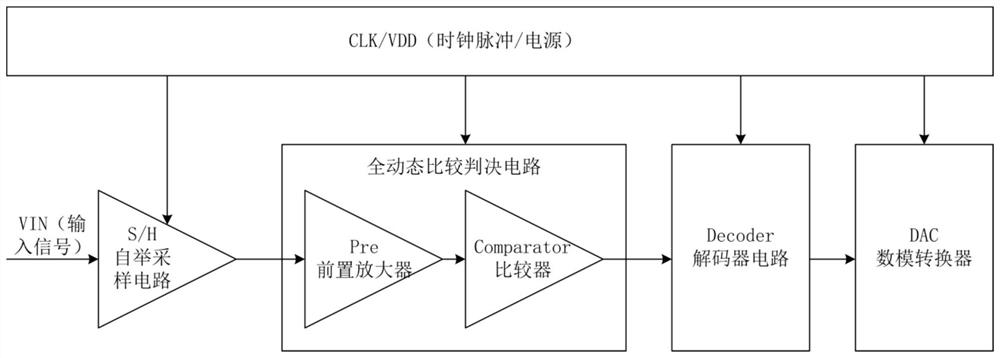

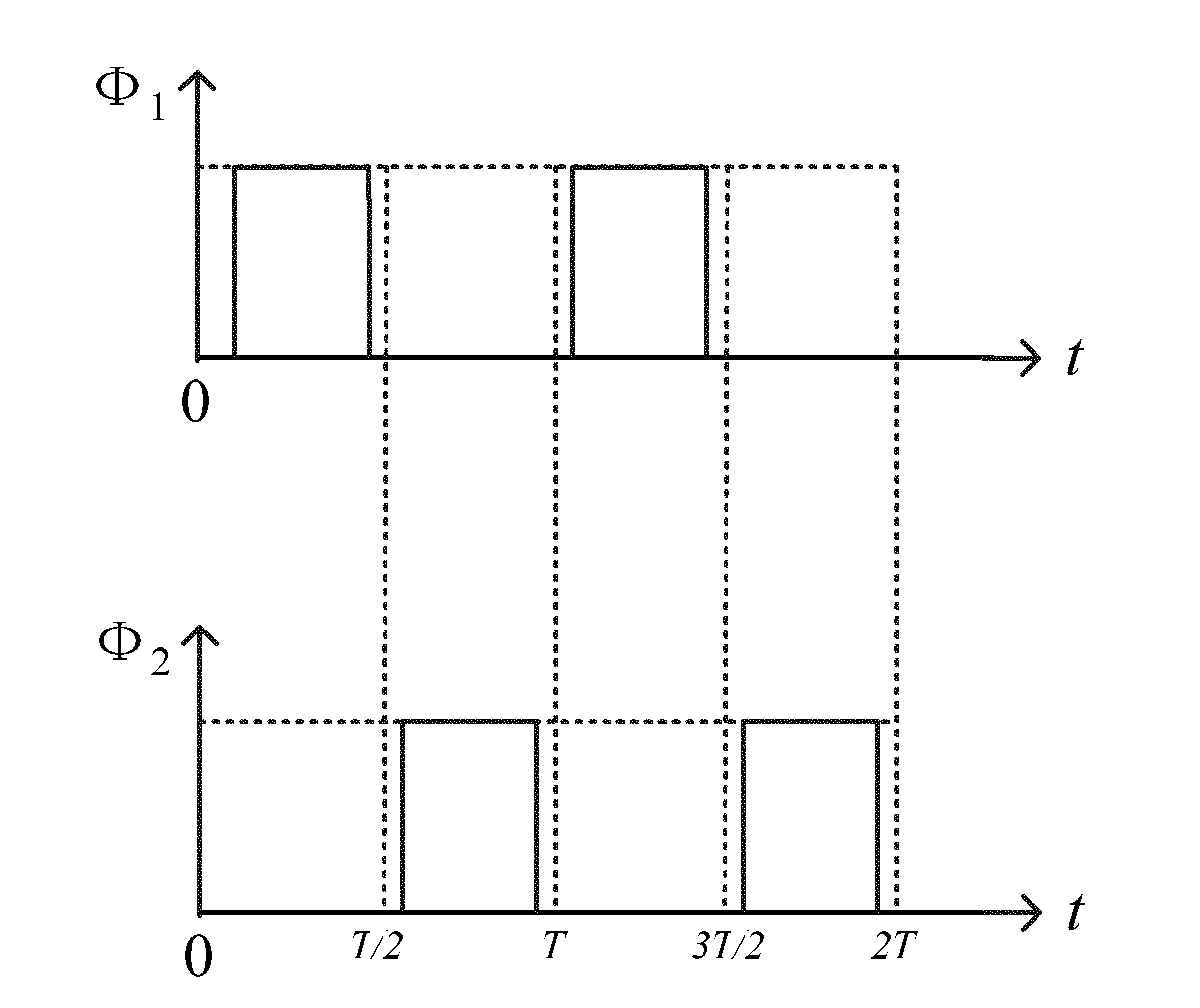

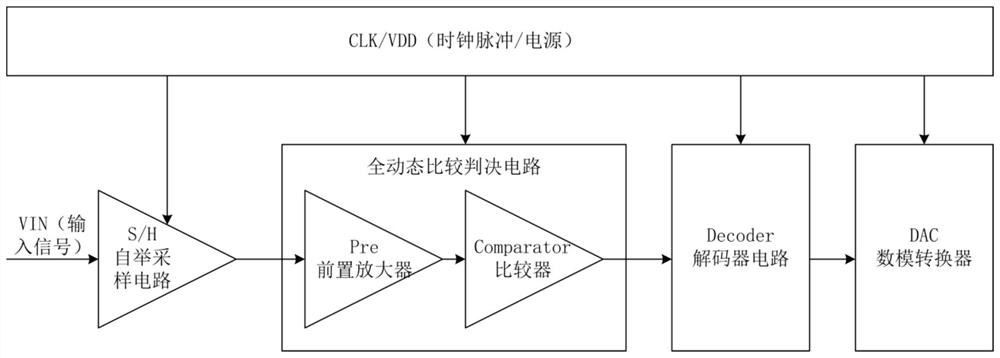

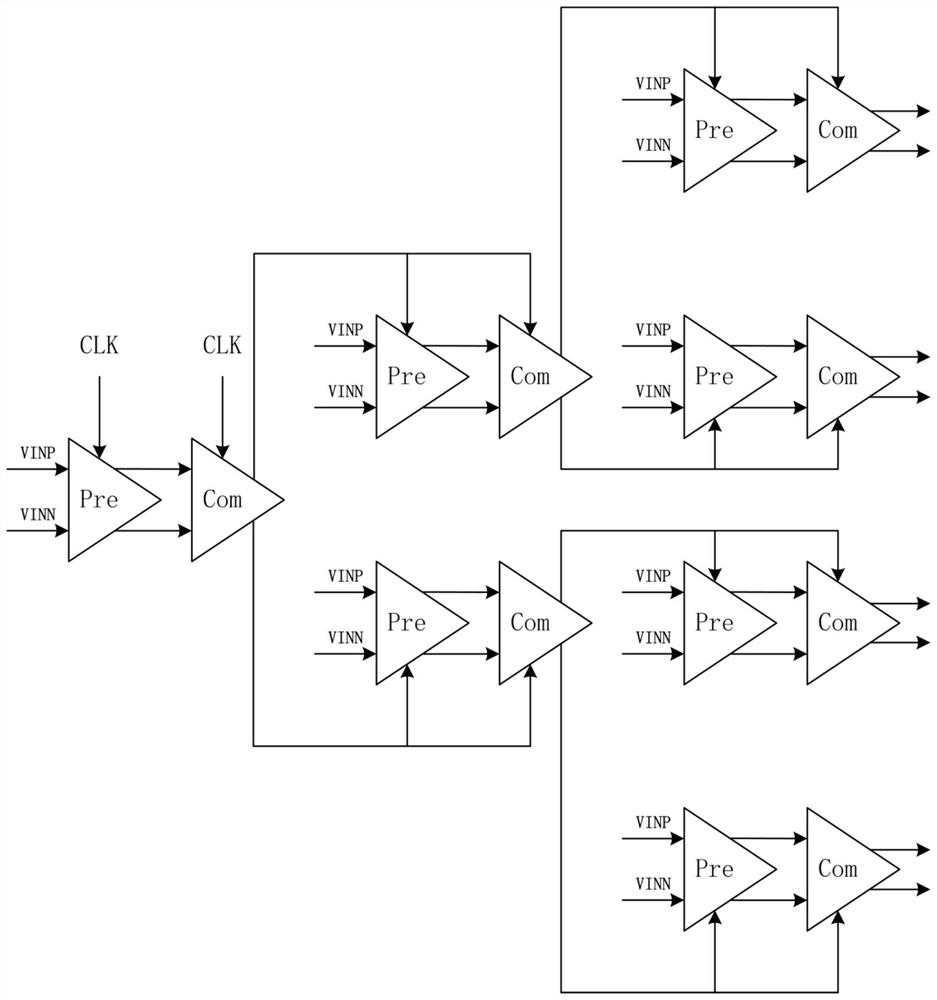

Binary-Search ADC system with low power consumption based on full-dynamic structure

ActiveCN112422130AReduce power consumptionReduced operating power consumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceHemt circuits

The invention requests to protect a low-power-consumption Binary-Search ADC system based on a full-dynamic structure. The low-power-consumption Binary-Search ADC system comprises a bootstrap samplingcircuit, a full-dynamic comparator array with a pre-amplifier and a decoder array, and the bootstrap sampling circuit comprises a charge pump circuit, a bootstrap sampling switch and a sampling capacitor; a decision array comprises a dynamic preamplifier, a dynamic comparator and a rear-end decoder array of each stage. The invention aims to enable all main modules in the circuit to be improved into a dynamic structure, the circuit does not work when no control time sequence is input, and most of time sequence signals for controlling the circuit to work are generated by the circuit structure, so that the power consumption is further reduced. The innovation point is that compared with a traditional architecture, the system has a remarkable effect of reducing the circuit power consumption based on a full-dynamic structure. According to the full-dynamic structure, the power consumption of the circuit can be reduced, the offset voltage influence of the circuit is reduced by the dynamic amplifier, and the precision is ensured.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Voltage detection circuit

ActiveCN103176020BSmall footprintHighly integratedCurrent/voltage measurementVoltage dividersCapacitanceVoltage reference

The invention discloses a voltage detection circuit which comprises a voltage divider circuit and a comparator. The voltage divider circuit includes a first capacitor and a second capacitor. A first end of the first capacitor is connected with a reference voltage, and a second end of the first capacitor is connected with a supply voltage through a first switch. A first end of the second capacitor is connected with the reference voltage through a second switch and connected with a ground potential through a third switch, and a second end of the second capacitor is the output end of the voltage divider circuit, connected with a first end of the comparator, and connected with the reference voltage through a forth switch. The second end of the first capacitor is connected with the second end of the second capacitor through a fifth switch. The voltage detection circuit can reduce the occupation space of the circuit on a chip, completely cancel the static power consumption of the circuit, thereby reducing the power consumption of the circuit, and guarantee that the high voltage dividing precision of the circuit.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

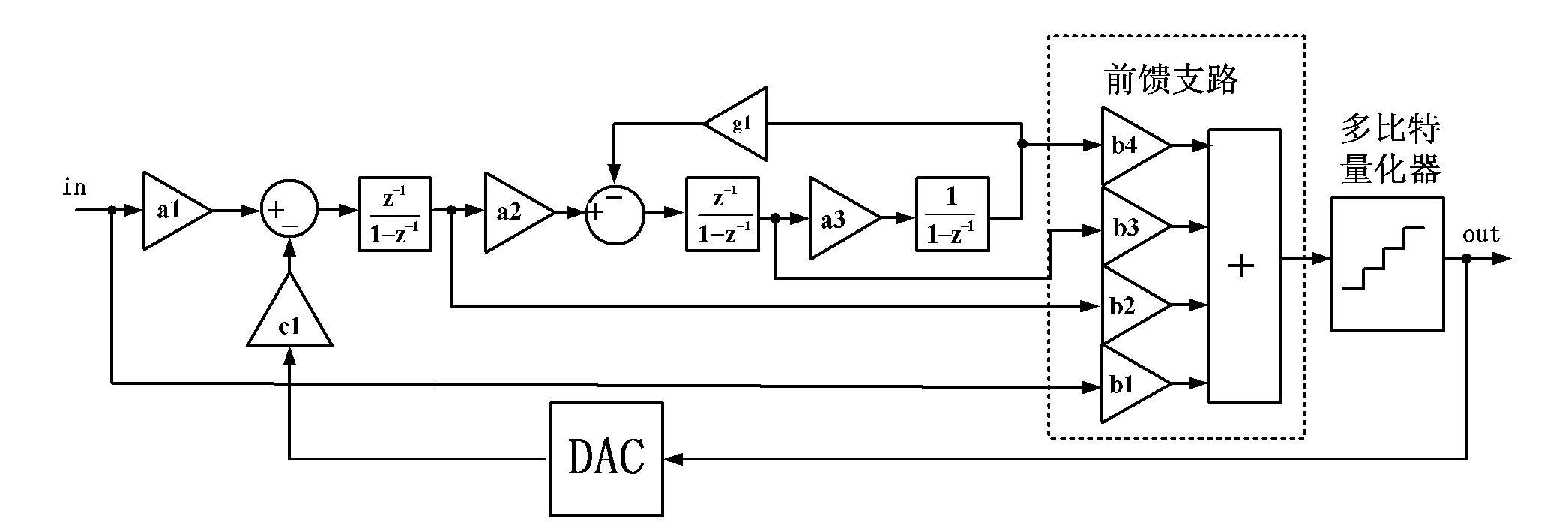

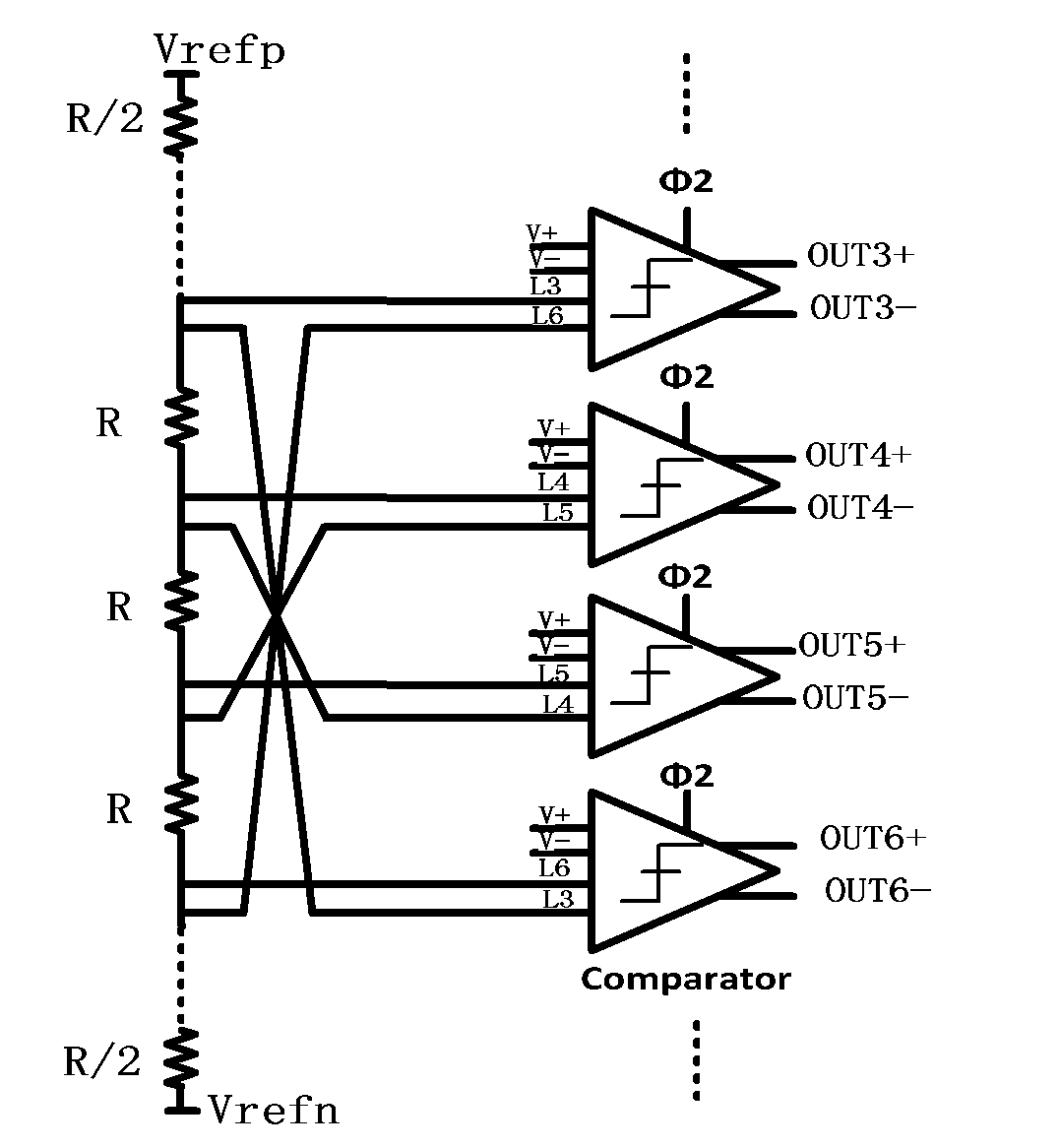

Capacitive-voltage-division-type multi-bit quantizer

ActiveCN102176675BEliminate Static Power ConsumptionIncrease capacitance densityAnalogue-digital convertersCapacitanceDividing circuits

The invention discloses a capacitive-voltage-division-type multi-bit quantizer, comprising two groups of capacitive voltage division circuits for providing reference voltage signals for dynamic comparators and a plurality of dynamic comparators for comparing the reference voltage signals with an input voltage signal and generating output voltage signals. In the capacitive-voltage-division-type multi-bit quantizer disclosed by the invention, the novel capacitive voltage division circuits are used as voltage division circuits, MOSCAP (Metal-Oxide-Semiconductor Capacitor) capacitors are used as the core devices in the voltage division circuits and the dynamic comparators are used as comparison devices, therefore the circuits of the quantizer are simplified, the static power consumption of the quantizer is basically eliminated, the total capacitance consumed by the capacitive voltage division circuits is greatly reduced, the capacitive voltage division precision is effectively improved and the area of the quantizer is prominently optimized, and the capacitive-voltage-division-type multi-bit quantizer is suitable for a miniaturized analog-to-digital converter with ultralow power consumption.

Owner:ZHEJIANG UNIV

A One-bit Full Adder Based on Finfet Device

ActiveCN105720969BLower latencyReduce the numberLogic circuits characterised by logic functionTransistorDifferential circuits

The invention discloses a one-bit full adder based on FinFET devices. The one-bit full adder comprises a sum output circuit and a carry output circuit, the sum output circuit comprises a first FinFET transistor, a second FinFET transistor, a third FinFET transistor, a fourth FinFET transistor, a fifth FinFET transistor, a sixth FinFET transistor, a seventh FinFET transistor, an eighth FinFET transistor, a ninth FinFET transistor, and a tenth FinFET transistor, and the carry output circuit comprises an eleventh FinFET transistor, a twelfth FinFET transistor, a thirteenth FinFET transistor, a fourteenth FinFET transistor, a fifteenth FinFET transistor, a sixteenth FinFET transistor, a seventeenth FinFET transistor, and an eighteenth FinFET transistor. The one-bit full adder is advantageous in that the sum output circuit and the carry output circuit both employs the differential circuits, sum output and carry output are realized via alternative work, and the one-bit adder works in a differential manner so that the static power consumption of the circuits can be completely eliminated; besides, opposite logic output is realized, an extra inverter is not needed for opposite logic so that the number of the transistors is further reduced, the circuit area is small, the time delay is short, the power consumption is low, and the consumption-delay product is small.

Owner:NINGBO UNIV

Reconfigurable operator, integrated circuit and method for reducing power consumption of reconfigurable operator

InactiveCN102184274BReduce jump rateEliminate Static Power ConsumptionSpecial data processing applicationsSpecific functionComputer module

The invention discloses a reconfigurable operator, which comprises a power consumption control module, wherein the power consumption control module is used for controlling the power consumption of the reconfigurable operator; and the power consumption control module can control the power supply situation of the reconfigurable operator when a functional unit of the reconfigurable operator does notrealize any specific function, or control output data according to the continuity of data processing of the reconfigurable operator when the reconfigurable operator realizes some specific function soas to fulfill the aim of reducing the power consumption. The invention also discloses an integrated circuit which comprises the reconfigurable operator. The invention also discloses a method for reducing the power consumption of the reconfigurable operator according to a principle of controlling the power consumption by the reconfigurable operator.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

A Discrete Threshold Voltage Comparator with Zero Static Power Consumption

ActiveCN107196629BEliminate Static Power ConsumptionEliminate dead timeMultiple input and output pulse circuitsAnalogue-digital convertersVoltage regulationEngineering

The invention discloses a discrete threshold voltage comparator with zero static power consumption. The discrete threshold voltage comparator comprises a first transistor and a plurality of parallel threshold value adjustment branches, wherein each threshold value adjustment branch is connected with the first transistor and a digital enable bit of the voltage comparator, and each threshold value adjustment branch adjusts a threshold voltage of the voltage comparator according to a digital control signal received by the digital enable bit. According to the discrete threshold voltage comparator , the plurality of parallel threshold value adjustment branches are arranged in the voltage comparator, and the threshold voltage of the voltage comparator is adjusted based on the digital control signal received by the digital enable bit, thus the digital control of the threshold voltage of the voltage comparator is realized; and since the voltage comparator utilizes digital control for adjusting the threshold voltage, the threshold voltage is eliminated, the discrete threshold voltage comparator with zero static power consumption and adjustable threshold voltage values is implemented, reset operation is avoided and the system dead time is eliminated.

Owner:SHENZHEN UNIV

Continuous third-order sigma-delta modulator circuit based on active resistor-capacitor integrator

ActiveCN106849953BImprove linearityEliminate Static Power ConsumptionAnalogue conversionCapacitanceIntegrator

Owner:XIDIAN UNIV

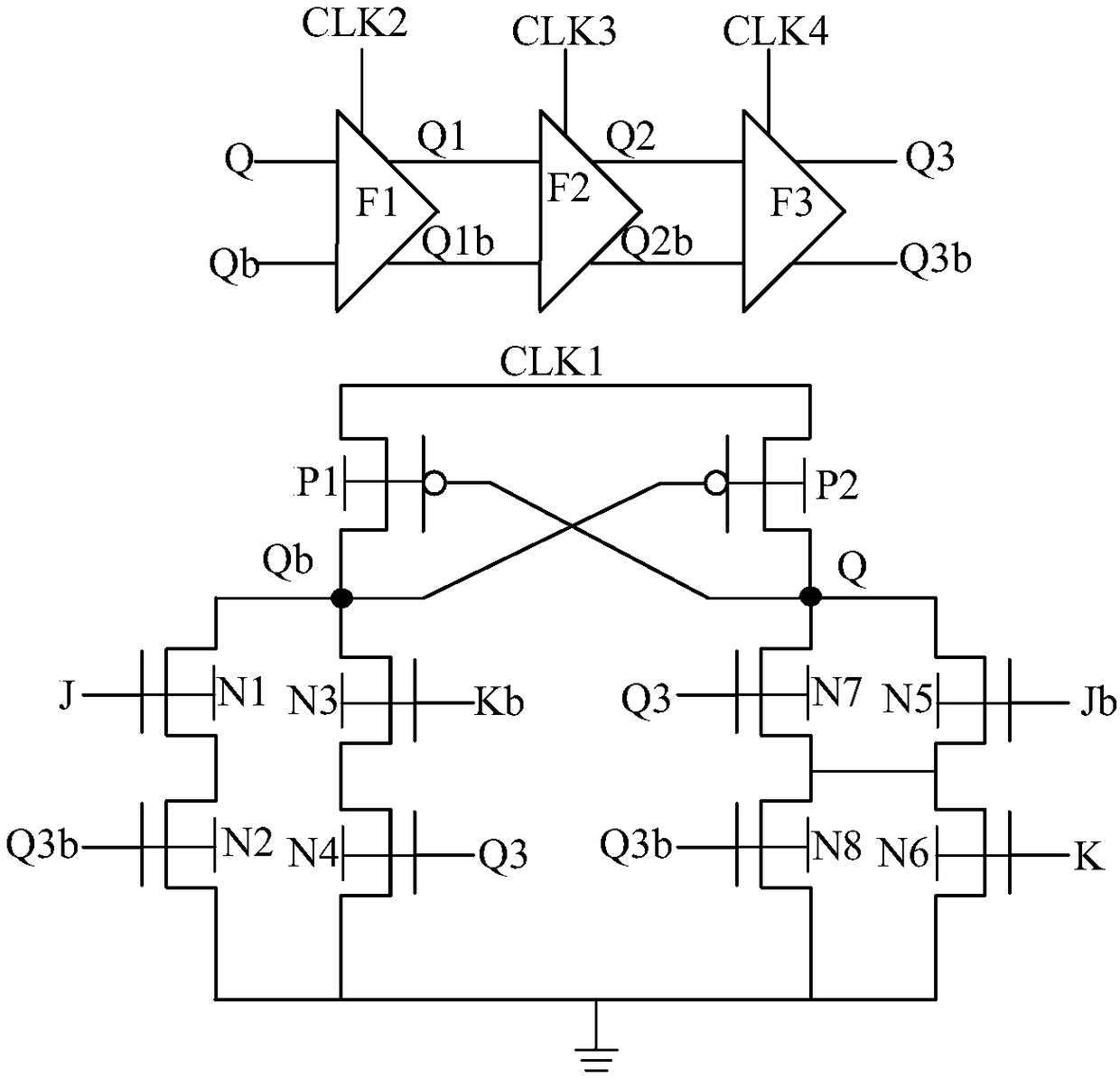

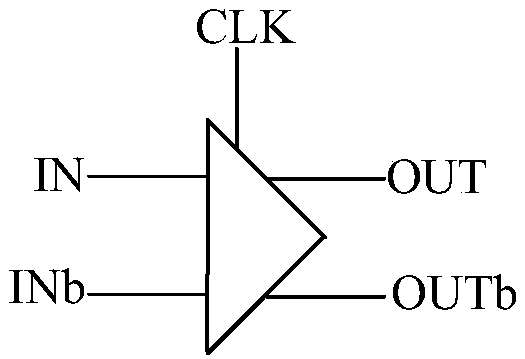

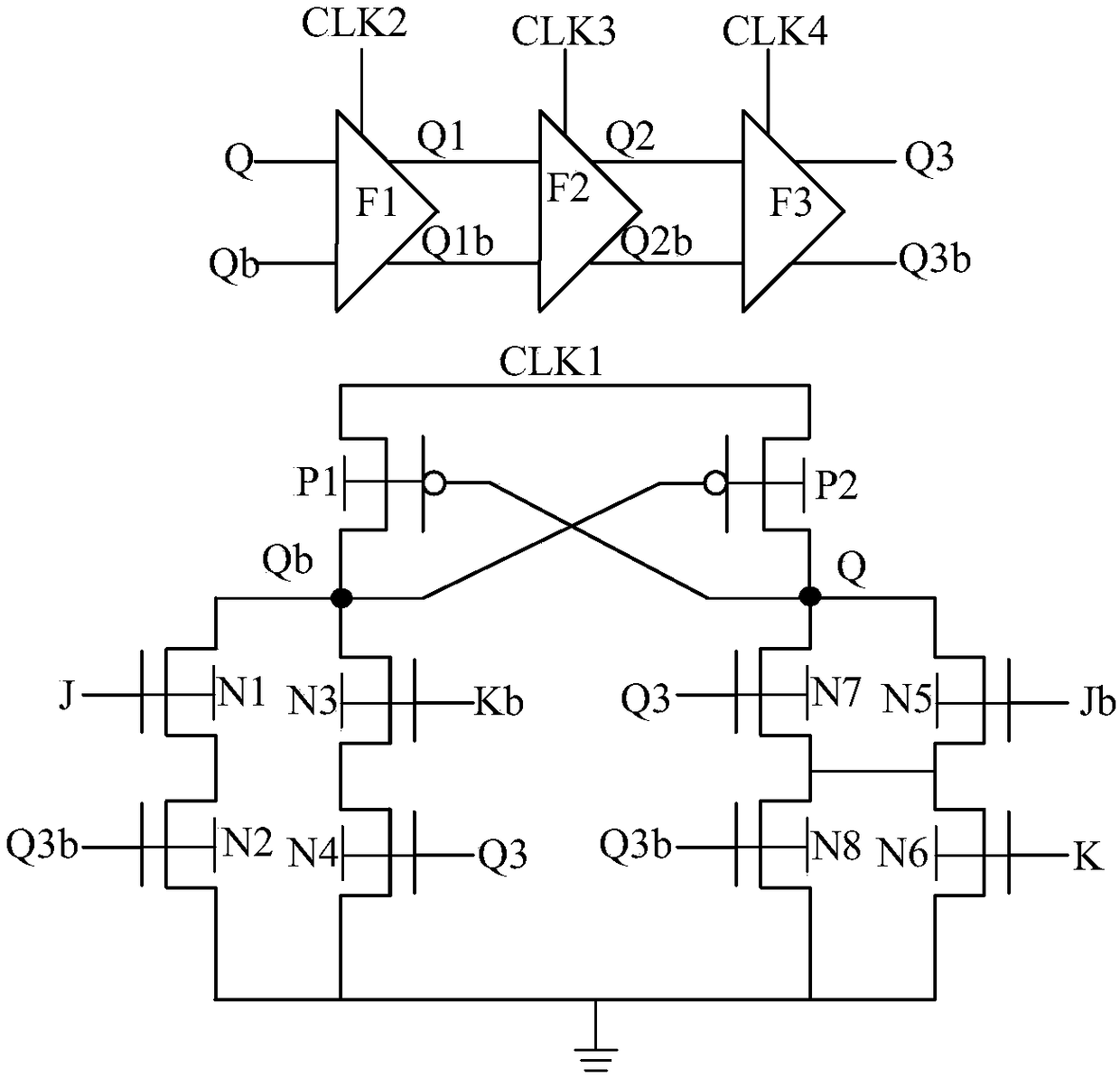

An adiabatic pal-2n jk flip-flop based on finfet device

ActiveCN105978534BEasy to chargeEasy to recycleElectric pulse generatorEngineeringPower–delay product

The invention discloses an adiabatic PAL-2N structure type JK flip-flop based on Fin-FET devices, comprising a first P-type Fin-FET, a second P-type Fin-FET, a third P-type Fin-FET, a fourth P-type Fin-FET, a first N-type Fin-FET, a second N-type Fin-FET, a third N-type Fin-FET, a fourth N-type Fin-FET, a fifth N-type Fin-FET, a sixth N-type Fin-FET, a seventh N-type Fin-FET, an eighth N-type Fin-FET, a ninth N-type Fin-FET, a tenth N-type Fin-FET and an eleventh N-type Fin-FET. The advantage is that under the condition that the circuit performance of the adiabatic PAL-2N structure type JK flip-flop is not affected, the number of Fin-FETs is reduced, the circuit area is reduced significantly, and the time delay, power consumption and power-delay product are reduced significantly.

Owner:NINGBO UNIV

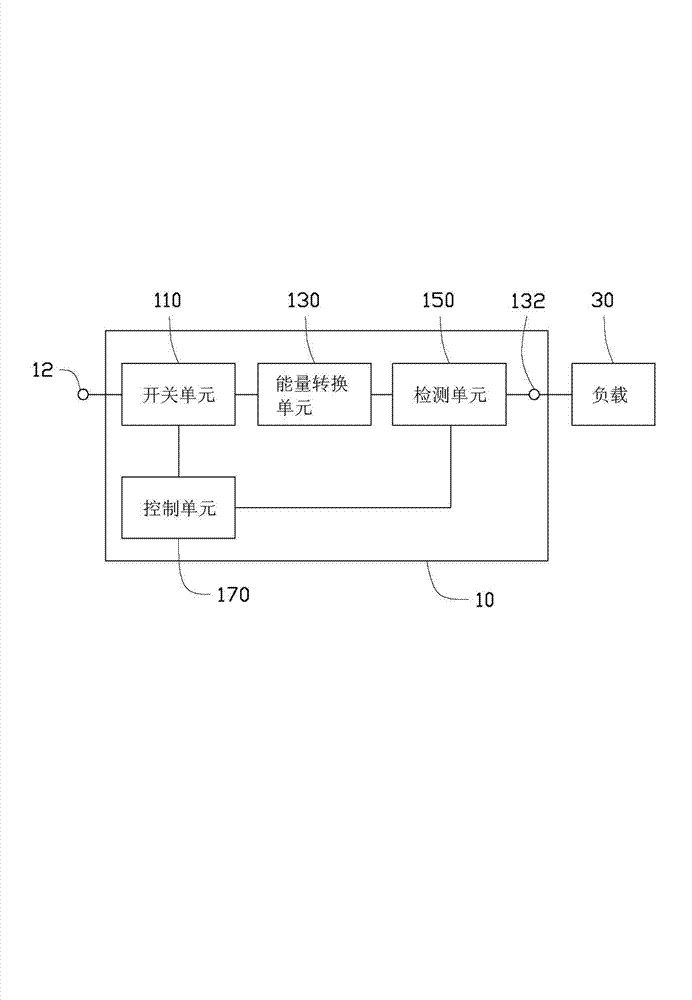

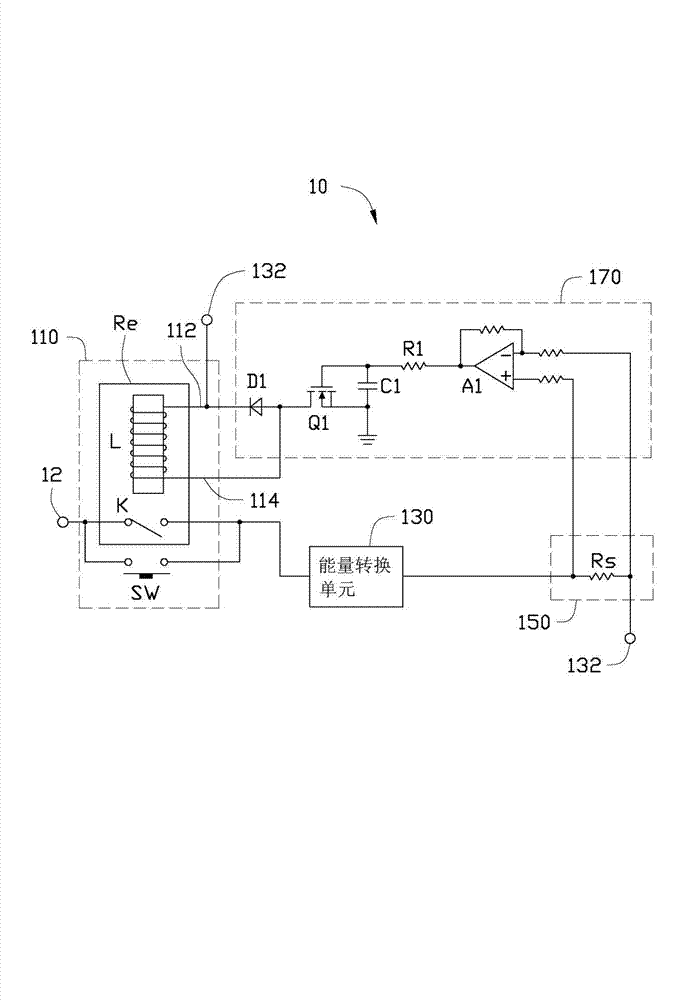

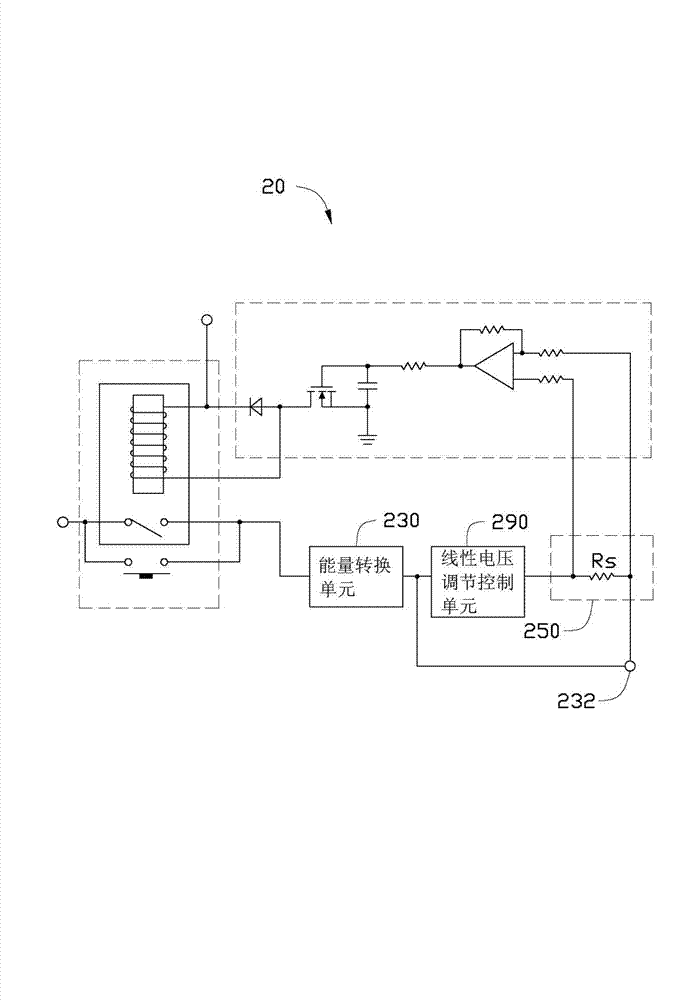

Power-supplying circuit

InactiveCN103095115AEliminate Static Power ConsumptionSave electricityBatteries circuit arrangementsEfficient power electronics conversionEngineeringControl unit

The invention provides a power-supplying circuit which comprises a switch unit, an energy conversion unit, a detection unit, a control unit and an output end. The switch unit is connected between an external power supply and the energy conversion unit, the energy conversion unit converts the external power supply into an input a load needs and outputs the input through an output end, the detection unit is connected between the energy conversion unit and the output end in series, and the detection unit detects the output current of the output end. The control unit is connected between the detection unit and the switch unit. When the detection unit detects that no current is outputted from the output end or current is very small, the control unit enables the switch unit to be cut off according to the detection signals provided by the detection unit.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

A low-power binary-search ADC system based on full dynamic structure

ActiveCN112422130BLower Offset VoltageReduce power consumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceHemt circuits

The present invention claims to protect a low-power Binary-Search ADC system based on a full dynamic structure, which includes a bootstrap sampling circuit, a full dynamic comparator array with a preamplifier and a decoder array, wherein the bootstrap sampling circuit includes a charge pump circuit, bootstrap sampling switch and sampling capacitor; decision array includes dynamic preamplifier, dynamic comparator and back end decoder array for each stage. The purpose of the present invention is to improve all the main modules in the circuit into a dynamic structure, when there is no control timing input, the circuit does not work, and most of the timing signals for the control circuit operation are generated by the circuit structure itself, so that the power consumption can be further improved. reduce. The innovation is that compared with the traditional structure, the present invention has a significant effect on reducing the power consumption of the circuit based on the full dynamic structure. The full dynamic structure of the present invention can not only reduce the power consumption of the circuit, but also reduce the influence of the offset voltage of the circuit by the dynamic amplifier and ensure the accuracy.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

An adiabatic ecrl structure type jk flip-flop based on finfet device

ActiveCN105958969BEasy to chargeEasy to recycleElectric pulse generatorStructure typeCircuit performance

The invention discloses a thermally-insulated ECRL structural JK trigger based on Fin FET devices. The thermally-insulated ECRL structural JK trigger comprises a first P-type Fin FET, a second P-type Fin FET, and first to thirteenth N-type Fin FETs. While not influencing circuit performance, the thermally-insulated ECRL structural JK trigger is decreased in the number of the Fin FETs and is significantly reduced iin circuit area, time delay, power consumption and power consumption time delay product.

Owner:NINGBO UNIV