A single-rail current modulus one-bit full adder based on finfet devices

A technology of current mode and full adder, which is applied to logic circuits with logic functions, instruments, and electrical digital data processing, etc. It can solve problems such as circuit logic errors, achieve the effects of increasing stability, simplifying circuits, and avoiding series configuration.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The preferred embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

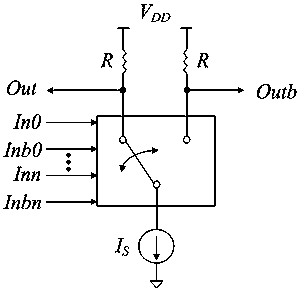

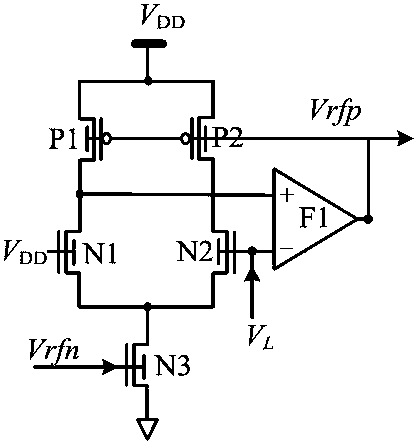

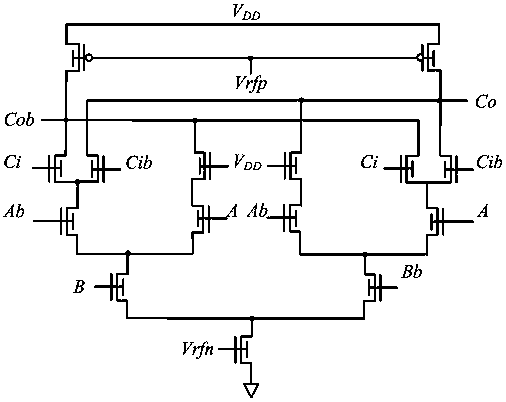

[0029] see figure 2 , shown in Fig. 4 (a) and Fig. 4 (b), it is the circuit of a kind of bias circuit, summation output circuit and carry output circuit of a kind of single-rail current modulus one-bit full adder based on FinFET device of the embodiment of the present invention Schematic diagram, the bias circuit controls the voltage swing, the source of the first P-type FinFET P1, the back gate of the first P-type FinFET P1, the source of the second P-type FinFET P2, the second P-type FinFET The back gate of P2 and the front gate of the first N-type FinFET tube N1 are connected to the power supply voltage VDD, the back gate of the first N-type FinFET tube N1, the back gate of the second N-type FinFET tube N2, and the third N-type FinFET tube The source of N3 and the back gate of the third N-type FinFET transistor N3 are grounded, and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More