A cmos addition unit

An addition unit, the eleventh technology, applied in the field of CMOS addition units, can solve problems such as circuit performance deterioration, circuit consumption, and multi-energy consumption, and achieve the effects of eliminating leakage, speeding up operation, and improving circuit speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

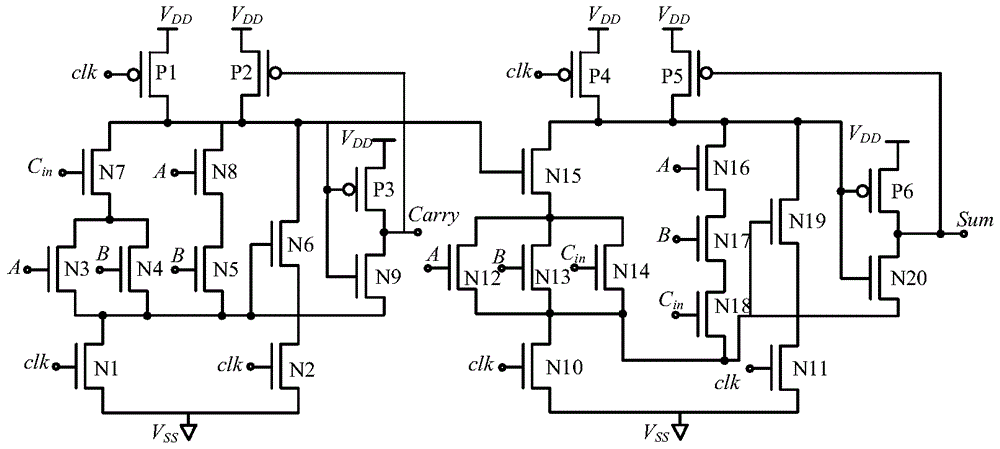

[0017] Example: such as figure 1 As shown, a CMOS addition unit includes a first PMOS transistor P1, a second PMOS transistor P2, a third PMOS transistor P3, a fourth PMOS transistor P4, a fifth PMOS transistor P5, a sixth PMOS transistor P6, a first NMOS transistor N1, the second NMOS transistor N2, the third NMOS transistor N3, the fourth NMOS transistor N4, the fifth NMOS transistor N5, the sixth NMOS transistor N6, the seventh NMOS transistor N7, the eighth NMOS transistor N8, the ninth NMOS transistor N9, The tenth NMOS tube N10, the eleventh NMOS tube N11, the twelfth NMOS tube N12, the thirteenth NMOS tube N13, the fourteenth NMOS tube N14, the fifteenth NMOS tube N15, the sixteenth NMOS tube N16, the tenth The seventh NMOS transistor N17, the eighteenth NMOS transistor N18, the nineteenth NMOS transistor N19, and the twentieth NMOS transistor N20, the source of the first PMOS transistor P1, the source of the second PMOS transistor P2, and the third PMOS transistor P3 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More